国際特許分類[H01L21/3205]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286)

国際特許分類[H01L21/3205]の下位に属する分類

後処理 (649)

国際特許分類[H01L21/3205]に分類される特許

1,011 - 1,020 / 6,637

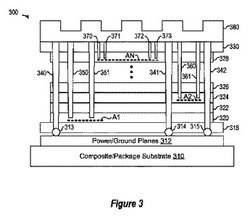

プロセス均一性及び熱消散を改善するダミーTSV(スルーシリコンビア)

【解決手段】

各々が能動回路領域を含むチップの積層体において、多重チップ積層体内の複数のスルーシリコンビア(TSV)開口をパターニングし、エッチングし、そして熱的伝導性材料で充填することによって、多重チップ積層体からの熱を熱的に伝導させるための複数のTSV構造が形成され、複数のTSV開口は、いずれの能動回路領域をも貫通せずに多重チップ積層体の実質的に全体を通って延びる第1の大きなTSV開口と、能動回路領域まで下に延びるが通過はしない第2の小さい開口と、を含む。

(もっと読む)

ダマシン処理によるサイドウォールポリマー用の洗浄溶液

【解決手段】ウエハ上の低誘電率材料及び相互接続材料に損傷を与えることなく、ウエハ上のダマシン処理によるサイドウォールポリマーを除去するための水性洗浄溶液及び洗浄溶液を用いる方法を記載する。 (もっと読む)

成膜方法、プログラム及びコンピュータ記憶媒体

【課題】基板の所定の位置に高い位置精度で膜を形成する。

【解決手段】電極形成用テンプレート112の表面112aには、ウェハWの貫通孔に対応する位置に開口部115が複数形成されている。電極形成用テンプレート112は、開口部115に連通する膜形成用液の流通路116を備えている。この電極形成用テンプレート112とウェハWを密着させた後、この状態のまま、めっき液供給口117から流通路116を介して開口部115からウェハWの貫通孔に対してめっき液を供給することで、ウェハWの貫通孔に電極を形成する。

(もっと読む)

半導体処理システムのための前駆物質を生成する方法及び装置

【課題】半導体処理システム(320)の前駆物質を生成する装置を提供する。

【解決手段】装置は、側壁(402)、上部、底部を有するキャニスタ(300)を含んでいる。キャニスタ(300)は、上の領域(418)と下の領域(434)を有する内容積(438)を画成している。一実施形態においては、装置は、更に、キャニスタ(300)を部分的に取り囲んでいるヒータ(430)を含んでいる。ヒータ(430)によって、上の領域(418)と下の領域(434)間に温度勾配が生じる。また、精製ペンタキス(ジメチルアミド)タンタルから原子層堆積によってバリヤ層、例えば、窒化タンタルバリヤ層を形成する方法も特許請求される。

(もっと読む)

貫通電極、微小構造体及びそれらの製造方法

【課題】短時間で製造することができ、十分な気密性を有するとともに、基板の反りを低減させることができる貫通電極、微小構造体及びそれらの製造方法を提供する。

【解決手段】導電性を有する基板10の所定領域を貫通トレンチ21で囲み、貫通トレンチ21内に絶縁膜50を形成して周囲から絶縁分離した貫通電極60において、絶縁膜50は、貫通トレンチ21の側面から化学気相成長させたシリコン膜40を熱酸化したシリコン熱酸化膜50である。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置の信頼性を向上させる。

【解決手段】半導体基板1は、素子形成面である第1の面1a及びその反対側の第2の面1bを有する。第1の面1aから第2の面1bまで半導体基板1を貫通するように貫通孔20が形成されている。貫通孔20の内壁上に絶縁膜21及びバリア膜22が順次形成されている。絶縁膜21及びバリア膜22が形成された貫通孔20が埋まるように導電部23が形成されている。貫通孔20の周辺に位置する部分の半導体基板1における少なくとも第1の面1a側にゲッタリングサイト30が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の微細化に対処しうる、製造が容易で安価な低コンタクト抵抗の半導体装置およびその製造方法を得る。

【解決手段】Si基板(1)上の不純物領域(7)を覆うように層間絶縁膜(8)が形成され、その層間絶縁膜(8)には、層間絶縁膜(8)を貫通して不純物領域(7)を掘り込むようにコンタクトホール(9)が形成されている。コンタクトホール(9)内には、金属膜(10)、バリア層(11)、金属シリサイド(12)およびソース、ドレイン配線(14)が形成されている。ソース、ドレイン配線(14)は、タングステンから形成されている。

(もっと読む)

半導体装置

【課題】 パッド内での過度の電流集中を抑制することが可能なパッド構造を有する半導体装置を提供する。

【解決手段】 半導体基板の上に、絶縁性材料からなる第1の絶縁膜が形成されている。第1の絶縁膜の上に、導電材料からなるパッド部が形成されている。パッド部に電気的に連続し、第1の幅W1を有する配線部が形成されている。第1の絶縁膜の上であって、パッド部の外周線から第2の幅W2より内側の第1の領域に、複数の第2の絶縁膜が配置されている。配線部とパッド部との境界線に最も近い第2の絶縁膜を連ねる直線のうち、配線部をパッド部内に延長した領域と重なる部分が、パッド部の導電材料と交差する長さをL3としたとき、W1≦2×W2+L3を満たす。

(もっと読む)

半導体集積回路装置

【課題】フリップチップ構造を有する半導体集積回路装置において、パッドからチップ内部素子へ加わる応力の影響に起因するタイミング信頼性の劣化を低コストで防止する。

【解決手段】フリップチップ構造を有する半導体集積回路装置において、応力の影響を受ける半導体チップ101の外周列におけるパッド102の構造及び配置位置等について、応力の影響に起因するLSIの動作不具合が発生しにくいように予めレイアウトする。

(もっと読む)

成膜方法、半導体装置の製造方法及び半導体装置

【課題】表面の平坦性の優れたシリコン膜を形成する成膜方法、半導体装置の製造方法及び半導体装置を提供する。

【解決手段】基体上にジシラン及びトリシランの少なくともいずれかを用いて第1温度で第1膜を形成する第1膜形成工程と、前記基体及び前記第1膜を、水素を含む雰囲気中において、前記第1温度から、前記第1温度よりも高い第2温度に向けて昇温する昇温工程と、前記昇温の後に、前記第1膜の上に、シランを用いて前記第2温度で第2膜を形成する第2膜形成工程と、を備えたことを特徴とする成膜方法が提供される。

(もっと読む)

1,011 - 1,020 / 6,637

[ Back to top ]