国際特許分類[H01L21/3205]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286)

国際特許分類[H01L21/3205]の下位に属する分類

後処理 (649)

国際特許分類[H01L21/3205]に分類される特許

1,021 - 1,030 / 6,637

半導体装置および配線用マスク判別方法

【課題】使用した配線用マスクを簡単かつ確実に判別でき、確認工数を削減する。

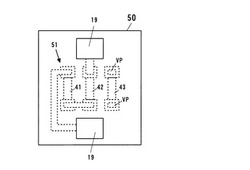

【解決手段】所定の配線パターンと共に両端に端子を備えた抵抗素子の複数41、42、43、を含む抵抗素子領域を形成するための所定配線用マスクを用いたリソグラフィステップと、半導体ウエハ特有の配線パターンと共に特有の配線パターンに応じて抵抗素子の端子間にて直列およびまたは並列接続された接続配線を含む識別領域50を形成するための識別配線51用マスクを用いたリソグラフィステップと、接続配線に接続され露出したパッド19を形成するためのパッド配線用マスクを用いたリソグラフィステップと、を含む。第1配線層および第2配線層の抵抗素子領域および識別領域の組がTEGチップまたはスクライブラインに形成されている。露出したパッドを介して抵抗素子の直列およびまたは並列接続された接続配線の抵抗値を測定するステップを更に含む。

(もっと読む)

半導体装置および貫通電極のテスト方法

【課題】貫通電極のショート不良およびオープン不良をチップまたはウェハ状態で検出可能な構造とする。

【解決手段】集積回路2がシリコン基板1の第1主面(いわゆる表面)側に形成されている。貫通電極3はシリコン基板1を厚さ方向に貫通して一端が集積回路2と電気的に接続されている。マイクロバンプ電極10はシリコン基板1の第2主面側に形成され、貫通電極3の他端と電気的に接続されている。テストパッド電極11はシリコン基板1の第2主面側に形成され、マイクロバンプ電極10と電気的に接続されている。

(もっと読む)

半導体集積装置の評価システム及び評価用半導体チップ

【目的】プラズマプロセスによる半導体集積装置の各製造段階において、所望のエッチング工程で生じたチャージアップの度合いのみを測定することが可能な半導体集積装置の評価システム及び評価用半導体チップを提供することを目的とするものである。

【構成】評価用半導体チップにプラズマエッチング処理を施している間にこの評価用半導体チップ内に生じたチャージアップに伴って流れる電流を、評価用半導体チップから外部に導出されている第1リード線及び第2リード線を介して計測する。評価用半導体チップは、シリコン基板上にゲート酸化膜、ゲート電極、プラズマによる電子電流の流入を部分的に遮断するパターンを有するレジストが積層された構造を有する。この際、レジスト上面側からシリコン基板の表面までを貫通する第1のコンタクトホールを介して上記第1リード線がシリコン基板の表面と電気的に接続されていると共に、上記レジストを貫通する第2のコンタクトホールを介して第2リード線がゲート電極の表面と電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 デュアルダマシン法による配線構造の製造において、接続プラグ用のホールを通じて下層配線の表面に凹部をエッチング形成するとき、上層配線用の溝の底部が過剰エッチングされないようにする。

【解決手段】 TaNなどからなり、接続プラグに対応する開口を有する導電性膜パターン112をSiOCなどからなる層間絶縁膜111と113との間に設けた後、配線溝114、ホール115を形成する。次にTaN、Taなどからなる積層導電性膜116を堆積し、ホール115の底部の積層導電性膜116を除去し、さらに下層配線を構成するCu膜109を掘り込むエッチングを行う。このとき、導電性膜パターン112があるために配線溝114の底部の下にある層間絶縁膜111のエッチングを防止できる。その後、配線溝114およびホール115内にCuなどの導電性膜117を埋め込む。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

半導体集積回路

【課題】少なくともロジック回路ブロックを含む半導体集積回路において、半導体集積回路の電源用パッドとロジック回路ブロックの電源ラインとを接続する電源配線、及び/又は、半導体集積回路のグランド用パッドとロジック回路ブロックのグランドラインとを接続するグランド配線の抵抗値を下げる。

【解決手段】この半導体集積回路は、半導体基板と、半導体基板上にそれぞれの層間絶縁膜を介して形成され、半導体基板に形成された複数のトランジスタに接続されて複数のトランジスタと共に少なくともロジック回路ブロックを構成する複数の配線層と、複数の配線層が形成された半導体基板上に層間絶縁膜を介して形成され、複数の配線層における最大膜厚の5倍〜20倍の膜厚を有する最上層の配線層とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストの増加および歩留まりを低下させることなく、配線抵抗を下げることのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板100上の絶縁膜104上にマスク材料膜106を形成した後、第1のトレンチ形成用開口と第2のトレンチ形成用開口とを有するマスクパターン109をマスク材料膜106に形成する工程と、マスク材料膜106上に、第1のトレンチ形成用開口を露出する第3のトレンチ形成用開口112を有し、且つ、第2のトレンチ形成用開口部を覆うレジストパターン113を形成する工程と、レジストパターン113及びマスクパターン109を用いて、絶縁膜104内に第1のトレンチ115を形成する工程と、レジストパターン113を除去した後、マスクパターン109を用いて、絶縁膜104内に第2のトレンチを形成する工程とを備えている。

(もっと読む)

表示装置

【課題】TFTと接続するソース電極あるいはドレイン電極のスルーホールにおけるコンタクト抵抗を減少させ、表示装置の動作効率を向上させる。

【解決手段】スルーホールにおいて、TFTのソース部とソース電極8が接続している。ソース電極8は、バリヤメタル、Al合金82、キャップメタル83の3層から形成されている。バリヤメタルは半導体層と接触する下層81aとAl合金と接触する上層81bとに分かれている。バリヤメタルの下層81aをスパッタリングして形成した後、熱処理し、その後、ベースメタルの上層81b、Al合金82、キャップメタル83を連続してスパッタリングによって形成する。Al合金82と接触するバリヤメタルの上層81bは酸化されていないので、スルーホールにおけるコンタクト抵抗の上昇を防止することが出来る。

(もっと読む)

基板構造物の製造方法及び半導体装置の製造方法

【課題】製造工程を増加させることなく、基板構造物及び半導体装置の反りを調整することのできる基板構造物の製造方法、及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11の裏面11b側から半導体基板11に、貫通電極接続用配線パターン38を露出する貫通孔15を形成し、次いで、半導体基板11の裏面11b及び貫通孔15を覆うと共に、第1及び第2のシード層78,79により構成された裏面シード層16を形成し、次いで、第1のシード層78が形成された貫通孔15に、めっき法により貫通電極17を形成し、次いで、第1のシード層78と、貫通電極17が形成されていない第2のシード層79とを絶縁するように、エッチングにより、第1のシード層78の周囲に位置する部分の裏面シード層16を除去して、反り調整部材として機能する第2のシード層79を残す。

(もっと読む)

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

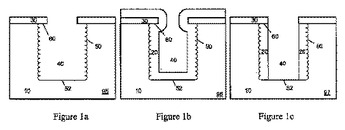

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

1,021 - 1,030 / 6,637

[ Back to top ]