国際特許分類[H01L21/8242]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | ダイナミックランダムアクセスメモリ構造 (2,471)

国際特許分類[H01L21/8242]に分類される特許

111 - 120 / 2,471

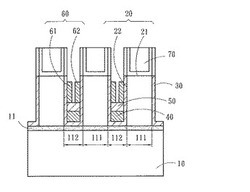

補助電極構造を備えた立体型DRAM

【課題】補助電極構造を備えた立体型DRAMの提供。

【解決手段】本補助電極構造を備えた立体型DRAMは、基板(10)、該基板(10)上に形成された少なくとも一つのビット線(11)、該ビット線(11)上の成長領域(111)に形成された柱状体(20)、補助電極(40)、該基板(10)に平行で且つ該ビット線(11)に垂直なワード線(60)、該柱状体(20)に接続されたコンデンサ(70)を包含し、該ビット線(11)は該基板(10)にドーパントをドープし並びに拡散を実行して形成され、該補助電極(40)は該ビット線(11)の間隔領域(112)に設置され、並びに該柱状体(20)に隣接し、該ワード線(60)は該補助電極(40)と絶縁されて設置され、並びに該ビット線(11)と組み合わされて該コンデンサ(70)に電子データを入出力する。本発明は該補助電極(40)の設置により、該ビット線(11)の抵抗を制御できるようにすることで、該ビット線(11)の導電能力を向上する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】短チャネル効果が抑制され、微細化を実現しつつ、安定した電気的特性を付与する半導体装置を提供する。また、上記半導体装置を作製する。

【解決手段】酸化物絶縁層に設けたトレンチに、トレンチに沿って成膜される酸化物半導体膜と、酸化物半導体膜と接するソース電極及びドレイン電極と、酸化物半導体膜上のゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有する半導体装置(トランジスタ)を設ける。該トレンチは下端コーナ部に曲面を有し、側部が酸化物絶縁層上面に対して略垂直な側面を有する。また、トレンチの上端の幅がトレンチの側面の幅の1倍以上1.5倍以下である。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体装置およびその作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】加熱処理により酸素を放出する絶縁体基板と、該絶縁体基板上に設けられた酸化物半導体膜と、を有し、該酸化物半導体膜にチャネルが形成されるトランジスタを有する半導体装置である。加熱処理により酸素を放出する絶縁体基板は、絶縁体基板の少なくとも酸化物半導体膜が設けられる側に、酸素イオン注入を行うことで作製することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、コンタクトプラグが形成されるセル部と、前記コンタクトプラグが形成されない周辺回路部とを平坦化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に最上部が第1の絶縁膜からなる配線層を形成する工程と、

前記半導体基板と前記配線層とを被う第2の絶縁膜を形成する工程と、前記第2の絶縁膜の所定の領域をエッチングし、前記配線層と前記半導体基板とを露出させる開口部を形成する工程と、前記開口部内と前記第2の絶縁膜上とに導電膜を形成する工程と、前記第1の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有し、前記第2の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有する条件で、前記第2の絶縁膜と前記導電膜とを前記第1の絶縁膜が露出するようCMP法で除去し、コンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

半導体装置

【課題】Y方向に隣接する2つの回路ブロックに対しX方向に延在する制御線からタイミング信号を同時に供給する。

【解決手段】例えば、Y方向に配列されたポートPT1,PT2と、ポートPT1,PT2にそれぞれ接続された回路C1,C2と、X方向に延在し回路C1,C2それぞれに含まれるサブ回路SC1,SC2を共通に制御する制御線CTL1を備える。サブ回路SC1,SC2のY方向における中間座標である座標Y1は、ポートPT1,PT2のY方向における中間座標Y0とは異なる。制御線CTL1からサブ回路SC1,SC2へのY方向における距離は互いに等しい。本発明によれば回路C1,C2の動作タイミングを正確に一致させることが可能となる。しかも、複数の制御線を必要とする場合であっても、制御線ごとに対応するサブ回路までの距離を一定とすることが可能となる。

(もっと読む)

111 - 120 / 2,471

[ Back to top ]