国際特許分類[H01L21/8244]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L21/8244]に分類される特許

51 - 60 / 855

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

半導体装置

【課題】不揮発性メモリを提供する。

【解決手段】一般的なSRAMと同様の回路構成を有し、該SRAMの記憶保持部と電源電位線の間にオフ電流の小さいトランジスタを配することで、記憶保持部からの電荷の漏れが防止された半導体装置(不揮発性メモリ)とする。ここで、記憶保持部からの電荷の漏れを防止するためのオフ電流の小さいトランジスタとしては、酸化物半導体膜により設けられたトランジスタを用いることが好ましい。このような構成はシフトレジスタにも適用することができ、消費電力の小さいシフトレジスタを得ることができる。

(もっと読む)

メモリセル

【課題】拡散層等のバルクが固定であってメタル層、コンタクト層の少なくとも何れか1層を変更して複数の仕様に対応可能なメモリセルを提供すること。

【解決手段】メモリユニットが列方向に沿って鏡面対称に行方向に沿って並置されて、2行2列に配置されメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第4拡散層を備え一対の記憶ノードが構成される。第1および第2ワード線は第1〜第4拡散層の両端部外方に配置される。第1及び第2ワード線の間に行方向に沿って第1のメタル配線領域が確保され、第1メタル層が配線可能とされる。列方向に隣接配置されるメモリユニットの境界領域でありは第3、第4拡散層が配置される列方向の位置には列方向に沿って第2のメタル配線領域が確保され、第2メタル層が配線可能とされる。

(もっと読む)

半導体記憶装置

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板と、少なくとも1つの島状半導体層110、該島状半導体層110の側壁の周囲の全部又は一部に形成された電荷蓄積層513及び制御ゲート523から構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層110が不純物拡散層により前記半導体基板から電気的に絶縁されてなる。

(もっと読む)

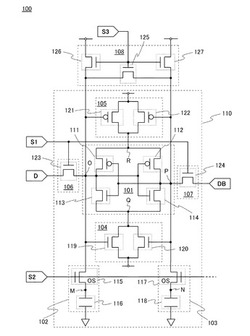

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

半導体装置および半導体装置を用いた記憶装置

【課題】データを一時的に待避させるための周辺回路を用いることなくオフ状態とすることが可能であり、かつ、装置の電源がオフ状態になっても記憶されたデータが消失しない、消費電力の低減された半導体装置および、当該半導体装置を用いた記憶装置を提供する。

【解決手段】半導体装置の保持回路に、オフ電流を十分に小さくすることができる酸化物半導体材料を用いて半導体層(少なくともチャネル形成領域)を形成したトランジスタを用いる。また、保持回路に蓄えられた記憶データと、外部から入力される参照データの比較処理を行う必要がない比較回路を、強制的に非活性状態とするスイッチング素子を備える構成とする。

(もっと読む)

トランジスタ及び半導体装置

【課題】SEU耐性が高く、高性能で低価なトランジスタ及び半導体装置を提供すること。

【解決手段】絶縁性基板12上に形成されたシリコン層と、シリコン層に形成され、第1導電型であるボディ(P−)15、第2導電型であるソース(N+)13、ドレイン(N+)14からなる部分と、ボディ(P−)15及びソース(N+)13にボディ(P−)15と同一導電型で接合され、ソース(N+)13と同じもしくは高い電位が供給されるボディ端子(P+)16と、を具備する。ボディ(P−)15において放射線によって発生した負電荷は、ボディ端子(P+)16を介して当該トランジスタ外に流出する。

(もっと読む)

51 - 60 / 855

[ Back to top ]