国際特許分類[H01L25/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 複数の個々の半導体または他の固体装置からなる組立体 (14,678) | すべての装置がグループ27/00〜51/00の同じサブグループに分類される型からなるもの,例.整流ダイオードの組立体 (8,439) | 個別の容器をもつ装置 (1,024) | 装置がグループ29/00に分類された型からなるもの (496)

国際特許分類[H01L25/11]に分類される特許

71 - 80 / 496

半導体デバイスの実装方法

【課題】高密度実装では占有面積の低減と低背化がキーとなっている。半導体デバイスを積層化した構造は高密度実装に適しているが、強度確保のための樹脂インターポーザの厚さ、上下のデバイスを電気接続する導電ボールの大きさ、ワイヤボンディングのための空間確保などにより、低背化が制限されていた。

【解決手段】樹脂よりもヤング率が大きい半導体インターポーザの採用、電気接続を複数の微小な金属塊から成る導電路で形成、フリップチップ構成の採用などにより、低背化が達成された。また、前記金属塊の形状、大きさ、配置などを最適化することにより、積層化プロセスが容易になった。

(もっと読む)

大電力スタック

【課題】装置の全長寸法を増加させることなく絶縁性能を高めた大電力スタックの提供を目的とする。

【解決手段】本発明の大電力スタックは、複数個の平型半導体素子10と金属製冷却フィン8とを交互に積層した積層体と、積層体の両端に設けられこれを圧接する金属製プレート7と、金属製プレート7間に渡され圧接圧力を保持する金属製ボルト4と、金属製ボルト4を被覆する円筒状の絶縁パイプ1と、金属製冷却フィン8に配設され、金属製冷却フィン8・絶縁パイプ1間の位置決めを行う絶縁物で構成された位置決め板5とを備える。絶縁パイプ1は、金属製プレート7に隣接配置される、第1外径を有するベローズ形状の第1部分と、第1部分から金属製プレート7と反対の中央方向に延在する、第1外径よりも小さい第2外径を有する円筒状の第2部分とを有し、絶縁パイプ1の第2部分は位置決め板5の穴5a、5bを貫通する。

(もっと読む)

モジュール

【課題】電子機器に搭載する場合に搭載面積を抑えることができ、搭載されている部品素子が外部から電磁波の影響を抑えることができるモジュールを提供する。

【解決手段】一方の主面に凹部空間が設けられ他方の主面に部品素子搭載パッドが設けられているカバーと、前記凹部空間の底面及び側面に一体的に設けられている金属からなるシールド膜と、前記部品素子搭載パッドに搭載されている部品素子と、から構成されていることを特徴とするモジュールと 配線基板と、前記配線基板に搭載されている配線基板用部品素子と、から主に構成されており、前記配線基板に搭載されている前記配線基板用部品素子が前記凹部空間内に収納され、前記シールド膜が所定の一つの配線基板接続端子と電気的に接続されていることを特徴とする。

(もっと読む)

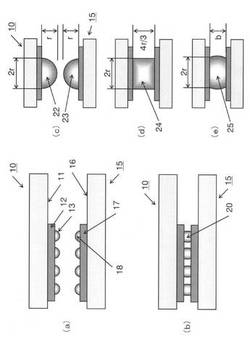

高密度集積回路モジュール構造

【課題】基板をヒートシンクと電気的に接触させることによって逆交互接触積層構造を構成し、電子製品の高さが限定されている場合であっても、製品の機能を高めることができる高密度集積回路モジュール構造を提供する。

【解決手段】高密度集積回路モジュール構造は、少なくとも基板20とヒートシンク30とを具備し、基板は、ヒートシンクと電気的に接触させることによって逆交互接触積層構造を構成し、熱伝導体31は少なくとも非平坦構造を有する。この構成によって、電子製品の限定された高さ内で製品の機能を高めることができ、かつ、耐振動性や放熱性を高めることができる。組立手続工程において、はんだボールとキャリアの結合を行う工程が不要となり、製品の機能向上、容量の拡大、製造コストの低減を図りつつ組立作業を簡素化できる。

(もっと読む)

積み重ねられたパッケージ間のワイヤボンド相互接続を有する半導体マルチパッケージモジュール

【課題】それぞれのパッケージにおいて予めテスト可能であり、製品MPMの最終テスト歩留まりをより高くする。

【解決手段】積み重ねられた下側および上側パッケージを有する半導体マルチパッケージモジュールであって、パッケージのそれぞれは、基板に取り付けられたダイスを有し、上側および下側基板は、ワイヤボンディングにより相互接続されるものである。また、半導体マルチパッケージモジュールの形成方法であって、下側基板およびダイスを有するモールドされた下側パッケージを供給し、上側基板を有するモールドされた上側パッケージを前記下側パッケージの上側表面上に取り付け、前記上側および下側基板間のz軸相互接続を形成するものである。

(もっと読む)

積層型半導体装置

【課題】積層される2つの半導体装置間の接合性を損なうことなく、接続不良を回避する。

【解決手段】積層型半導体装置50は、第1の配線基板1に形成された複数の第1の電極4b,4c,4d,4eと、各第1の電極4b,4c,4d,4eに形成され、柱状に突出する複数の突出電極5b,5c,5d,5eと、を備えている。また、積層型半導体装置50は、第2の配線基板21に形成された複数の第2の電極24b,24c,24d,24eと、同一のはんだ量で形成された複数のはんだ電極25b,25c,25d,25eと、を備えている。各突出電極5b,5c,5d,5eは、はんだ電極25b,25c,25d,25eよりも高融点材料で形成され、且つ第1の電極とはんだ電極との離間距離が大きいほど、高さが高く設定されている。

(もっと読む)

電子デバイス及びその製造方法

【課題】接合熱処理温度が低くて済み、凝固後は高い融点を確保し得る高耐熱性の電子デバイス及びその製造方法を提供すること。

【解決手段】複数枚の基板WF1〜WFrのそれぞれは、縦導体31と、接続導体4とを有している。複数枚の基板WF1〜WFrのうち、隣接する基板WF1、WF2は、一方の基板WF2の接続導体(縦導体)31が、他方の基板WF1の接続導体4と、接合膜5によって接合されている。接合膜5は、第1金属または合金成分と、それよりも融点の高い第2金属または合金成分とを含み、凝固後の溶融温度が第1金属または合金成分の融点よりも高くなっている。

(もっと読む)

表面実装デバイス及びプリント基板、並びに、それらを用いた表面実装デバイスの実装構造体

【課題】樹脂補強等の後工程補強を行うことなく、上層の表面実装デバイスと下層の表面実装デバイスとの接続強度を向上させた実装構造体を提供する。

【解決手段】混合POP型のBGAパッケージを、プリント基板に直接実装される第1BGAパッケージ21と、第1BGAパッケージ21の表面の面内方向に配列・実装された、1段の及び/又は多段に積層された複数の第2BGAパッケージ22、23とにより構成する。上下に隣接する2つのBGAパッケージにおいて、下層のBGAパッケージの、上層のBGAパッケージと対向する側の面に、上層のBGAパッケージが有する複数の半田ボールにそれぞれ対応する複数のパッドを形成し、複数のパッドを、下層のBGAパッケージの、上層のBGAパッケージと対向する側の面に形成された複数の第2凹所の各底部にそれぞれ設ける。

(もっと読む)

インバータ回路ユニット

【課題】両面空冷方式の半導体装置を備えるインバータ回路ユニットについて、半導体装置の構造を活用した位置決め機構の実施により、組立て性及び製品性能を確保する。

【解決手段】インバータ回路ユニット30は、半導体装置10を収納するとともに、内部に配置された複数個の第1のフィン112に対して送風される空気の取り入れ口である複数個の通風口32bを側面に形成する通風路形成部材32,33を備える。通風路形成部材32,33は、隣り合う通風口32bを仕切る仕切り部32aと、内壁面から突出する凸部であって主面に平行な方向Xの外方に本体部226よりも突き出る部分における基板部110間の隙間110CLに嵌まる第1の凸部38と、を有する。仕切り部32aは、半導体モジュール22を挟む基板部110間を外側から覆うとともに、内壁面側に第1の凸部38が形成されている。

(もっと読む)

積層チップパッケージの製造方法

【課題】本体の側面に配線が形成された積層チップパッケージを、低コストで短時間に大量生産すると共に、配線を精度よく形成する。

【解決手段】積層チップパッケージは、本体と、本体の側面に配置された配線を備えている。本体は、複数の階層部分を含んでいる。積層チップパッケージの製造方法では、まず、複数の構造体を形成する。複数の構造体の各々は、配線予定面2Pcを有する本体形成部分を少なくとも1つ含む。次に、配線予定面2Pcが上方向に向くように、複数の構造体を、配線予定面2Pcよりも低い位置にある上面を有する治具122によって囲って整列させる。次に、樹脂フィルムを用いて、治具122および複数の構造体を覆う樹脂層133を形成する。次に、配線予定面2Pcが露出するまで樹脂層133を研磨する。次に、配線予定面2Pcに対して一括して配線を形成する。次に、本体形成部分を分離する。

(もっと読む)

71 - 80 / 496

[ Back to top ]