国際特許分類[H01L27/088]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 1種類の半導体構成部品だけを含むもの (8,288) | 電界効果構成部品のみを含むもの (6,291) | 構成部品が絶縁ゲートを有する電界効果トランジスタであるもの (5,861)

国際特許分類[H01L27/088]の下位に属する分類

相補型MIS電界効果トランジスタ (2,948)

国際特許分類[H01L27/088]に分類される特許

1,001 - 1,010 / 2,913

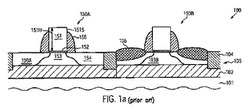

トランジスタにおいて進歩したシリサイド形成と組み合わされる凹型のドレイン及びソース区域

【解決手段】

洗練されたトランジスタ要素を形成するための製造プロセスの間、それぞれの金属シリサイド領域を形成するのに先立つ共通のエッチングシーケンスにおいて、ゲート高さが減少させられてよく、そして凹型のドレイン及びソース構造もまた得られてよい。対応する側壁スペーサ構造はエッチングシーケンスの間に維持され得るので、ゲート電極におけるシリサイド化プロセスの可制御性及び均一性を高めることができ、それにより、低減された程度のスレッショルドばらつきを得ることができる。更に、凹型のドレイン及びソース構造が、全体的な直列抵抗の低減及び応力転移効率の増大をもたらすことができる。

(もっと読む)

半導体装置

【課題】半導体装置の仕様を満たす電圧が得られているどうかを、半導体装置内で容易に検出できるようにする。

【解決手段】半導体装置の内部回路の出力電圧を検出し、前記出力電圧が半導体装置の仕様内の電圧であるか仕様外の電圧であるかを判定する機能を有する検出回路を備えており、前記検出回路は、前記出力電圧が仕様内であるか仕様外であるかを判定する信号をデジタル回路に送り、前記デジタル回路は当該信号に応じて回路動作の実行または停止を行う。

(もっと読む)

ファセットされたシリサイドコンタクトを有する半導体デバイス及び関連する製造方法

【解決手段】

開示される主題は、半導体トランジスタデバイス及び、従来のシリサイドコンタクトと比較して増大された実効サイズを有するシリサイドコンタクトを形成するために利用することができる関連する製造技術に関する。ここに開示されるプロセスに従って製造される半導体デバイス(200)は、半導体材質(102)の層と、半導体材質(102)の層を覆うゲート構造(112,128)とを含む。チャネル領域(218)が半導体材質(102)の層内に形成され、チャネル領域(218)はゲート構造(112,128)の下層となる。半導体デバイス(200)はまた、半導体材質(102)の層内のソース及びドレイン領域(216)を含み、チャネル領域(218)はソース及びドレイン領域(216)の間に配置される。また、半導体デバイス(200)はソース及びドレイン領域(216)を覆うファセット形状シリサイドコンタクト区域(210,308,406)を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11と、半導体基板11の上に形成され、第1の元素と第2の元素とを含むゲート絶縁膜26と、ゲート絶縁膜26の上に形成されたゲート電極27とを備えている。ゲート絶縁膜26は、半導体基板11側においてゲート電極27側と比べて第1の元素の含有量が多く、ゲート電極27側において半導体基板11側と比べて第2の元素の含有量が多い。

(もっと読む)

半導体装置およびその特性ばらつきのフィードバック方法

【課題】ランダムばらつきをオンチップでモニターして、MOSFETのしきい値電圧ばらつきを減らすように基板電圧、電源電圧にフィードバックをかけることを可能とする。

【解決手段】ソースフォロアに接続された複数のペアトランジスタ10と、複数のペアトランジスタ10が接続され複数のペアトランジスタ10の一つを選択する選択回路21と、選択回路21に接続されたラッチ回路22と、ラッチ回路22に入力すると同時にある一定の幅を持ったパルスが発振されるパルス発生回路23と、ラッチ回路22から出力される値と、パルス発生回路23から出力される値が同じであるか否かによってペアトランジスタの差分の有無を判定する判定回路24と、判定回路24で差分があると判定された回数をカウントするカウンタ回路26と、カウンタ回路26で加算された値mと設定値kとを比較し、電源電圧もしくは基板電圧にフィードバックする比較回路27とを有する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体装置の製造方法等に関し、ゲート絶縁膜へのプラズマダメージをなくし、ゲート絶縁膜の信頼性を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、MONOS型メモリトランジスタ領域101及びトランジスタ領域100を同一の半導体基板に有する場合、MONOS型メモリトランジスタ領域101にトンネル酸化膜7を形成し、そのトンネル酸化膜7上及びトランジスタ領域のゲート絶縁膜5上に窒化シリコン膜8を形成し、窒化シリコン膜上に酸化シリコン膜9を形成する工程と、MONOS型メモリトランジスタ領域101にマスク膜10を形成し、マスク膜10をマスクとして酸化シリコン膜9を除去する工程と、マスク膜10をマスクとして窒化シリコン膜8を熱燐酸によるウェットエッチングにより除去する工程とを具備することを特徴とする。

(もっと読む)

駆動回路、光プリントヘッド及び画像形成装置

【課題】複数のLED駆動回路間での駆動電流のばらつきを改善し、印刷濃度のむらを解消して印刷品位の向上を図る。

【解決手段】LEDプリントヘッドに搭載されるドライバIC中の複数のLED駆動回路110において、駆動トランジスタであるPMOS118〜122のゲート118G〜121G,122−1G〜122−4GをLEDアレイ方向(X軸方向)に並列に配置して、PMOSのチャネルがLEDアレイ方向に対して直交する方向(Y軸方向)となるように配置し、ドレイン電流をY軸方向に流す構成にしている。そのため、低温雰囲気中であってもドライバIC端部とドライバIC中心部との駆動電流の差が小さくなり、ドライバIC内での駆動電流のばらつきを改善できる。これにより、画像形成装置における印刷濃度のむらを解消できて印刷品位を向上できる。

(もっと読む)

絶縁ゲート型トランジスターチップ

【課題】本発明は、絶縁ゲート型トランジスターチップ内の要因により形成される帰還回路によるゲート発振を簡易な構成で抑制する絶縁ゲート型トランジスターチップを提供することを目的とする。

【解決手段】

半導体基板と、該半導体基板の表面に形成されたエミッタ電極と、該半導体基板の裏面に形成されたコレクタ電極と、該半導体基板の表面に形成されたゲートパッドとを備える。さらに、該半導体基板の表面に形成されて一端が該ゲートパッドと接続された第1ゲート配線と、該半導体基板の表面に形成されて該第1ゲート配線の他端と接続された第1内蔵抵抗と、該半導体基板の表面に形成されて一端が該第1内蔵抵抗を介して該第1ゲート配線の他端と接続された第2ゲート配線とを備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積、高速且つ高性能な歪みSOI構造の縦型MISFETを得ること。

【解決手段】Si基板1上に酸化膜2を介して、横方向エピタキシャルSiGe層3が設けられ、SiGe層3は素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。SiGe層3上には選択的に縦方向エピタキシャルSiGe層7が設けられ、SiGe層7の側面には格子定数がやや小さい横方向エピタキシャル歪みSi層8が周設され、歪みSOI基板を形成しており、SiGe層7及び歪みSi層8の上部にはドレイン領域(10、11)が設けられ、SiGe層3全体、SiGe層7及び歪みSi層8の下部にはソース領域9が設けられ、歪みSi層8の側面にはゲート酸化膜12を介してゲート電極13が周設され、ドレイン領域11、ソース領域9及びゲート電極13には、それぞれ導電プラグ20を介してCu配線23が接続されている歪みSOI構造の縦型のMISFETを構成すること。

(もっと読む)

半導体装置の製造方法

【課題】ゲートラストプロセスで作製するトランジスタにおいて、活性領域と素子分離領域の高さばらつきのためゲートのポリシリコンを抜くことができないことにより、ゲートの抵抗にばらつきが生じるのを防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、第1のゲート部30及び第2のゲート部31の上面が共に露出するように、酸化膜16、PMD19、及び第1のゲート部30又は第2のゲート部31の一部を研磨除去する工程、露出された部分より、ポリシリコン12を抜く工程、第1のゲート部30及び第2のゲート部31を覆うメタルを形成する工程を備える。また、第1のゲート部30及び第2のゲート部31の上面が共に露出するようにメタルを研磨除去し、第1のゲート部30と第2のゲート部31で厚みの異なるメタルを残す工程を備えて構成される。

(もっと読む)

1,001 - 1,010 / 2,913

[ Back to top ]