国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

901 - 910 / 3,785

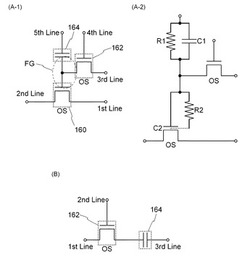

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

半導体集積回路

【課題】ビット線フックアップ回路における配線層間の耐圧を保障できる半導体集積回路を提供する。

【解決手段】順次配置された第1〜第4のビット線を有するメモリセルアレイ11と、メモリセルアレイ11の一端側に配置され、第1,第3のビット線に電気的に接続された第1センス回路12−1と、メモリセルアレイ11の他端側に配置され、第2,第4のビット線に電気的に接続された第2センス回路と、メモリセルアレイ11と第1センス回路12−1との間に配置され、電流通路の一端が第1のビット線に接続され、他端が第1センス回路12−1に接続される転送トランジスタTF0を含む第1フックアップ領域13−1と、第1フックアップ領域13−1と第1センス回路12−1との間に配置され、電流通路の一端が第3のビット線に接続され、他端が第1センス回路12−1に接続される転送トランジスタTF1を含む第2フックアップ領域13−2とを具備する。

(もっと読む)

記憶素子および記憶装置

【課題】書き込みデータの保持特性の向上および消去時の低電圧化、ならびに複数回の書き込み・消去動作に対して消去状態における抵抗値のばらつきを低減することが可能な記憶素子および記憶装置を提供する。

【解決手段】記憶層20は、テルル(Te)を含む高抵抗層22と、少なくとも1種類の金属元素を含むと共に、少なくとも1種のカルコゲン元素を含むイオン源層21とを有する。高抵抗層22が陰イオン成分としてテルル(Te)を主成分とすることにより、書き込み時にイオン源層21から高抵抗層22に拡散した金属元素が安定化され、書き込み保持特性が向上する。また、消去に必要な電圧が低電圧化されると共に、多数回の記録・消去動作を繰り返し行った場合の抵抗値のばらつきが低減される。

(もっと読む)

記憶装置、半導体装置、及び電子機器

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。位相反転素子への電源電圧の印加を停止する場合、データを容量素子に記憶させることで、位相反転素子への電源電圧の供給を停止しても、容量素子においてデータを保持させる。

(もっと読む)

半導体記憶装置

【課題】 ベリファイ動作を高速化し、データの書き込み速度を向上する。

【解決手段】 メモリセルアレイ1は、ワード線、及びビット線に接続され、n値(nは3以上の自然数)のうちの1値を記憶する複数のメモリセルが配置されて構成されている。制御回路7は、入力データに応じて前記ワード線、ビット線の電位を制御し、前記メモリセルにデータを書き込む。データ記憶回路10は、前記ビット線に接続され、少なくとも1ビット以上のデータを記憶する。制御回路7は、書き込み動作により、メモリセルの閾値電圧が第k値の閾値電圧に達したかのベリファイ時、前記第k値の閾値電圧より低い閾値電圧でベリファイ動作を行ない、前記メモリセルの閾値電圧が前記第k値の閾値電圧より低い閾値電圧を越えている場合、前記データ記憶回路内のデータを第k値より低い第i値の閾値電圧(i<k)への書き込みと同じデータに設定する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 低コストで、生産性及び歩留まりに優れる構造の不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】

メモリセル選択用のトランジスタが形成された基板上の同一層の第1の金属配線119及び第2の金属配線121上に、夫々、第1の開口部128及び第2の開口部129を同時に形成する。次に可変抵抗体124と上部電極126を、第1の開口部128内は上部電極126により完全に充填されるが、第2の開口部129内は完全に充填されることのないように全面に堆積する。その後、第2の開口部の底部に第2の金属配線121の表面が露出するまでエッチバックを行うことで、第1の開口部128内に可変抵抗素子104を、第2の開口部129内に第3の金属配線(ビット線)120と接続するための導通孔を、同時に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域中の層間絶縁膜を湿式エッチングにより除去する際に、使用する薬液が第2の領域に浸透することを防止する。これにより、第2の領域の特性の劣化がない、高性能の半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた第2の領域と、を有する半導体装置。第1の領域は、導電性を有する第1の膜によって構成された第1の電極を有する。第1の領域中の第1の電極の表面は、第2の膜で覆われていない。ガードリングは、凹状の溝の内壁を覆う第1の膜と、凹状の溝の内部において少なくとも第1の膜の表面の一部を覆う絶縁性の第2の膜を有する。

(もっと読む)

半導体集積回路

【課題】バス配線数を削減しつつ動作時の電流消費を抑えられる半導体集積回路を提供すること。

【解決手段】複数のバンク(バンク1、バンク2)に分割されるとともに多ビットのデータを処理する回路ユニット(例えば、メモリセルアレイプレート)と、多ビットのデータの入出力が行われる複数の入出力回路I/O1〜I/O4と、対応するデータ入出力回路I/O1〜I/O4と回路ユニットとを電気的に接続する複数のバス配線(b11、b12、b21、b22、b31、b32、b41、b42)と、を備え、バス配線のうち、バンク間を跨るように配置され、かつ、接続される前記バンクが互いに異なる2本以上のバス配線(b12とb31、b22とb41)は、中間部分にて共通化された共通バス配線(BUS13、BUS24)を有する。

(もっと読む)

リセス埋込ダイを備えるコアレスパッケージ

マイクロエレクトロニクスパッケージ構造を形成する方法、及びそれによって形成される構造物が提供される。該方法は、めっき部材に、ダイを保持するためのキャビティを形成し、前記キャビティ内にダイを取り付け、前記ダイに隣接して誘電体材料を形成し、前記ダイに隣接して前記誘電体材料内にビアを形成し、前記ビア内にPoPランドを形成し、前記ビア内にインターコネクトを形成し、その後、前記めっき部材を除去して、前記PoPランドと前記ダイとを露出させることを有し、前記ダイは前記PoPランドより上に配置される。  (もっと読む)

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】安定した動作が可能な不揮発性記憶装置及びその製造方法を提供する。

【解決手段】第1主面110fと、第1主面とは反対側の第2主面110mと、を有する第1導電層110と、第1主面に対向し、第1主面に対して平行な平面を含む第3主面120fと、第3主面の第1主面とは反対の側に設けられた第4主面120mと、第3主面と第4主面とに接する側面120sと、第3主面と側面との間に設けられ、第3主面よりも曲率が高い角部120cと、を有する第2導電層120と、第1導電層と第2導電層との間に設けられ、印加される電界及び通電される電流の少なくともいずれかによって電気抵抗が変化する抵抗変化層130と、第1導電層の第2主面に対向して設けられた整流素子70と、を備えた不揮発性記憶装置が提供される。第3主面の面積は、第2主面の面積よりも小さい。

(もっと読む)

901 - 910 / 3,785

[ Back to top ]