国際特許分類[H03H5/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | 回路網の部品として受動的電気素子のみを含む一端子対回路網 (107) | 電圧または電流に依存する素子を少なくとも1個もつもの (20)

国際特許分類[H03H5/12]に分類される特許

11 - 20 / 20

ミキサ回路および通信用半導体集積回路

【課題】 LC共振回路を負荷としたミキサ回路において、LC共振回路の共振周波数を変化させてもゲインが大きく変化したりQの値が大きく低下したりすることがないようにする。

【解決手段】 LC共振回路を負荷としたミキサ回路において、一次側の負荷インダクタ(L1,L2)と相互誘導結合される二次側のインダクタ(L3,L4)および該インダクタと並列に接続された可変容量(Cv1,Cv2)をLC共振回路に設け、可変容量に印加される制御電圧を変化させることで等価インダクタンス値を変化させて、LC共振回路の共振周波数を変化させるようにした。

(もっと読む)

積層型フィルタ

【課題】 バリスタ電圧を越える高い電圧のノイズが入力に印加された際に、バリスタ効果によって急激に流れた電流がノイズとなって通過するのを防止することができる積層型フィルタを提供する。

【解決手段】 積層型フィルタは、積層体2内にインダクタ部10及びバリスタ部20を備えており、インダクタ部10は、4Ω〜100Ωの直流抵抗を有している。これにより、バリスタ電圧を越える高い電圧のノイズが入力に印加された際に、バリスタ効果によって急激に流れた電流がノイズとなって通過するのを阻止することができる。

(もっと読む)

自己整合結合式共振器フィルタ回路およびそれを組み込む広帯域チューナ回路

自己整合共振器フィルタ、自己整合結合式共振器フィルタ回路(200)、ならびに、フィルタおよび回路を組み込むテレビジョンチューナ回路が本明細書に開示される。自己整合共振器フィルタは、チューナ回路の局部発振器(208)を梃子にし、オフチップコンポーネントの量を大幅に低減して実現することができる。自己整合共振器フィルタは、同調モード中に、抵抗素子の両端で測定される位相差に応答して所望の周波数で共振するように、同調可能共振器(206)の整合をとるように構成され、抵抗素子(214)は、ランモード中に、自己整合共振器フィルタからはずれるように切換えられる。自己整合結合式共振器フィルタ回路は、各共振器段が、他の共振器段によって影響を受けない状態で整合をとられることができるように、同調中に、個々の共振器段を分離するように構成される。テレビジョンチューナ回路は、比較的低コストで製造されることができ、一方、使用している間、高性能と動的に整合をとる能力を保持する。  (もっと読む)

(もっと読む)

MEMS型可変共振器

【課題】 構成を簡素化或いは小型化したMEMS型可変共振器を提供する。

【解決手段】 キャパシタと、信号ラインに配置したコイル3とを含む可変共振器1Aであって、前記キャパシタを構成する一方の電極が前記コイル3を兼ね、該一方の電極と他方の電極5との間隔を可変に形成したMEMS型可変共振器である。基板上に配置したコイル3が信号ラインに配置したコイルになると共に、電極5とでキャパシタを構成している。コイル3と電極5との間に直流バイアス電圧を印加すると、静電引力が作用して電極5が固定側のコイル3側に吸引されるので間隔が狭くなる。よって、このMEMS型可変共振器1Aは構成を簡素化して小型化を図ることができる可変共振器となる。

(もっと読む)

可変容量回路および可変容量回路の制御方法

【課題】 低電源電圧においても、可変容量素子の素子面積を増大させることや、制御電圧のレベル変換を行うことなく、可変容量素子の可変容量幅を最大限に広げることが可能な可変容量回路および可変容量の制御方法を提供すること。

【解決手段】 可変容量回路2は、容量値制御回路11、バラクタVA1およびVA2、抵抗素子R1およびR2を備える。容量値制御回路11は、入力される制御電圧VTに応じて、可変な出力電圧CNTOUTを出力することで、バラクタの両端の電位を同時に制御する。出力電圧CNTOUTは、制御電圧VTに対して、負の相関を有するように可変に調整される。端子間電圧VDの変動幅を、変動幅SA1から変動幅SA1a(レンジは±(Vcc1))へ拡大することができる。すると図5(B)に示すように、バラクタ容量値CVの可変領域を、可変領域CA1から可変領域CA1aへ広げることができる。

(もっと読む)

可変インダクタ並びにそれを用いた発振器及び情報機器

【課題】クオリティファクタの低下が少ない可変インダクタ並びにそれを用いた発振器及び情報機器を提供すること。

【解決手段】主インダクタL1に対して相互インダクタンスMを介して磁気的に結合している副インダクタL2に、素子値が可変のリアクタンス素子例えば可変容量かからなるインダクタンス制御回路41を接続する。可変容量の容量値を変化させるための制御信号を入力するインダクタンス制御端子VLCをインダクタンス制御回路に設ける。制御信号によって容量値を変化させることによって主インダクタのインダクタンスを変える。

(もっと読む)

可変容量コンデンサ,回路モジュールおよび通信装置

【課題】 波形歪みや相互変調歪みが小さく、耐電力に優れた、低損失な可変共振回路を提供する。

【解決手段】 高周波信号の入力端子Iと出力端子Oとの間に印加電圧により誘電率が変化する薄膜誘電体層を用いた複数の可変容量素子C1〜C4が直列接続されており、印加電圧の高電位側の第1バイアスラインB11,B12,B13と低電位側の第2バイアスラインB21,B22とが、複数の可変容量素子の両端および各素子間に交互に接続されていることから、バイアス信号による可変容量コンデンサの容量変化率を最大限に利用して広い周波数範囲にわたり共振周波数を変化させることができ、かつ、高周波電子部品において波形歪みや相互変調歪みが小さく、耐電力に優れた、高周波でも低損失な可変容量コンデンサとすることができる。

(もっと読む)

線形容量を有する電圧制御発振器

【課題】線形及び単調な容量特性を持つ電圧制御発振器を達成し、これによる連続及び単調な利得が得られ、位相雑音の低減を可能とする。

【解決手段】 電圧制御発振器は、増幅器(5)と、インダクタ(L)、及びその制御電圧によって変化する容量をそれぞれ有する、直列に接続の第1(Cv+)及び第2(Cv−)の可変コンデンサを備える発振システム(6)とを備える。可変コンデンサの1つ(Cv+)の容量は、その制御電圧と同方向に変化し、他の可変コンデンサ(Cv−)の容量は、その制御電圧と反対方向に変化する。固定容量を有するコンデンサは、第1(Cv+)及び第2(Cv−)の可変コンデンサと直列又は並列に接続され、第1及び第2の可変コンデンサは、各々PMOS及びNMOS型トランジスタにて形成される。追加の第1及び第2の可変コンデンサの追加の列は、第1及び第2の可変コンデンサと並列に接続される事ができる。

(もっと読む)

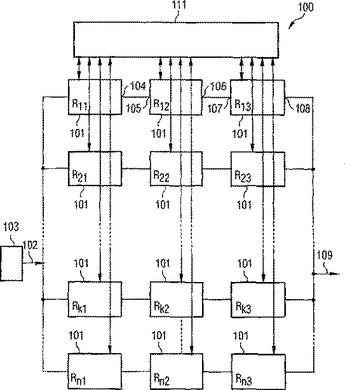

回路配列および信号処理装置

本発明は、回路配列(100)および信号処理装置に関するものである。この回路配列は、入力信号から出力信号を生成する共振器回路(101)を備えている。この共振器回路は、キャパシタ、インダクタ、入力信号を供給できる入力部、および、出力信号を供給できる出力部を備えている。さらに、この回路配列は、共振器回路のQを制御または調節する制御回路(111)を備えている。ここで、制御回路は、入力信号および/または出力信号の、振幅の信号曲線に応じて共振器回路のQを制御または調節するように、設置されている。  (もっと読む)

(もっと読む)

プログラム可能なトランシーバ

周波数およびプロトコルにとらわれない、デジタル入力および出力を有する無線周波数集積回路(RFIC)から構成される、完全統合型の、プログラム可能な混合信号トランシーバで、トランシーバは、複数の無線周波数帯域および規格にプログラム可能かつ構成可能で、多くのネットワークおよびサービスプロバイダに接続可能である。RFICは、インダクタンスと、第1の制御信号に応じて同調可能な共振回路にスイッチを入れられ切られるように構成される複数の切り替え可能なキャパシタと、第2の制御信号に応じて変更されることができる少なくとも1つの可変キャパシタとを有する伝送回線を含む同調可能な共振回路を含み、共振回路の共振中心周波数は、複数の切り替え可能なキャパシタの第1のキャパシタンス値と、少なくとも1つの可変キャパシタの第2のキャパシタンス値とを制御する第1および第2の制御信号に応じて電気的に同調可能である。  (もっと読む)

(もっと読む)

11 - 20 / 20

[ Back to top ]