国際特許分類[H03K19/013]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | スイッチ動作の高速化のための変形 (58) | バイポーラトランジスタ回路におけるもの (10)

国際特許分類[H03K19/013]に分類される特許

1 - 10 / 10

通信システム

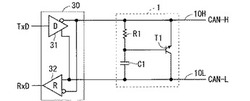

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】トランシーバ回路30等の通信回路に接続される通信線10を構成するHライン通信線10H,Lライン通信線10L間にリンギング抑制回路1が設けられる。リンギング抑制回路1において、バイポーラトランジスタT1のエミッタはHライン通信線10Hに接続され、コレクタはLライン通信線10Lに接続され、ベースはコンデンサC1の一方電極及び抵抗R1の一端に接続され、コンデンサC1の他方電極はLライン通信線10Lに接続され、抵抗R1の他端はHライン通信線10Hに接続される。

(もっと読む)

出力バッファ回路およびそれを用いたドライバ回路

【課題】 入出力信号が変化する際の過渡期間に出力バッファを構成するトランジスタへのバイアス電流を一時的に増強することで、バッファ回路全体の定常的なバイアス電流を抑制しつつ、高スルーレートが得られるバッファ回路を提供する。

【解決手段】 ドライバ回路200は信号レベル発生回路100により発生した信号SGOを出力バッファ回路110を駆動する回路150(プリバッファ回路)を介し、出力バッファ回路110により伝送線路120を駆動することで測定対象回路DUT140に伝える。プリバッファ回路150とこれを模擬したレプリカバッファ回路160とを互いに並列に備え、信号SGOが変化する際の入出力新信号の過渡期間において、レプリカバッファ回路160の出力電流に基づいて出力バッファ回路110の出力段トランジスタQN12、QP22の入力バイアス電流を一時的に増強する。

(もっと読む)

ドライバ回路およびそれを用いた試験装置

【課題】高速なドライバ回路を提供する。

【解決手段】レベルスイッチ回路20は、デジタルの入力信号INを受け、その値に応じた電圧レベルvih、vilを有するレベル信号sigを生成する。バッファ回路30は、レベル信号sigを受け、それを出力端子7から出力する。バイアス電流生成回路40は、一定レベルの直流成分i_dcと入力信号INに応じて変動する変動成分i_dynとを含むバイアス電流i_biasを生成し、バッファ回路30へと供給する。バイアス電流生成回路40は、入力信号INのエッジを検出し、エッジから所定期間Tr、Tfの間、バイアス電流i_biasを所定量だけ増加させる。

(もっと読む)

比較回路

【課題】比較回路の自己発熱を抑制して、自己発熱対策に起因する当該比較回路の動作速

度の低下を防止できるようにする。

【解決手段】差動増幅部11,12にスイッチS1,S2をそれぞれ接続させる。スイッ

チS1をONにして差動増幅部11を動作させるときには、スイッチS2をOFFにして

差動増幅部12を停止させ、スイッチS2をONにして差動増幅部12を動作させるとき

には、スイッチS1をOFFにして差動増幅部11を停止させる。この結果、スイッチS

1,S2によって差動増幅部11,12が交互に動作するので、差動増幅部11,12の

動作による自己発熱を抑制することができ、自己発熱対策に起因する比較回路1の動作速

度の低下を防止できる。

(もっと読む)

高速多重化回路

【課題】高速動作時の出力波形品質を改善する。

【解決手段】高速多重化回路は、データ信号列(D1P,D1N),(D2P,D2N)毎に設けられ、入力されたデータ信号列を共通に接続された信号出力端子に選択的に出力する第1のトランジスタQ1P,Q1N,Q2P,Q2Nと、トランジスタQ1P,Q1Nから構成される差動対またはトランジスタQ2P,Q2Nから構成される差動対のいずれか一方をクロック信号CK1,CK2に応じてオンにする第2のトランジスタQ3,Q4と、トランジスタQ1P,Q1N,Q2P,Q2N,Q3,Q4にコレクタ電流を流す電流源となる第3のトランジスタQ6,Q7と、第3のトランジスタQ6,Q7のコレクタとエミッタ側の電源電圧VEEとの間に挿入されたコンデンサC1とを備える。

(もっと読む)

スイッチングアンプ及びそのスイッチングアンプのレベルシフト回路

【課題】所定の振幅範囲でレベルが変化するPWM信号から振幅範囲の異なるPWM信号に変換するレベルシフト回路の簡単化を図る。

【解決手段】スイッチングアンプはオーディオ信号EsをPWM信号に変換して出力するパルス幅変調回路11の後段にシフトレベル回路12が設けられる。パルス幅変調回路11はPWM信号PsとPWM信号Psに対して逆相関係のPWM信号Ps’を出力する出力端子out1,out2を有する。シフトレベル回路12を抵抗R1、P型トランジスタQ1、N型トランジスタQ2および抵抗R2がこの順で直列接続された回路で構成し、この回路の両端を電源電圧+VB,−VBが入力される一対の電源端子に接続し、トランジスタQ1,Q2のベースにパルス幅変調回路11のout1を接続し、トランジスタQ1,Q2の接続点mにパルス幅変調回路11のout2を接続する構成とした。

(もっと読む)

ドライバ回路および試験装置

【課題】高周波成分を強調した信号を精度良く生成する。

【解決手段】外部から受け取った受信信号に応じた送信信号を出力するドライバ回路であって、入力される第1信号に応じた電圧を出力する第1ドライバと、第1ドライバが出力する電圧を電源電圧として受け取り、入力される第2信号および電源電圧に応じた送信信号を出力する第2ドライバと、受信信号の変化に応じて第1信号および第2信号の両方を変化させて、受信信号に応じた送信信号を第2ドライバから出力させる制御部と、を備えるドライバ回路を提供する。

(もっと読む)

コンパレ一タ回路

【課題】 スイッチングトランジスタにおける入力容量の低減、ゼロクロス周波数特性の向上を図り、高周波数の矩形波をサンプリングするコンパレータ回路(高周波トランジスタ回路)等の特性を改善する。

【解決手段】 プッシュプル回路40を構成するスイッチングトランジスタQ6と、前段のスイッチング回路30を構成する位相反転用トランジスタQ4のみを化合物半導体トランジスタで構成する。他のトランジスタの動作速度に限界があっても、充放電電流の減少やゼロクロス周波数の改善により、従来にない高速かつ高精度な動作(高周波数の矩形波のサンプリング等)が可能となる。

(もっと読む)

デジタル・ロジック回路のための誘導電流ステアリングを使用するシステムおよび方法

本発明は、誘導電流ステアリングを利用して、従来のトランジスタ電流ステアリングに関連付けられた伝搬遅延を軽減することにより、ロジック回路性能を改善するシステムおよび方法を提供するものである。これらのシステムおよび方法は、一次巻線にエネルギーを与えることにより、関連付けられた二次巻線に電流を誘導するRF変圧器を使用している。一態様においては、単一クロック・バスを使用して電流を誘導し、この電流がこの二次巻線のそれぞれの端部を経由してこれらのトランジスタのエミッタ・リードに経路指定される。この電流と電圧は、一方のトランジスタが「オン」であるが、他方は「オフ」であり、これが差動出力を生成するように、180度位相がずれている。別の態様においては、差動クロック信号を使用して、二次巻線および関連付けられたトランジスタのエミッタにこの電流を誘導する。さらに、これらのシステムおよび方法を利用して、差動トランジスタ対を結合し、この変圧器ベースのシングル・エンド・クロックまたは差動クロックを用いてこれらの対を駆動することにより、フリップフロップおよびシフト・レジスタを構成することができる。  (もっと読む)

(もっと読む)

ECL回路

【課題】カスケードトランジスタを持つ差動トランジスタ対で構成されるECL回路において、動作速度の温度による変化を従来よりも小さくする。

【解決手段】差動対トランジスタQ1 ,Q6 に、それらトランジスタとエミッタ電極を共通にしたもう一つの差動対トランジスタQ9 ,Q10を設ける。トランジスタQ9 ,Q10は、エミッタ面積を、差動対トランジスタQ1 ,Q6 のエミッタ面積より小さくする。コレクタ電極はそれぞれ、本来の差動対トランジスタQ1,Q6 に対し、逆相側のコレクタ電極に接続する。トランジスタQ9 ,Q10を通して回路に常に微小電流が流れているので、遅れ時間が短い。微小電流を流すのにトランジスタを用いているので、本来の差動対トランジスタと追加した差動対トランジスタとは、温度に対し同じ変化をする。従って動作速度の温度変化は、微少電流経路を抵抗で構成するのに比べ、小さい。

(もっと読む)

1 - 10 / 10

[ Back to top ]