国際特許分類[H03K3/354]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電気的パルスの発生回路;単安定回路,双安定回路,多安定回路 (1,702) | パルスの発生に用いられる回路形式または手段によって特徴づけられた発生器 (1,478) | 能動素子として内部または外部正帰還をもつ電界効果トランジスタを用いるもの (670) | 非安定回路 (292)

国際特許分類[H03K3/354]に分類される特許

1 - 10 / 292

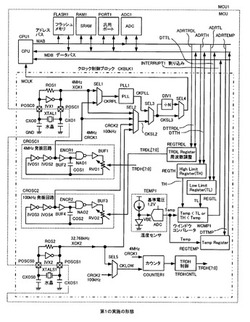

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に搭載されたデジタル制御発振装置が生成するクロック信号の品質を向上させる。

【解決手段】ICチップは周辺部を除く部位に位置する回路形成部位が、パルス遅延回路10からなる第1回路ブロック3と、時間/数値変換回路20及びデータ処理部30,デジタル制御発振回路40からなる第2回路ブロック5と、第1回路ブロック3及び第2回路ブロック5により形成されるデジタル制御発振装置1にて生成されたクロック信号CKOを利用した各種処理を実行するための周辺回路等からなる第3回路ブロック7とからなる。また、第1回路ブロック3は、電源パッドP1及び電源ラインL1を介して供給される第1の電源VDD1により駆動され、第2回路ブロック5及び第3回路ブロック7は、電源パッドP2及び電源ラインL2を介して供給される第2の電源VDD2により駆動されるように、レイアウトされている。

(もっと読む)

発振装置および無線通信装置

【課題】低消費電力で微弱な無線信号を受信する。

【解決手段】本発明の一態様としての発振装置は、クロック回路と、電源電流源と、発振回路とを備える。前記クロック回路は、クロック信号を生成する。前記電源電流源は、前記クロック信号に従って、電源電流を生成する。前記発振回路は、前記電源電流と、入力信号に基づき発振し、前記クロック信号の周波数より高い発振周波数を有する発振信号を生成する。

(もっと読む)

弛張発振回路

【課題】従来技術に比較して周波数が一定のクロックを発生できる弛張発振回路を提供する。

【解決手段】クロック発生サブ回路1は、基準電圧Vrefとコンパレータ14の誤差電圧ΔV1とを含む比較電圧Vcmp1を発生して出力電圧Vsub1としてコンパレータ14の反転入力端子に出力する比較電圧発生期間と、電流電圧変換回路11からの出力電圧Vc1を比較電圧Vcmp1と比較するクロック発生期間とを交互で繰り返すように制御される。クロック発生サブ回路2も、クロック発生サブ回路1と同様のクロック発生期間とを交互で繰り返すように制御される。制御回路5は、クロック発生サブ回路1及び2を、一方の回路が比較電圧発生期間であるときに他方の回路がクロック発生期間であるように制御する。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

半導体装置、タイミング検出方法及びタイミング調整方法

【課題】半導体装置の設計値に対するタイミング検出、設計値に対するタイミング調整を最適に行う半導体装置、タイミング検出方法及びタイミング調整方法を提供する。

【解決手段】オシレータ回路1−3と、テスト信号の活性化期間内に前記オシレータ回路に対してクロッキング動作を行わせる前記テスト信号を前記オシレータ回路に出力するコマンド回路1−1と、前記オシレータ回路と接続され、前記クロッキング動作によるクロッキング数をカウントするカウンタ回路1−2と、を備える。

(もっと読む)

抵抗周波数変換回路及び電子機器

【課題】製造バラツキによる影響の少ない発振回路を有した抵抗周波数変換回路を提供する。

【解決手段】抵抗周波数変換回路が、第1のノードと第2のノードとの間に接続された第1のキャパシターと、前記第2のノードと第3のノードとの間に接続され、前記第2のノードにおける信号を反転出力する第1の反転ゲートと、前記第3のノードと前記第1のノードとの間に接続される第1の抵抗と、前記第1のノードと第4のノードとの間に接続される第2の抵抗と、前記第4のノードにおける信号を増幅して前記第2のノードに出力することができる第1の回路と、を含む。

(もっと読む)

発振器

【課題】 発振器に含まれる複数の遅延反転増幅回路の配線容量を高い精度で一定にすることにより、容易に正確、かつ高周波数の多相クロックを生成できる発振器を提供する。

【解決手段】 リング状に接続された遅延反転増幅回路101〜105を、1列にレイアウトし、かつ、遅延反転増幅回路102の出力端子から103の入力端子までの配線長と、遅延反転増幅回路103の出力端子から104の入力端子までの配線長と、遅延反転増幅回路104の出力端子から105の入力端子までの配線長と、遅延反転増幅回路105の出力端子から101の入力端子までの配線長と、遅延反転増幅回路101〜105の出力端子と接続されている配線の配線長を全て等しくする。

(もっと読む)

半導体集積回路装置

【課題】 リングオシレータ回路を構成するインバータを切り替えることで変化する配線抵抗や配線容量などの変動をリングオシレータ回路の出力信号から得られる周波数変動から除去し、半導体回路の内部に実装されているトランジスタのランダムばらつきを検出する半導体回路装置を提供する。

【解決手段】 入力された信号の論理レベルを反転させる複数の回路素子を直列に接続した発振回路と、発振回路の出力周波数をカウントする信号処理部と、第1の回路素子に電源電圧を印加する電源端子と接地端子との間において互いに並列に接続された、互いの特性を比較した場合においてばらつきを持つ複数のトランジスタと、複数のトランジスタのうち、選択制御部によってそれぞれの1つが順番に選択されるようにタイミング信号を制御する。

(もっと読む)

発振回路

【課題】高精度発振が必要な場合には発振周波数の温度依存性を低減して高精度発振を可能とすると共に、高精度発振が不要な場合には発振回路の消費電流を低減することができる発振回路を提供する。

【解決手段】発振回路は、温度依存性が調整された出力電圧を出力するバンドギャップ回路と、第1の可変抵抗を備え、バンドギャップ回路から出力された出力電圧を第1の可変抵抗の抵抗値に応じた出力電流に変換し、変換された出力電流に基づいてバイアス電流を出力する電圧−電流変換回路と、第2の可変抵抗、容量及び比較部を備え、第2の可変抵抗の抵抗値と容量の容量値とに基づく発振周波数で発振すると共に、比較部が電圧−電流変換回路から入力されたバイアス電流の電流値に応じて動作するCR発振回路と、を備える。

(もっと読む)

1 - 10 / 292

[ Back to top ]