国際特許分類[H03K5/04]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | パルスの整形 (700) | 持続時間の増大によるもの;持続時間の減少によるもの (189)

国際特許分類[H03K5/04]の下位に属する分類

クロック信号または時間参照信号の使用によるもの (37)

遅廷線または他のアナログ素子の使用によるもの (20)

共振回路の使用によるもの (4)

国際特許分類[H03K5/04]に分類される特許

1 - 10 / 128

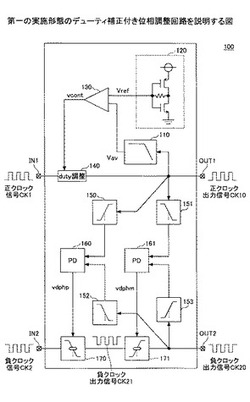

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

CMOSインバータ

【課題】 入力波形が急峻な場合でも反転電位を用いずに容易にデューティを補正することができるCMOSインバータを提供する。

【解決手段】 PMOSトランジスタP1と、NMOSトランジスタN1と、入力端子NGと、出力端子NDとを具備し、前記PMOSトランジスタ側もしくは前記NMOSトランジスタ側に接続されたスイッチを有している。前記スイッチがPMOSスイッチP2の場合には前記PMOSトランジスタ側に接続され、前記スイッチがNMOSスイッチの場合には前記NMOSトランジスタ側に接続される。入力端子NGに入力信号を入力した後に、前記スイッチに設けられた制御端子G1に制御信号を前記入力信号とずらして入力することによって前記入力信号の電圧を保持させ出力信号のデューティ補正を行う。

(もっと読む)

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

半導体装置

【課題】クロック伝送回路3の電流消費量の増大を抑えつつ、リードデータのジッタを軽減する。

【解決手段】半導体装置10は、アクティブ期間内に内部クロック信号LCLKよりも周期の長い長周期クロック信号を供給し、アクティブ期間に続くリード期間内に内部クロック信号LCLKを供給するクロック出力制御回路73と、クロック出力制御回路73から出力された内部クロック信号LCLK及び長周期クロック信号を伝送するクロック伝送回路3と、データ入出力端子14と、クロック伝送回路3によって伝送された内部クロック信号LCLKに同期して、データ入出力端子14にリードデータを出力する入出力回路64とを備える。

(もっと読む)

デューティ補償回路

【課題】補正対象クロックより高速なクロックを準備することなく、デューティ補償を可能とする。

【解決手段】デューティ検出回路106と、検出されたデューティから制御信号を生成するデューティ補正信号生成回路110と、デューティ補正回路104とを有し、デューティ検出回路は、可変遅延回路105により遅延させて得られるサンプリングタイミングでクロックをサンプリングしてそのデューティを検出する。

(もっと読む)

パルス幅調整回路及びこれを用いたデューティ比補正回路

【課題】入力クロック信号のパルス幅を安定して調整すること。

【解決手段】第1及び第2の電源間に設けられたパルス幅調整回路であって、ゲートに入力パルス信号INが入力される第1導電型の第1のトランジスタP1と、第1のトランジスタP1と第2の電源との間に設けられ、ゲートに入力パルス信号INが入力される第2導電型の第2のトランジスタN1と、第1のトランジスタP1と第1の電源との間に設けられ、ゲートに入力される第1の制御信号に応じて流れる電流が制御される第1導電型の第3のトランジスタP2と、第1のトランジスタP1と第1の電源との間に、第3のトランジスタP2と並列に設けられた第1の電流源回路102と、を備えるパルス幅調整回路。

(もっと読む)

クロックデューティ補正回路

【課題】出力されるクロック信号が発振することなく、デューティが一定になるようにクロック信号を補正することが可能なクロックデューティ補正回路を提供する。

【解決手段】クロックデューティ補正回路100は、クロック信号発生部から出力されたクロック信号が入力され、当該クロック信号の波形の立ち上がりに合わせて波形が立ち上がり、信号の周期が一定となるワンショットパルス信号を生成するワンショットパルス信号生成部110と、ワンショットパルス信号生成部110の出力信号を反転するインバータ113と、インバータ113の出力信号を遅延させる第1遅延回路114と、インバータ113の出力信号と、第1遅延回路114の出力信号との論理積を演算し、出力されるクロック信号のデューティを一定にする論理積回路116とを備える。

(もっと読む)

信号伝送回路、カラムA/D変換器、固体撮像素子およびカメラシステム

【課題】伝送される信号の論理を保ち、かつ、デューティ崩れの蓄積、加算を解消することが可能な信号伝送回路、カラムA/D変換器、固体撮像素子およびカメラシステムを提供する。

【解決手段】主信号が伝送される主伝送ライン11と、主伝送ライン11に縦続接続されるように配置され、伝搬される信号の反転機能を有する複数のリピータ13−1〜13−xと、各リピータの出力側の主伝送ラインから分岐するように接続された副伝送ライン14−1〜14−xと、各副伝送ラインに接続され、信号が供給される下位回路16−1〜16−xと、を有し、副伝送ラインが、主信号の反転論理の信号がリピータから供給される副伝送ラインである場合には、その副伝送ラインに反転回路15が配置されている。

(もっと読む)

1 - 10 / 128

[ Back to top ]