国際特許分類[H03K5/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | パルスの整形 (700) | 持続時間の増大によるもの;持続時間の減少によるもの (189) | 遅廷線または他のアナログ素子の使用によるもの (20)

国際特許分類[H03K5/06]に分類される特許

1 - 10 / 20

パルス幅延長回路および方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

パルス幅調整回路および方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

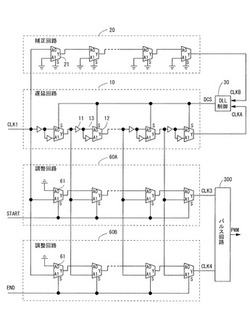

遅延クロック信号生成回路およびパルス生成回路

【課題】遅延経路を切り替えるマルチプレクサの遅延時間をキャンセルした遅延クロック信号生成回路を実現する。

【解決手段】N段直列接続の単位遅延段13からなり初段の単位遅延段13にクロック信号CLK1が入力する遅延回路10と、単位遅延段13のマルチプレクサ12と同一の遅延時間を有するN段直列接続のマルチプレクサ21からなり初段のマルチプレクサ21にクロック信号CLK1が入力する補正回路20と、遅延回路10の出力クロック信号CLKAと補正回路20の出力クロック信号CLKBとの位相差がクロック信号CLK1の1周期に等しくなるように遅延回路10の各単位遅延段13の遅延を制御するDLL制御回路30と、N段直列接続のマルチプレクサ12と同一の遅延時間を有するN段直列接続のマルチプレクサ61からなる調整回路60A、60Bとを備える。

(もっと読む)

出力信号制御装置、出力信号制御方法および出力信号制御プログラム

【課題】入力信号を遅延させて出力信号を作成する際に、入力信号の変動が原因で出力信号の遅延が規定値内に納まらない場合であっても、この出力信号によるエラーの発生の抑制が可能な出力信号制御装置、方法およびプログラムを得ること。

【解決手段】位相差許容範囲判別手段12は、位相差測定手段11が測定した出力信号の位相差がこの出力信号を入力する回路で許容範囲内であるかを判別する。出力制御手段13は、許容範囲内でないと判別する状態で出力信号の出力を遮断し、許容範囲内となった段階で出力を開始する。

(もっと読む)

パルス幅制御回路及び半導体メモリ

【課題】トランジスタのプロセス依存と配線幅のばらつきとに応じて適切なパルス幅に制御することが可能なパルス幅制御回路及び半導体メモリを提供すること。

【解決手段】配線による遅延とインバータによる遅延とを比較する比較回路と、インバータ段数によりパルス幅を調整するパルス幅調整回路と、を備える。パルス幅調整回路は、比較回路の比較結果に基づいて、インバータによる遅延が配線による遅延よりも小さくなった場合に、インバータ段数を多くし、パルス幅を増加させる。

(もっと読む)

半導体装置及びその制御方法並びにデータ処理システム

【課題】レベルシフトによって生じるスキューを無くす。

【解決手段】電圧の振幅値がVPERIである内部クロック信号LCLK3を電圧の振幅値がVDDである内部クロック信号LCLK4に変換するレベルシフト回路200aと、電圧の振幅値がVPERIである内部データ信号BD,BEを電圧の振幅値がVDDである内部データ信号CD,CEに変換するレベルシフト回路200bと、内部クロック信号LCLK4に基づいて相補の内部クロック信号LCLK5,LCLK5Bを生成するクロック分割回路300と、内部データ信号CD,CEに基づいて、内部クロック信号LCLK5,LCLK5Bにそれぞれ同期してデータ出力端子14から連続的に出力する出力回路400と、を備える。本発明によれば、出力回路400に入力される前にレベルシフトを行っていることから、出力データ間にスキューが生じない。

(もっと読む)

クロック生成装置、クロック生成方法およびデジタル放送受信装置

【課題】延回路を用いて低ジッタの周波数可変クロック生成システムを実現する。

【解決手段】クロック生成装置100は、CKinを遅延してCKoutを提供する遅延回路200,300と、稼動主遅延段選択部と、稼動補正遅延段選択部と、遅延制御部を具備する。遅延回路は、選択的に動作する複数の主遅延段D1〜Dnが縦続接続された主遅延部300および、この主遅延部に接続され選択的に動作する複数の補正遅延段C1〜Cmが縦続接続された補正遅延部(補正用ディレイ200)を含む。稼動主遅延段選択部は、主遅延段のうち遅延動作に用いられる稼動主遅延段を選択する。稼動補正遅延段選択部は、補正遅延段のうち遅延動作に用いられる稼動補正遅延段を選択する。遅延制御部(MPU120)は、稼動主遅延段を選択することでCKinに対するCKoutの遅延量を定め、稼動主遅延段の遅延値が均一化するように稼動補正遅延段を決定する。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

DDRメモリデバイスのデータ出力のデューティサイクル制御及び正確な調整のための複数の電圧制御された遅延ラインの利用

【課題】DDRメモリにおいて、デューティの歪みを生じさせることなくデータ信号のライジングとフォーリングエッジの双方を効果的に同期させるDLL回路を提供する。

【解決手段】DDRメモリの出力データ信号の50%のデューティを保証するための3DLL回路であって、第1クロック信号から第2クロック信号を生成する第1DLLと、前記DDRの出力データ信号の1つの遷移を調整する第2DLLと、前記DDRの出力データ信号の第2の遷移を調整する第3DLLを備え、前記第2、第3DLLに設けられた第2、第3遅延ラインの出力のライジングエッジにより生成されるライジングとフォーリングエッジを有し、前記DDRの出力データ信号をイネーブルにする第3クロック信号と、前記第3クロック信号を固定時間遅延させ、前記第2、第3DLLの第2、第3位相検出手段へフィードバックすることにより生成される第4クロック信号とを有する構成とする。

(もっと読む)

パルス生成方法、パルス生成回路およびそのハードマクロ

【課題】SRラッチによってパルス幅変調信号を生成する際に、SRラッチの入力信号幅の最小スペック値に影響されずに、パルス幅変調信号を微細化できるようにする。

【解決手段】1つのパルス幅変調信号を作成するためのセット信号とリセット信号の組を複数組入力して、複数のパルス幅変調信号からなるパルス列を生成するパルス生成方法において、前記組を時間軸上の奇数番目と偶数番目に分離し、奇数番目の前記組により第1のSRラッチでパルス幅変調信号を作成し、偶数番目の前記組により第2のSRラッチでパルス幅変調信号を作成し、第1のSRラッチで作成したパルス幅変調信号と第2のSRラッチで作成したパルス幅変調信号を時間軸上で合成して前記複数のパルス幅変調信号のパルス列信号を生成する。

(もっと読む)

1 - 10 / 20

[ Back to top ]