国際特許分類[H03K5/1252]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | パルスの識別 (173) | 雑音または干渉の抑制または制限 (129)

国際特許分類[H03K5/1252]の下位に属する分類

国際特許分類[H03K5/1252]に分類される特許

1 - 10 / 116

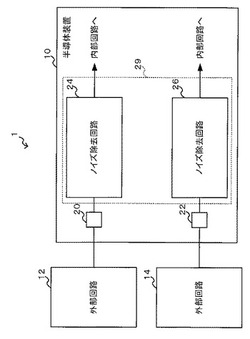

半導体装置及びノイズ除去装置

【課題】電源電圧の変動を伴うノイズに対して、入力される信号に応じた入力端子の種別によってそれぞれ異なる手法を用いることによりノイズ耐性が装置内で向上する。

【解決手段】外部回路12から入力端子20を介してノイズ除去回路24に発振信号が入力される。電源ノイズにより電源電圧が変動した場合は、ノードBにLレベルパルスのグリッチが発生し出力信号が反転する。OR回路48には、当該出力信号と、遅延回路46により遅延されてグリッチ(反転)のタイミングがずれた遅延信号と、が入力されるため出力信号は、反転せずHレベルを保つ。一方、外部回路14から入力端子22を介してノイズ除去回路26に遅延に関する制限が厳しい高周波の発振信号が入力される。シュミット回路52の入力と出力との間に接続された容量素子C7により、ノードAが電源電圧に追従して変動するため、ノードBにグリッチが発生せず、反転せずにHレベルを保つ。

(もっと読む)

電子回路

【課題】 リセットに起因するディジタル回路の初期化時の誤動作の発生を減らす。

【解決手段】 電子回路において、ノイズ除去回路13は、パワーオンリセット信号などのリセット信号のノイズ除去を行い、ディジタル回路11は、ノイズ除去回路13によるノイズ除去後の信号でリセットされる。そして、早期有効化回路16は、そのリセット信号によるリセット状態が解除されるまでの期間、ディジタル回路11の出力信号を所定の値に固定する。

(もっと読む)

クロック出力回路

【課題】クロック出力回路1にて電流消費を抑えつつ、周波数が安定したクロックを出力する。

【解決手段】 発振回路10から出力される発振信号を論理否定するNOTゲート21A、22Aと、NOTゲート21Aの出力信号を論理否定するNOTゲート23と、NOTゲート22A、23の出力信号を入力信号とするRSフリップフロップ回路24とを備え、NOTゲート21Aの第1の閾値Th1はNOTゲート22Aの第2の閾値Th2よりも大きく、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなる。発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24が源クロックの出力を待機し、周波数が低くなるとRSフリップフロップ回路24が源クロックを出力する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

信号伝達装置

【課題】ハイブリッド自動車、電気自動車、家電機器、産業機器、及び医療機器の分野では、入出力間を直流的に絶縁した信号伝達装置が用いられているが、並列接続された2つのトランスに入力されるノイズレベルが互いに異なる場合でも、ノイズキャンセルを正常に作動させる。

【解決手段】信号伝達装置100は、1次巻線T11と2次巻線T12とは直流的に分離されており、1次巻線T11と2次巻線T12とは互いに別々の接地電位に接続されるトランスT1と、前記トランスT1の2次巻線T12からの出力が入力される第1コンパレータCM1及び第2コンパレータCM_M1と、前記第1コンパレータCM1の出力が入力される遅延信号生成部141aと、前記第2コンパレータCM_M1の出力が入力されるマスキング信号生成部143aとを有する。

(もっと読む)

集積回路

【課題】電源ノイズが存在する環境下において、位相同期回路の出力信号の特性劣化を軽減する。

【解決手段】基準信号源は、基本周波数を有する基準信号を生成する。位相同期回路102は、制御電圧に応じた周波数の信号を生成する電圧制御発振器106と、前記周波数の信号をN分周して第1分周信号を生成する第1分周器107と、第1分周信号と基準信号との位相差を検出する位相検出器103と、チャージポンプ104と、ループフィルタ105と、を含む。第2分周器は、電圧制御発振器により生成された信号をM分周して第2分周信号を生成する。信号処理回路は、第2分周信号に同期して動作する。基本周波数のK倍と、第2分周信号の周波数との差分の絶対値が、電圧制御発振器の入力から位相同期回路の出力までの伝達関数によって表される帯域通過フィルタの低域遮断周波数以下または高域遮断周波数以上となるように、NおよびMの値が決定されている。

(もっと読む)

半導体回路

【課題】本発明は、ハイレベルの入力信号に混入されたローレベルのノイズ及びローレベルの入力信号に混入されたハイレベルのノイズをより効果よく取り除くことができる半導体回路を提供する。

【解決手段】 入力信号を所定時間遅延して出力する遅延部120、220、320と、該入力信号のレベルによって電圧を充放電させる電圧調整部140、240、340と、該入力信号のレベル及び遅延部120、220、320から出力される信号のレベルを用いて生成された信号によって、電圧調整部140、240、340の充放電動作を制御する組合せ部160、260、360とを含む。

(もっと読む)

グリッジ処理回路

【課題】グリッジのパルス幅を十分に伸張させて後段回路で貫通電流が発生しないようにする。

【解決手段】単相の入力信号から差動信号をノードN1,N2に生成する単相/差動変換回路10と、ノードN1の信号をノードN3の信号でマスキシグしてノードN4に出力し、ノードN2の信号をノードN5の信号でマスキングしてノードN6に出力するマスキング回路30と、ノードN4,N6の信号を入力しノードN7,N8に出力信号を出力するラッチ回路30と、ノードN7の信号を時間T0だけ遅延させてノードN5に出力し、ノードN8の信号を時間T0だけ遅延させてノードN3に出力する遅延回路40とを具備し、ノードN8の信号を出力信号とする。

(もっと読む)

パルス信号補正装置およびそれを用いた充填装置

【課題】流量計と充填を制御する制御装置の間でノイズなどによって流量を表すパルスが増加あるいは消失すると、制御装置が正確な流量を把握できないので、正確に充填することができない。本発明はこのような課題を解決することを目的にする。

【解決手段】パルス信号補正装置を経由して流量計の出力を制御装置に入力する。パルス信号補正装置は流量計の出力と制御装置が受信したパルス数の差分を計算し、この差分に基づいて、次の出力周期で出力パルス数を補正するようにする。制御装置が正確な流量を得ることができるので、正確に充填できる。

(もっと読む)

グリッチフリークロック信号マルチプレクサ回路および動作の方法

【課題】クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。

【解決手段】クロックマルチプレクサ116は、第1のクロック入力を受信し、クロック出力118を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサ116は、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力118を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサ116の出力は第2のクロック信号のフェーズレベルに従う。

(もっと読む)

1 - 10 / 116

[ Back to top ]