国際特許分類[H03L7/093]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ループ中で特別なろ波または増幅特性を用いるもの (404)

国際特許分類[H03L7/093]に分類される特許

1 - 10 / 404

PLL回路

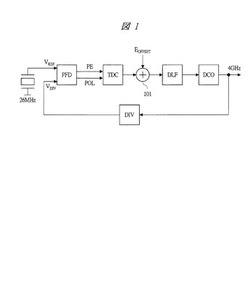

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

半導体装置及びこれを搭載する無線通信端末

【課題】回路規模の増大を抑止しつつ、ループ帯域の切替に際して生じるオフセットを補償する。

【解決手段】半導体装置(110)を構成する位相検出器(111)は、発振器(114)の出力信号を帰還した帰還信号と参照信号との間の位相差を検出し、位相差に応じた値を示す位相差値を生成する。増幅器(112)は、外部からの制御信号に応じて決定される増幅率で、位相差値を増幅する。フィルタ(113)は、増幅器(112)の出力値を平滑化する。発振器(114)は、フィルタ(113)の出力値に応じて、出力信号の周波数を制御する。

(もっと読む)

PLL回路

【課題】PLL回路において、VCOのゲインが低くても、VCOを構成するトランジスタの動作速度に関係なく、ターゲット周波数にロックさせることができ、かつ内蔵ループフィルタのMOS容量の電圧依存性に起因するジッタを抑制できるようにする。

【解決手段】PLL部のチャージポンプ20及びループフィルタ30をスリープ状態にし、校正部60のループフィルタ62の出力電圧V’inと校正用電源66の出力電圧Vdd/2とを電圧比較器63で比較する。比較結果を基に、V’in≒Vdd/2となるように、電流制御装置64によりデジタル制御電圧を生成し、デジタルアナログ変換器65によりアナログ制御電圧V+、V-に変換し、VCO40内の電圧電流変換回路41に供給する。

(もっと読む)

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

PLL回路

【課題】電圧制御発振回路の発振周波数レンジを広く保持しつつ、出力クロックのジッターを低減することが可能なPLL回路を提供する。

【解決手段】PLL回路は、基準クロックと出比較回路チャージポンプ回路を備え、チャージポンプ回路の出力に一端が接続された抵抗素子と、抵抗素子の他端に一端が接続され且つ接地に他端が接続された容量素子とを有し、チャージポンプ回路が出力した電流を変換して、抵抗素子の一端から第1の制御電圧信号を出力し且つ容量素子の一端から第2の制御電圧信号を出力する第1の低域通過フィルタを備える。PLL回路は、抵抗素子の一端に第1の非反転入力端子が接続され、容量素子の一端に第2の非反転入力端子が接続され、出力端子と反転入力端子とが接続され、出力端子から第3の制御電圧信号を出力するアンプ回路を備える。PLL回路は、第3の制御電圧信号に応じた周波数の出力クロックを出力するVCO回路とを備える。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

位相同期回路及びテレビジョン信号受信回路

【課題】チューニングラインに設けられるラインフィルタのフィルタ特性の低下を防止すること。

【解決手段】この位相同期回路は、チャージポンプ(35)から出力されるパルス信号を積分するローパスフィルタ(19)と、ローパスフィルタ(19)から電圧制御発振回路(17A)に対して制御電圧を供給する制御電圧供給ライン(LUHF)に設けられたラインフィルタ(20)と、を具備し、ラインフィルタ(20)のキャパシタ(C1)の一端をチャージポンプ(35)の出力端子からCP電流切替回路(36)の抵抗(r)を介してグランドに高周波的に接続した。

(もっと読む)

1 - 10 / 404

[ Back to top ]