国際特許分類[H03L7/14]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 供給電圧または補正電圧が低下したとき周波数を一定にすることを確実にするためのもの (71)

国際特許分類[H03L7/14]に分類される特許

1 - 10 / 71

周波数シンセサイザ

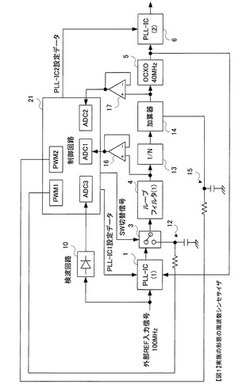

【課題】 外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号が「断」となった場合には、SW3に可変電圧供給回路12からの出力電圧にループフィルタ4に出力させる切替信号を出力し、更にループフィルタ4からの出力電圧を1/N分圧器13で分圧した電圧を微調制御電圧とし、オフセット電圧供給回路15からの電圧を粗調電圧として加算器14で加算してOCXO5の制御電圧として出力する周波数シンセサイザである。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

通信装置及び通信方法

【課題】PLL回路をベースとしたCDR回路を使用したトランシーバ間において、再同期を高速に行うことを目的とする。

【解決手段】PLL回路により構成されるクロック抽出部16に、受信信号を受信していない非受信状態の場合には、受信信号を受信している受信状態から非受信状態へ移行する時点におけるクロック信号の位相を示す位相情報を保持しておく受信側位相保持部22を追加する。データ送信時には、受信側位相保持部22が保持した位相情報を用いて生成されたクロック信号を用いて送信データを送信する。

(もっと読む)

クロック信号生成装置およびクロック信号生成方法

【課題】クロック信号の精度を向上させる。

【解決手段】パルス信号S2を決められた数だけカウントする毎にクロック信号S3を生成する際に、2回の1秒信号S1の出力時点間におけるパルス信号S2の第1カウント数とパルス信号S2の周波数との差分値である第1の誤差を決められた数から増減する補正処理を実行する処理部31〜33を備え、処理部は、1秒信号S1の出力時点から1秒間に生成すべき数のクロック信号S3を生成する毎に出力する1秒完了信号S6の出力時点までの間におけるパルス信号S2の第2カウント数が第1規定値以下のときに第2カウント数を第2の誤差として特定し、第2カウント数が第1規定値よりも大きくかつ周波数の値および第1の誤差を合計した値と第2カウント数との差分値の絶対値が第1規定値以下のときにその差分値を第3の誤差として特定し、補正処理において第1〜第3の誤差の合計値を決められた数から増減する。

(もっと読む)

PLL回路

【課題】 基準周波数断時におけるフリーランの出力周波数の精度を向上させるPLL回路を提供する。

【解決手段】 比例積分方式のPLL回路を用いて、積分器14の後にA/D変換部15とパタン生成部16を付加した構成とし、A/D変換部15が、ロック時の積分器14の出力電圧をデジタル信号として得て、ロック外れ時はロック時のデジタル信号を保持する機能を備え、ロック外れ時で基準周波数断時には、保持したデジタル信号に応じてパタン生成部16がパタン生成し、セレクタ13によって積分器14に出力するものであり、基準周波数断時には、パタン生成の波形を積分器14に代替入力するPLL回路である。

(もっと読む)

位相同期回路及びその制御方法

【課題】従来技術の位相同期回路では、入力クロックの切り替え時において、安定した出力クロックを生成することができないという問題があった。

【解決手段】本発明にかかる位相同期回路は、入力クロックを選択するセレクタ3と、入力クロックを分周する1/m分周器4と、フィードバッククロックを分周する1/n分周器5と、位相差検出器と、電圧保持回路30を有する電圧制御発振器10と、電圧保持回路31を有する電圧制御発振器11と、電圧制御発振器10,11のうちいずれかの出力を出力クロックとして出力するセレクタ13と、電圧制御発振器10,11のうちいずれかの出力をフィードバッククロックとして出力するセレクタ12と、備え、保持モードの電圧制御発振器が出力クロックfoutを生成し、通常モードの電圧制御発振器がフィードバッククロックを生成している場合に、入力クロックの切り替えが行われる。

(もっと読む)

基準信号発生装置及び方法

【課題】 GPS信号の受信障害が発生しても、内蔵オシレータよりも高い周波数安定度の基準信号を発生することと、受信障害の発生前後で連続性の高い基準信号を出力することとを両立した基準信号発生装置を提供する。

【解決手段】 GPS受信機にて取得したGPS受信時刻と、そのGPS受信時刻の直前或いはその直後に標準電波受信機にて取得した標準電波受信時刻との時刻差を、予め定められた時間間隔毎に算出し、算出した時刻差と日時とを関連づけた時刻差データベースを構築する。GPS受信障害の発生を未検出のときGPS受信時刻に基づいて電圧制御発振器を制御して基準信号を発生し、GPS受信障害の発生を検出中は、時刻差データベースから取得した現在の日時に対応する時刻差に基づいて標準電波受信時刻を補正して電圧制御発振器を制御して基準信号を発生する。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

同期信号生成装置、同期信号生成方法

【課題】ホールドオーバ状態からGPS通信衛星の電波を捕捉できる状態に復帰した場合、もしくはGPS通信衛星の電波を捕捉している状態からホールドオーバ状態に移行した場合、高精度の同期を迅速に行う同期信号生成装置、同期信号生成方法を提供することを課題としている。

【解決手段】同期信号生成装置1は、同期信号抽出部11と、制御部12と、同期部13と、DAC部(デジタル信号−アナログ信号変換部)14と、発振部15とを備えている。また、同期信号生成装置1には、GPS通信衛星アンテナ3と、基地局5とが接続されている。

(もっと読む)

1 - 10 / 71

[ Back to top ]