スイッチング素子駆動回路

【課題】 スイッチング素子のゲート容量を増大することなく、フライホイールダイオードの電圧が急激に立ち上がったときにも、ゲート電圧を安定して、高い応答性能を確保し、最大性能を出力する。

【解決手段】 スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去る。

【解決手段】 スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力用スイッチング素子などを駆動するスイッチング素子駆動回路に係わり、特にどのような運転モードで運転したときにも、安定した性能を維持できるようにしたスイッチング素子駆動回路に関する。

【背景技術】

【0002】

電力変換装置などで使用されるIGBT、MOSFETなどのゲート型スイッチング素子では、近年、大容量化、高速化にともない、その応用範囲を着実に広げている。

【0003】

また、このようなIGBT、MOSFETなどのゲート型スイッチング素子は、オン状態、オフ状態を自己継続しないノンラッチング型のスイッチ素子であることから、サイリスタなどのラッチング型のスイッチング素子に比べて、ゲート駆動による高い制御性を持つという利点がある。また、「Angelo Raciti et al“Control of the Switching Transients of IGBT Series Strings by High-Performance Drive Units”,IEEE Transactions on Industrial Electronics,Vol.48,No.3,June 2001」などの文献(非特許文献)からも分かるように、ターンオフ/ターンオンのスイッチング過渡期においても、ゲート制御によって、サージ電圧やサージ電流を抑制したり、スイッチング過渡期の電流や電圧の傾きを自在に制御することができる。

【0004】

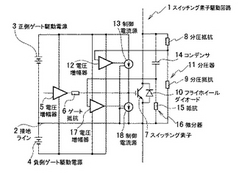

図6はこのようなゲート型スイッチング素子を駆動するスイッチング素子駆動回路の従来例を示す回路図である。

【0005】

この図に示すスイッチング素子駆動回路101は、正電圧側の電源として使用される正側ゲート駆動電源103と、負電圧側の電源として使用される負側ゲート駆動電源104と、図示しない制御装置から供給される制御信号を増幅して出力する電圧増幅器105と、電圧増幅器105から出力される制御信号の電流値を制限して制御対象となるスイッチング素子107のゲートに供給するゲート抵抗106と、分圧抵抗108及び分圧抵抗109によって構成され、フライホイールダイオード110が接続されたスイッチング素子107のコレクタ・エミッタ間電圧“Vce”を分圧して帰還信号を生成する分圧器111と、分圧器111からの帰還信号が設定値を超えているとき、これを増幅して出力する電圧増幅器112と、電圧増幅器112から出力される帰還信号に応じた電流を生成してスイッチング素子107のゲートに供給する制御電流源113とを備えている。

【0006】

そして、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器105から出力される制御信号の電圧が負側に振れると、ゲート抵抗106を介して、スイッチング素子107のゲート電圧が下がり始め、スイッチング素子107の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子107のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0007】

この後、スイッチング素子107のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めて、2つの分圧抵抗108、109の接続点からの帰還信号が予め設定されている設定値を超えたとき、電圧増幅器112から出力される帰還信号の値が上げられて、制御電流源113から出力される電流が増加してゲート電圧の低下が抑制される。

【0008】

これにより、スイッチング素子107の電流遮断時に、スイッチング素子107のコレクタ・エミッタ間電圧“Vce”が設定値を超えないようにすることができる。

【非特許文献1】Angelo Raciti et al“Control of the Switching Transients of IGBT Series Strings by High-Performance Drive Units”,IEEE Transactions on Industrial Electronics,Vol.48,No.3,June 2001

【発明の開示】

【発明が解決しようとする課題】

【0009】

ところが、従来のスイッチング素子駆動回路101では、スイッチング素子107のコレクタ・エミッタ間電圧“Vce”が設定値を超えるとき、コレクタ・エミッタ間電圧“Vce”を効果的に抑制できるものの、コレクタ・エミッタ間電圧“Vce”の時間変化率については、何らの考慮も払われていない。

【0010】

このため、スイッチング素子107のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいとき、スイッチング素子107のコレクタ、ゲート間に存在する内部帰還容量などにより、電圧増幅器105から出力される制御信号の電圧値より、スイッチング素子107のゲート電圧が高くなって、スイッチング素子107の動作が不安定になるという問題が発生していた。

【0011】

特に、スイッチング素子107のターンオフ特性に比べて、スイッチング素子107に並列に接続されているフライホイールダイオード110のターンオフ特性が急峻であることから、フライホイールダイオード110に流れていた電流がオフされたとき、逆回復時間を経過した後、フライホイールダイオード110自身の逆回復特性によって決まる時間変化率で、フライホイールダイオード110の電圧が急激に立ち上がり、スイッチング素子107の内部帰還容量を介し、ゲート電圧が持ち上げられ、本来、オフ状態になっていなければならないスイッチング素子107がオンしてしまうという現象がしばしば起こっていた。

【0012】

このようなゲート電圧の持ち上がりは、スイッチング素子107の予期せぬターンオンを引き起こすことがあることから、図6の回路図では、スイッチング素子107のゲート、エミッタ間にコンデンサ114を接続して、ゲート電圧を安定化するようにしている。

【0013】

しかしながら、このような対処方法では、内部帰還容量の影響を減殺できるものの、スイッチング素子駆動回路101側からみたスイッチング素子107のゲート容量が増大してしまうことから、応答性能が悪化してしまうという欠点が発生する。

【0014】

特に、極めて短い過渡期間にゲート電圧を制御して、スイッチング素子をスイッチングし、スイッチング素子の分担する主電圧を制御するアクティブゲート駆動技術を用いたスイッチング素子駆動回路などでは、ゲート駆動電流に対する応答性能の悪化がアクティブゲート駆動制御の性能悪化に直結してしまうという問題があった。

【0015】

本発明は上記の事情に鑑み、アクティブゲート駆動技術などを用いて、スイッチング素子を駆動した場合でも、高い応答性能を確保して、最大性能を出力できるスイッチング素子駆動回路を提供することを目的としている。

【課題を解決するための手段】

【0016】

上記の目的を達成するために本発明は、電圧増幅器によって、スイッチング素子のゲート端子に電圧信号を供給して、前記スイッチング素子の主電圧を制御するスイッチング素子駆動回路において、前記スイッチング素子の主電極間に印加される主電圧に応じて、前記ゲート端子に電流を注入する注入側制御電流源と、前記スイッチング素子の主電極間に印加される主電圧の時間変化率を検出して時間変化率検出信号を生成する時間変化率検出器と、この時間変化率検出器から出力される時間変化率検出信号に応じて、前記ゲート端子から電流を排出する排出側制御電流源とを備えたことを特徴としている。

【発明の効果】

【0017】

本発明によれば、スイッチング素子のゲート容量を増大することなく、フライホイールダイオードの電圧が急激に立ち上がり、スイッチング素子の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【発明を実施するための最良の形態】

【0018】

《第1の実施形態》

図1は本発明によるスイッチング素子駆動回路の第1の実施形態を示す回路図である。

【0019】

この図に示すスイッチング素子駆動回路1は、負電圧端子が接地ライン2に接続され、正電圧側の電源として使用される正側ゲート駆動電源3と、正電圧端子が接地ライン2に接続され、負電圧側の電源として使用される負側ゲート駆動電源4と、正側ゲート駆動電源3の正電圧端子から供給される正電圧、負側ゲート駆動電源4の負電圧端子から出力される負電圧を電源電圧として取り込み、図示しない制御装置などから供給される制御信号を増幅して出力する電圧増幅器5と、電圧増幅器5から出力される制御信号の電流値を制限してIGBTなどの制御対象となるスイッチング素子7のゲートに供給するゲート抵抗6と、スイッチング素子7のコレクタとエミッタ間に直列に接続された分圧抵抗8および分圧抵抗9によって構成され、フライホイールダイオード10が接続されたスイッチング素子7のコレクタ・エミッタ間電圧“Vce”を分圧して帰還信号を生成する分圧器11と、正側ゲート駆動電源3から供給される正電圧、負側ゲート駆動電源4から供給される負電圧を電源電圧として取り込み、分圧器11からの帰還信号が設定値を超えているとき、これを増幅して出力する電圧増幅器12と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3から供給される正電圧を電源電圧として取り込み、電圧増幅器12から出力される帰還信号に応じた電流を生成してスイッチング素子7のゲート端子に供給する制御電流源13とを備えている。

【0020】

さらに、スイッチング素子駆動回路1は、スイッチング素子7のコレクタとエミッタ間に直列に接続されたコンデンサ14および抵抗15によって構成され、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分し、コレクタ・エミッタ間電圧“Vce”の時間変化率を示す微分信号を生成する微分器16と、正側ゲート駆動電源3から供給される正電圧、負側ゲート駆動電源4から出力される負電圧を電源電圧として取り込み、微分器16からの微分信号を増幅して出力する電圧増幅器17と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧増幅器17から出力される微分信号に応じて、スイッチング素子7のゲート端子から電流を引き出して接地ライン2に流す制御電流源18とを備えている。

【0021】

そして、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられる。これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0022】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器12から出力される帰還信号の値が上昇して、制御電流源13から出力される電流が増加され、ゲート電圧の低下が抑制される。

【0023】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0024】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、微分器16によって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、電圧増幅器17から増幅された微分信号が出力されるとともに、制御電流源18によって、微分信号の値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0025】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源18によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0026】

このように、第1の実施形態では、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るようにしているので、スイッチング素子7のゲート容量を増大することなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0027】

また、第1の実施形態では、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0028】

《第2の実施形態》

図2は本発明によるスイッチング素子駆動回路の第2の実施形態を示す回路図である。なお、この図において、図1の各部に対応する部分には、同じ符号が付してある。

【0029】

この図に示すスイッチング素子駆動回路21は、図1と同様、正側ゲート駆動電源3と、負側ゲート駆動電源4と、電圧増幅器5と、ゲート抵抗6と、分圧器11と、微分器16とを備えている。

【0030】

また、第2の実施形態のスイッチング素子駆動回路21は、抵抗22,23によって構成され、分圧器11から出力される帰還信号をさらに分圧する分圧器24と、正側ゲート駆動電源3から供給される正電圧、負側ゲート駆動電源4から供給される負電圧を電源電圧として取り込み、非反転入力端子に供給される分圧器24からの帰還信号を非反転増幅して出力する電圧増幅器25と、一端がコンデンサ14と抵抗15との接続点に接続された抵抗26、一端が抵抗26の他端、電圧増幅器25の反転入力端子に接続され、他端が電圧増幅器25の出力側に接続された抵抗27によって構成され、電圧増幅器25から出力される帰還信号と微分器16から出力される微分信号との差信号を電圧増幅器25の反転入力端子に供給して、反転増幅する分圧器28と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧増幅器25から出力される帰還信号に応じて、スイッチング素子7のゲート端子に電流を供給する動作、またはスイッチング素子7のゲート端子から電流を引き去る動作を行う制御電流源13とを備えている。

【0031】

そして、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられ、これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0032】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器25から出力される帰還信号の値が上げられて、制御電流源13の電流出力が開始され、ゲート電圧の低下が抑制される。

【0033】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0034】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、微分器16によって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、分圧器28を介して、電圧増幅器25の反転入力端子に供給される。

【0035】

そして、電圧増幅器25の出力電圧は、分圧器28の分圧比と微分信号の電圧値とに応じた電圧値になるまで下げられるとともに、制御電流源13によって、電圧増幅器25の出力電圧値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0036】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源13によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0037】

この後、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が小さくなる従い、電圧増幅器25の出力電圧が元の電圧値まで、引き上げられるとともに、制御電流源13による、スイッチング素子7のゲート端子から電流の引き去り量が漸次、引き下げられる。

【0038】

このように、第2の実施形態では、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器25によって、前記微分信号を反転増幅して、制御電流源13を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るようにしているので、スイッチング素子7のゲート容量を増大することなく、かつ第1の実施形態のような制御電流源18を追加することなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0039】

また、第2の実施形態においても、第1の実施形態と同様に、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0040】

《第3の実施形態》

図3は本発明によるスイッチング素子駆動回路の第3の実施形態を示す回路図である。なお、この図において、図1の各部に対応する部分には、同じ符号が付してある。

【0041】

第1の実施形態、第2の実施形態では、ゲートから排出される電流の値に制限を設けていなかった。しかし、応用によっては、ゲートから排出される電流の値を制限したい場合もある。特にフライホイールダイオード10がすでにターンオフしてしまった後では、スイッチング素子7が自分自身で電圧を制御するモードに入るが、この場合はゲートから電流を排出するほどコレクタ・エミッタ間電圧の時間微分は大きくなることがあり、ゲートから排出される電流を制限しなければスイッチング素子7が急激にターンオフしてしまうことになる。

【0042】

本発明の第3の実施形態では、制御電流源18の最大出力電流の値をある一定の値以上にしないことで、スイッチング素子7が急激にターンオフしてしまう不具合を解消するものである。

【0043】

第3の実施形態を図3に基づいて詳述すると、この図に示すスイッチング素子駆動回路31は、第1の実施形態と同様、正側ゲート駆動電源3と、負側ゲート駆動電源4と、ゲート抵抗6と、分圧器11と、電圧増幅器12と、制御電流源13と、微分器16と、電圧増幅器17とを備えている。

【0044】

さらに、第3の実施形態のスイッチング素子駆動回路31は、制御端子に入力される制限電圧33の値に応じて、入力される電圧増幅器17からの微分信号を制限して出力する電圧制限器32と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧制限器32から出力される微分信号に応じて、スイッチング素子7のゲート端子から電流を引き出し、接地ライン2に流す制御電流源18とを備えている。

【0045】

そして、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられ、これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0046】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器12から出力される帰還信号の値が上げられて、制御電流源13から出力される電流が増加し、ゲート電圧の低下が抑制される。

【0047】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0048】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、微分器16によって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、電圧増幅器17から増幅された微分信号が出力されるとともに、制御電流源18によって、微分信号の値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0049】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源18によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0050】

第3の実施形態では、フライホイールダイオード10が完全にターンオフして、スイッチング素子7が急激にターンオフしてしまうのを防止するために、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値制限が制限され、制御電流源18によるゲート端子からの電流引き去りが制限される。電圧制限器32の制限値は制限電圧33によって設定されるが、この設定値としては、ゲートから排出する電流として通常必要となるレベルの電流を制御電流源18から出力するのに相当な値として選定するのが望ましい。

【0051】

このように、第3の実施形態では、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るとともに、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値を制限して、制限電流源18によるゲート端子からの電流引き去り動作を制限するようにしているので、スイッチング素子7のゲート容量を増大することなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定できるとともに、主電圧が一定値を超えたとき、ゲートからの電流排出動作を制限して、スイッチング素子7の電圧制御を再開することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0052】

また、第3の実施形態においても、第1の実施形態と同様に、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0053】

なお、図3では、電圧増幅器12の出力電圧値を制限しているが、実際に制限したいのは制御電流源18の出力であるから、制御電流源18において最大出力電流を制限するような構成を取ったり、あるいは、電圧増幅器17の入力において最大電圧を制限するような構成を取ることもまた可能である。

【0054】

《第4の実施形態》

図4は本発明によるスイッチング素子駆動回路の第4の実施形態を示す回路図である。なお、この図において、図1の各部に対応する部分には、同じ符号が付してある。

【0055】

図3に示した第3の実施形態では、制御電流源18の最大出力電流の値をある一定の値以上にしないことで、スイッチング素子7が急激にターンオフしてしまう不具合を解消するものであったが、スイッチング素子7が急激にターンオフする危険は、スイッチング素子7のコレクタ・エミッタ間電圧によって異なる。スイッチング素子7のコレクタ・エミッタ間電圧が低い場合には、大きな危険はないが、コレクタ・エミッタ間電圧が素子の耐圧に近づくにつれて危険は増大する。そこで、制御電流源18の最大出力電流の値をスイッチング素子7のコレクタ・エミッタ間電圧に応じて制限するようにすれば、より柔軟で応答性が高い制御系を得ることができる。これに対応するのが、図4に示す本発明の第4の実施形態である。

【0056】

第4の実施形態を図4に基づいて詳述すると、この図に示すスイッチング素子駆動回路41は、第1の実施形態と同様、正側ゲート駆動電源3と、負側ゲート駆動電源4と、ゲート抵抗6と、分圧器11と、電圧増幅器12と、制御電流源13と、微分器16と、電圧増幅器17とを備えている。

【0057】

さらに、スイッチング素子駆動回路41は、制御端子に入力される分圧器11からの帰還信号の値に応じて、入力される電圧増幅器17からの微分信号を制限して出力する電圧制限器32と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧制限器32から出力される微分信号に応じて、スイッチング素子7のゲート端子から電流を引き出し、接地ライン2に流す制御電流源18とを備えている。

【0058】

そして、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられ、これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0059】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器12から出力される帰還信号の値が上げられて、制御電流源13から出力される電流が増加し、ゲート電圧の低下が抑制される。

【0060】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0061】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、コンデンサ14と、抵抗15とによって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、電圧増幅器17から増幅された微分信号が出力されるとともに、制御電流源18によって、微分信号の値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0062】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源18によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0063】

次いで、フライホイールダイオード10が完全にターンオフして、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が予め設定された値になったとき、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値制限が開始され、制御電流源18によるゲート端子からの電流引き去りが制限される。

【0064】

このように、第4の実施形態では、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るとともに、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が予め設定されている設定値を超えたとき、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値を制限して、制限電流源18によるゲート端子からの電流引き去り動作を制限するようにしているので、スイッチング素子7のゲート容量を増大することなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定できるとともに、主電圧が一定値を超えたとき、ゲートからの電流排出動作を制限して、スイッチング素子7の電圧制御を再開することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0065】

また、第4の実施形態においても、第1の実施形態と同様に、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0066】

《第5の実施形態》

図5は本発明によるスイッチング素子駆動回路の第5の実施形態を示す回路図である。なお、この図において、図1の各部に対応する部分には、同じ符号が付してある。

【0067】

上述した各実施の形態では、スイッチング素子7のコレクタ・エミッタ間電圧の時間微分が小さい場合にも、比例した電流をゲートから排出するようにした。しかし、値が小さな時間微分についてはノイズとみなしてフィードバック制御をさせない方が良い。微分回路を使用した場合には、微分回路がノイズを拾って誤動作し易いことから、誤動作に強い回路構成を採用することが望ましい。そこで、第5の実施形態では、微分出力がある一定の値を上回るまでは電圧制限器の出力電圧をゼロに制限することで、細かいノイズによるフィードバック回路の誤動作を防止するようにしたものである。

【0068】

第5の実施形態を図5に基づいて詳述すると、この図に示すスイッチング素子駆動回路51は、第1の実施形態と同様、正側ゲート駆動電源3と、負側ゲート駆動電源4と、ゲート抵抗6と、分圧器11と、電圧増幅器12と、制御電流源13と、微分器16と、電圧増幅器17とを備えている。

【0069】

さらに、スイッチング素子駆動回路51は、制御端子に入力される微分器16からの微分信号の値に応じて、入力される電圧増幅器17からの微分信号を制限して出力する電圧制限器32と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧制限器32から出力される微分信号に応じて、スイッチング素子7のゲート端子から電流を引き出し、接地ライン2に流す制御電流源18とを備えている。

【0070】

そして、微分器16から出力される微分信号の値が予め設定されたノイズ弁別しきい値以下であるとき、ノイズなどに起因して、電圧増幅器17から誤った電圧信号が出力されても、電圧制限器32によって、これがカットされて、誤動作が防止される。

【0071】

また、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられ、これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0072】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器12から出力される帰還信号の値が上げられて、制御電流源13から出力される電流が増加し、ゲート電圧の低下が抑制される。

【0073】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0074】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、コンデンサ14と、抵抗15とによって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、電圧増幅器17から増幅された微分信号が出力される。

【0075】

そして、微分信号の値がノイズ弁別しきい値を超えたとき、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値制限が行われることなく、微分信号が制御電流源18に供給されて、制御電流源18によって、微分信号の値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0076】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源18によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0077】

このように、第5の実施形態では、微分器16から出力される微分信号の値が予め設定されたノイズ弁別しきい値以下であるとき、ノイズなどに起因して、電圧増幅器17から誤った電圧信号が出力されても、電圧制限器32によって、これがカットして、誤動作を防止しながら、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して得られた微分信号がノイズ弁別しきい値を超えたとき、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るようにしているので、スイッチング素子7のゲート容量を増大することなく、かつノイズなどに影響されることなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0078】

また、第5の実施形態においても、第1の実施形態と同様に、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0079】

《他の実施形態》

また、上述した第1の実施形態〜第5の実施形態では、スイッチング素子7として、IGBTを使用するようにしているが、制御対象となるスイッチング素子7として、MOSFETなどを使用するようにしても良い。

【図面の簡単な説明】

【0080】

【図1】本発明によるスイッチング素子駆動回路の第1の実施形態を示す回路図。

【図2】本発明によるスイッチング素子駆動回路の第2の実施形態を示す回路図。

【図3】本発明によるスイッチング素子駆動回路の第3の実施形態を示す回路図。

【図4】本発明によるスイッチング素子駆動回路の第4の実施形態を示す回路図。

【図5】本発明によるスイッチング素子駆動回路の第5の実施形態を示す回路図。

【図6】従来から知られているスイッチング素子駆動回路の一例を示す回路図。

【符号の説明】

【0081】

1,21,31,41,51:スイッチング素子駆動回路、2:接地ライン、3:正側ゲート駆動電源、4:負側ゲート駆動電源、5:電圧増幅器、6:ゲート抵抗、7:スイッチング素子、8,9:分圧抵抗、10:フライホイールダイオード、11:分圧器、12:電圧増幅器、13:制御電流源(注入側制御電流源、注入/排出共用制御電流源)、14:コンデンサ、15:抵抗、16:微分器(時間変化率検出器)、17:電圧増幅器、18:制御電流源(排出側制御電流源)

22,23,26,27:抵抗、24:分圧器、25:電圧増幅器、28:分圧器、32:電圧制御器、33:制御電圧。

【技術分野】

【0001】

本発明は、電力用スイッチング素子などを駆動するスイッチング素子駆動回路に係わり、特にどのような運転モードで運転したときにも、安定した性能を維持できるようにしたスイッチング素子駆動回路に関する。

【背景技術】

【0002】

電力変換装置などで使用されるIGBT、MOSFETなどのゲート型スイッチング素子では、近年、大容量化、高速化にともない、その応用範囲を着実に広げている。

【0003】

また、このようなIGBT、MOSFETなどのゲート型スイッチング素子は、オン状態、オフ状態を自己継続しないノンラッチング型のスイッチ素子であることから、サイリスタなどのラッチング型のスイッチング素子に比べて、ゲート駆動による高い制御性を持つという利点がある。また、「Angelo Raciti et al“Control of the Switching Transients of IGBT Series Strings by High-Performance Drive Units”,IEEE Transactions on Industrial Electronics,Vol.48,No.3,June 2001」などの文献(非特許文献)からも分かるように、ターンオフ/ターンオンのスイッチング過渡期においても、ゲート制御によって、サージ電圧やサージ電流を抑制したり、スイッチング過渡期の電流や電圧の傾きを自在に制御することができる。

【0004】

図6はこのようなゲート型スイッチング素子を駆動するスイッチング素子駆動回路の従来例を示す回路図である。

【0005】

この図に示すスイッチング素子駆動回路101は、正電圧側の電源として使用される正側ゲート駆動電源103と、負電圧側の電源として使用される負側ゲート駆動電源104と、図示しない制御装置から供給される制御信号を増幅して出力する電圧増幅器105と、電圧増幅器105から出力される制御信号の電流値を制限して制御対象となるスイッチング素子107のゲートに供給するゲート抵抗106と、分圧抵抗108及び分圧抵抗109によって構成され、フライホイールダイオード110が接続されたスイッチング素子107のコレクタ・エミッタ間電圧“Vce”を分圧して帰還信号を生成する分圧器111と、分圧器111からの帰還信号が設定値を超えているとき、これを増幅して出力する電圧増幅器112と、電圧増幅器112から出力される帰還信号に応じた電流を生成してスイッチング素子107のゲートに供給する制御電流源113とを備えている。

【0006】

そして、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器105から出力される制御信号の電圧が負側に振れると、ゲート抵抗106を介して、スイッチング素子107のゲート電圧が下がり始め、スイッチング素子107の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子107のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0007】

この後、スイッチング素子107のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めて、2つの分圧抵抗108、109の接続点からの帰還信号が予め設定されている設定値を超えたとき、電圧増幅器112から出力される帰還信号の値が上げられて、制御電流源113から出力される電流が増加してゲート電圧の低下が抑制される。

【0008】

これにより、スイッチング素子107の電流遮断時に、スイッチング素子107のコレクタ・エミッタ間電圧“Vce”が設定値を超えないようにすることができる。

【非特許文献1】Angelo Raciti et al“Control of the Switching Transients of IGBT Series Strings by High-Performance Drive Units”,IEEE Transactions on Industrial Electronics,Vol.48,No.3,June 2001

【発明の開示】

【発明が解決しようとする課題】

【0009】

ところが、従来のスイッチング素子駆動回路101では、スイッチング素子107のコレクタ・エミッタ間電圧“Vce”が設定値を超えるとき、コレクタ・エミッタ間電圧“Vce”を効果的に抑制できるものの、コレクタ・エミッタ間電圧“Vce”の時間変化率については、何らの考慮も払われていない。

【0010】

このため、スイッチング素子107のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいとき、スイッチング素子107のコレクタ、ゲート間に存在する内部帰還容量などにより、電圧増幅器105から出力される制御信号の電圧値より、スイッチング素子107のゲート電圧が高くなって、スイッチング素子107の動作が不安定になるという問題が発生していた。

【0011】

特に、スイッチング素子107のターンオフ特性に比べて、スイッチング素子107に並列に接続されているフライホイールダイオード110のターンオフ特性が急峻であることから、フライホイールダイオード110に流れていた電流がオフされたとき、逆回復時間を経過した後、フライホイールダイオード110自身の逆回復特性によって決まる時間変化率で、フライホイールダイオード110の電圧が急激に立ち上がり、スイッチング素子107の内部帰還容量を介し、ゲート電圧が持ち上げられ、本来、オフ状態になっていなければならないスイッチング素子107がオンしてしまうという現象がしばしば起こっていた。

【0012】

このようなゲート電圧の持ち上がりは、スイッチング素子107の予期せぬターンオンを引き起こすことがあることから、図6の回路図では、スイッチング素子107のゲート、エミッタ間にコンデンサ114を接続して、ゲート電圧を安定化するようにしている。

【0013】

しかしながら、このような対処方法では、内部帰還容量の影響を減殺できるものの、スイッチング素子駆動回路101側からみたスイッチング素子107のゲート容量が増大してしまうことから、応答性能が悪化してしまうという欠点が発生する。

【0014】

特に、極めて短い過渡期間にゲート電圧を制御して、スイッチング素子をスイッチングし、スイッチング素子の分担する主電圧を制御するアクティブゲート駆動技術を用いたスイッチング素子駆動回路などでは、ゲート駆動電流に対する応答性能の悪化がアクティブゲート駆動制御の性能悪化に直結してしまうという問題があった。

【0015】

本発明は上記の事情に鑑み、アクティブゲート駆動技術などを用いて、スイッチング素子を駆動した場合でも、高い応答性能を確保して、最大性能を出力できるスイッチング素子駆動回路を提供することを目的としている。

【課題を解決するための手段】

【0016】

上記の目的を達成するために本発明は、電圧増幅器によって、スイッチング素子のゲート端子に電圧信号を供給して、前記スイッチング素子の主電圧を制御するスイッチング素子駆動回路において、前記スイッチング素子の主電極間に印加される主電圧に応じて、前記ゲート端子に電流を注入する注入側制御電流源と、前記スイッチング素子の主電極間に印加される主電圧の時間変化率を検出して時間変化率検出信号を生成する時間変化率検出器と、この時間変化率検出器から出力される時間変化率検出信号に応じて、前記ゲート端子から電流を排出する排出側制御電流源とを備えたことを特徴としている。

【発明の効果】

【0017】

本発明によれば、スイッチング素子のゲート容量を増大することなく、フライホイールダイオードの電圧が急激に立ち上がり、スイッチング素子の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【発明を実施するための最良の形態】

【0018】

《第1の実施形態》

図1は本発明によるスイッチング素子駆動回路の第1の実施形態を示す回路図である。

【0019】

この図に示すスイッチング素子駆動回路1は、負電圧端子が接地ライン2に接続され、正電圧側の電源として使用される正側ゲート駆動電源3と、正電圧端子が接地ライン2に接続され、負電圧側の電源として使用される負側ゲート駆動電源4と、正側ゲート駆動電源3の正電圧端子から供給される正電圧、負側ゲート駆動電源4の負電圧端子から出力される負電圧を電源電圧として取り込み、図示しない制御装置などから供給される制御信号を増幅して出力する電圧増幅器5と、電圧増幅器5から出力される制御信号の電流値を制限してIGBTなどの制御対象となるスイッチング素子7のゲートに供給するゲート抵抗6と、スイッチング素子7のコレクタとエミッタ間に直列に接続された分圧抵抗8および分圧抵抗9によって構成され、フライホイールダイオード10が接続されたスイッチング素子7のコレクタ・エミッタ間電圧“Vce”を分圧して帰還信号を生成する分圧器11と、正側ゲート駆動電源3から供給される正電圧、負側ゲート駆動電源4から供給される負電圧を電源電圧として取り込み、分圧器11からの帰還信号が設定値を超えているとき、これを増幅して出力する電圧増幅器12と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3から供給される正電圧を電源電圧として取り込み、電圧増幅器12から出力される帰還信号に応じた電流を生成してスイッチング素子7のゲート端子に供給する制御電流源13とを備えている。

【0020】

さらに、スイッチング素子駆動回路1は、スイッチング素子7のコレクタとエミッタ間に直列に接続されたコンデンサ14および抵抗15によって構成され、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分し、コレクタ・エミッタ間電圧“Vce”の時間変化率を示す微分信号を生成する微分器16と、正側ゲート駆動電源3から供給される正電圧、負側ゲート駆動電源4から出力される負電圧を電源電圧として取り込み、微分器16からの微分信号を増幅して出力する電圧増幅器17と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧増幅器17から出力される微分信号に応じて、スイッチング素子7のゲート端子から電流を引き出して接地ライン2に流す制御電流源18とを備えている。

【0021】

そして、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられる。これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0022】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器12から出力される帰還信号の値が上昇して、制御電流源13から出力される電流が増加され、ゲート電圧の低下が抑制される。

【0023】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0024】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、微分器16によって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、電圧増幅器17から増幅された微分信号が出力されるとともに、制御電流源18によって、微分信号の値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0025】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源18によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0026】

このように、第1の実施形態では、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るようにしているので、スイッチング素子7のゲート容量を増大することなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0027】

また、第1の実施形態では、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0028】

《第2の実施形態》

図2は本発明によるスイッチング素子駆動回路の第2の実施形態を示す回路図である。なお、この図において、図1の各部に対応する部分には、同じ符号が付してある。

【0029】

この図に示すスイッチング素子駆動回路21は、図1と同様、正側ゲート駆動電源3と、負側ゲート駆動電源4と、電圧増幅器5と、ゲート抵抗6と、分圧器11と、微分器16とを備えている。

【0030】

また、第2の実施形態のスイッチング素子駆動回路21は、抵抗22,23によって構成され、分圧器11から出力される帰還信号をさらに分圧する分圧器24と、正側ゲート駆動電源3から供給される正電圧、負側ゲート駆動電源4から供給される負電圧を電源電圧として取り込み、非反転入力端子に供給される分圧器24からの帰還信号を非反転増幅して出力する電圧増幅器25と、一端がコンデンサ14と抵抗15との接続点に接続された抵抗26、一端が抵抗26の他端、電圧増幅器25の反転入力端子に接続され、他端が電圧増幅器25の出力側に接続された抵抗27によって構成され、電圧増幅器25から出力される帰還信号と微分器16から出力される微分信号との差信号を電圧増幅器25の反転入力端子に供給して、反転増幅する分圧器28と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧増幅器25から出力される帰還信号に応じて、スイッチング素子7のゲート端子に電流を供給する動作、またはスイッチング素子7のゲート端子から電流を引き去る動作を行う制御電流源13とを備えている。

【0031】

そして、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられ、これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0032】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器25から出力される帰還信号の値が上げられて、制御電流源13の電流出力が開始され、ゲート電圧の低下が抑制される。

【0033】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0034】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、微分器16によって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、分圧器28を介して、電圧増幅器25の反転入力端子に供給される。

【0035】

そして、電圧増幅器25の出力電圧は、分圧器28の分圧比と微分信号の電圧値とに応じた電圧値になるまで下げられるとともに、制御電流源13によって、電圧増幅器25の出力電圧値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0036】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源13によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0037】

この後、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が小さくなる従い、電圧増幅器25の出力電圧が元の電圧値まで、引き上げられるとともに、制御電流源13による、スイッチング素子7のゲート端子から電流の引き去り量が漸次、引き下げられる。

【0038】

このように、第2の実施形態では、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器25によって、前記微分信号を反転増幅して、制御電流源13を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るようにしているので、スイッチング素子7のゲート容量を増大することなく、かつ第1の実施形態のような制御電流源18を追加することなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0039】

また、第2の実施形態においても、第1の実施形態と同様に、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0040】

《第3の実施形態》

図3は本発明によるスイッチング素子駆動回路の第3の実施形態を示す回路図である。なお、この図において、図1の各部に対応する部分には、同じ符号が付してある。

【0041】

第1の実施形態、第2の実施形態では、ゲートから排出される電流の値に制限を設けていなかった。しかし、応用によっては、ゲートから排出される電流の値を制限したい場合もある。特にフライホイールダイオード10がすでにターンオフしてしまった後では、スイッチング素子7が自分自身で電圧を制御するモードに入るが、この場合はゲートから電流を排出するほどコレクタ・エミッタ間電圧の時間微分は大きくなることがあり、ゲートから排出される電流を制限しなければスイッチング素子7が急激にターンオフしてしまうことになる。

【0042】

本発明の第3の実施形態では、制御電流源18の最大出力電流の値をある一定の値以上にしないことで、スイッチング素子7が急激にターンオフしてしまう不具合を解消するものである。

【0043】

第3の実施形態を図3に基づいて詳述すると、この図に示すスイッチング素子駆動回路31は、第1の実施形態と同様、正側ゲート駆動電源3と、負側ゲート駆動電源4と、ゲート抵抗6と、分圧器11と、電圧増幅器12と、制御電流源13と、微分器16と、電圧増幅器17とを備えている。

【0044】

さらに、第3の実施形態のスイッチング素子駆動回路31は、制御端子に入力される制限電圧33の値に応じて、入力される電圧増幅器17からの微分信号を制限して出力する電圧制限器32と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧制限器32から出力される微分信号に応じて、スイッチング素子7のゲート端子から電流を引き出し、接地ライン2に流す制御電流源18とを備えている。

【0045】

そして、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられ、これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0046】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器12から出力される帰還信号の値が上げられて、制御電流源13から出力される電流が増加し、ゲート電圧の低下が抑制される。

【0047】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0048】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、微分器16によって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、電圧増幅器17から増幅された微分信号が出力されるとともに、制御電流源18によって、微分信号の値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0049】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源18によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0050】

第3の実施形態では、フライホイールダイオード10が完全にターンオフして、スイッチング素子7が急激にターンオフしてしまうのを防止するために、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値制限が制限され、制御電流源18によるゲート端子からの電流引き去りが制限される。電圧制限器32の制限値は制限電圧33によって設定されるが、この設定値としては、ゲートから排出する電流として通常必要となるレベルの電流を制御電流源18から出力するのに相当な値として選定するのが望ましい。

【0051】

このように、第3の実施形態では、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るとともに、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値を制限して、制限電流源18によるゲート端子からの電流引き去り動作を制限するようにしているので、スイッチング素子7のゲート容量を増大することなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定できるとともに、主電圧が一定値を超えたとき、ゲートからの電流排出動作を制限して、スイッチング素子7の電圧制御を再開することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0052】

また、第3の実施形態においても、第1の実施形態と同様に、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0053】

なお、図3では、電圧増幅器12の出力電圧値を制限しているが、実際に制限したいのは制御電流源18の出力であるから、制御電流源18において最大出力電流を制限するような構成を取ったり、あるいは、電圧増幅器17の入力において最大電圧を制限するような構成を取ることもまた可能である。

【0054】

《第4の実施形態》

図4は本発明によるスイッチング素子駆動回路の第4の実施形態を示す回路図である。なお、この図において、図1の各部に対応する部分には、同じ符号が付してある。

【0055】

図3に示した第3の実施形態では、制御電流源18の最大出力電流の値をある一定の値以上にしないことで、スイッチング素子7が急激にターンオフしてしまう不具合を解消するものであったが、スイッチング素子7が急激にターンオフする危険は、スイッチング素子7のコレクタ・エミッタ間電圧によって異なる。スイッチング素子7のコレクタ・エミッタ間電圧が低い場合には、大きな危険はないが、コレクタ・エミッタ間電圧が素子の耐圧に近づくにつれて危険は増大する。そこで、制御電流源18の最大出力電流の値をスイッチング素子7のコレクタ・エミッタ間電圧に応じて制限するようにすれば、より柔軟で応答性が高い制御系を得ることができる。これに対応するのが、図4に示す本発明の第4の実施形態である。

【0056】

第4の実施形態を図4に基づいて詳述すると、この図に示すスイッチング素子駆動回路41は、第1の実施形態と同様、正側ゲート駆動電源3と、負側ゲート駆動電源4と、ゲート抵抗6と、分圧器11と、電圧増幅器12と、制御電流源13と、微分器16と、電圧増幅器17とを備えている。

【0057】

さらに、スイッチング素子駆動回路41は、制御端子に入力される分圧器11からの帰還信号の値に応じて、入力される電圧増幅器17からの微分信号を制限して出力する電圧制限器32と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧制限器32から出力される微分信号に応じて、スイッチング素子7のゲート端子から電流を引き出し、接地ライン2に流す制御電流源18とを備えている。

【0058】

そして、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられ、これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0059】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器12から出力される帰還信号の値が上げられて、制御電流源13から出力される電流が増加し、ゲート電圧の低下が抑制される。

【0060】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0061】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、コンデンサ14と、抵抗15とによって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、電圧増幅器17から増幅された微分信号が出力されるとともに、制御電流源18によって、微分信号の値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0062】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源18によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0063】

次いで、フライホイールダイオード10が完全にターンオフして、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が予め設定された値になったとき、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値制限が開始され、制御電流源18によるゲート端子からの電流引き去りが制限される。

【0064】

このように、第4の実施形態では、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して、微分信号を生成するとともに、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るとともに、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が予め設定されている設定値を超えたとき、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値を制限して、制限電流源18によるゲート端子からの電流引き去り動作を制限するようにしているので、スイッチング素子7のゲート容量を増大することなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定できるとともに、主電圧が一定値を超えたとき、ゲートからの電流排出動作を制限して、スイッチング素子7の電圧制御を再開することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0065】

また、第4の実施形態においても、第1の実施形態と同様に、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0066】

《第5の実施形態》

図5は本発明によるスイッチング素子駆動回路の第5の実施形態を示す回路図である。なお、この図において、図1の各部に対応する部分には、同じ符号が付してある。

【0067】

上述した各実施の形態では、スイッチング素子7のコレクタ・エミッタ間電圧の時間微分が小さい場合にも、比例した電流をゲートから排出するようにした。しかし、値が小さな時間微分についてはノイズとみなしてフィードバック制御をさせない方が良い。微分回路を使用した場合には、微分回路がノイズを拾って誤動作し易いことから、誤動作に強い回路構成を採用することが望ましい。そこで、第5の実施形態では、微分出力がある一定の値を上回るまでは電圧制限器の出力電圧をゼロに制限することで、細かいノイズによるフィードバック回路の誤動作を防止するようにしたものである。

【0068】

第5の実施形態を図5に基づいて詳述すると、この図に示すスイッチング素子駆動回路51は、第1の実施形態と同様、正側ゲート駆動電源3と、負側ゲート駆動電源4と、ゲート抵抗6と、分圧器11と、電圧増幅器12と、制御電流源13と、微分器16と、電圧増幅器17とを備えている。

【0069】

さらに、スイッチング素子駆動回路51は、制御端子に入力される微分器16からの微分信号の値に応じて、入力される電圧増幅器17からの微分信号を制限して出力する電圧制限器32と、負電圧端子が接地ライン2に接続され、正側ゲート駆動電源3の正電圧端子から供給される正電圧を電源電圧として取り込み、電圧制限器32から出力される微分信号に応じて、スイッチング素子7のゲート端子から電流を引き出し、接地ライン2に流す制御電流源18とを備えている。

【0070】

そして、微分器16から出力される微分信号の値が予め設定されたノイズ弁別しきい値以下であるとき、ノイズなどに起因して、電圧増幅器17から誤った電圧信号が出力されても、電圧制限器32によって、これがカットされて、誤動作が防止される。

【0071】

また、スイッチング素子7に電流が流れている場合には、制御装置から供給される制御信号の電圧値が切り替えられて、電圧増幅器5から出力される制御信号の電圧が負電圧に切り替えられ、これによりゲート抵抗6を介して、スイッチング素子7のゲート電圧が下がり始め、スイッチング素子7の静特性によって一義的に決まるしきい値電圧を下回ったとき、スイッチング素子7のコレクタ・エミッタ間に流れていた電流の遮断が開始される。

【0072】

この後、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が上昇し、2つの分圧抵抗8、9の接続点から出力される帰還信号が予め設定されている設定値を超えたとき、電圧増幅器12から出力される帰還信号の値が上げられて、制御電流源13から出力される電流が増加し、ゲート電圧の低下が抑制される。

【0073】

これにより、スイッチング素子7の電流遮断時に、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が設定値以下にされる。

【0074】

また、フライホイールダイオード10に電流が流れている場合には、フライホイールダイオード10に流れていた電流が小さくなって、逆回復時間が過ぎ、フライホイールダイオード10自身の逆回復特性によって決まる時間変化率で、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”が急速に上昇し始めたとき、コンデンサ14と、抵抗15とによって、コレクタ・エミッタ間電圧“Vce”が微分されて、微分信号が生成され、電圧増幅器17から増幅された微分信号が出力される。

【0075】

そして、微分信号の値がノイズ弁別しきい値を超えたとき、電圧制限器32によって、電圧増幅器17から出力される微分信号の電圧値制限が行われることなく、微分信号が制御電流源18に供給されて、制御電流源18によって、微分信号の値に応じた電流値だけ、スイッチング素子7のゲート端子から電流が引き去られる。

【0076】

これにより、スイッチング素子7のコレクタ・エミッタ間に印加される主電圧の時間変化率が非常に大きいときでも、内部帰還容量を介して、ゲート端子側に帰還される電流(コレクタ・エミッタ間電圧“Vce”の微分値に比例した電流値となる電流)と、制御電流源18によって、ゲート端子から引き去られる電流とを相殺して、電圧増幅器5から出力される制御信号の電圧値より、スイッチング素子7のゲート電圧が高くならないようにする。

【0077】

このように、第5の実施形態では、微分器16から出力される微分信号の値が予め設定されたノイズ弁別しきい値以下であるとき、ノイズなどに起因して、電圧増幅器17から誤った電圧信号が出力されても、電圧制限器32によって、これがカットして、誤動作を防止しながら、スイッチング素子7のコレクタ端子、エミッタ端子に接続された微分器16によって、スイッチング素子7のコレクタ・エミッタ間電圧“Vce”を微分して得られた微分信号がノイズ弁別しきい値を超えたとき、電圧増幅器17によって、前記微分信号を増幅して、制御電流源18を制御し、内部帰還容量を介して、コレクタ側からゲート端子側に帰還される電流と対応する電流値分だけ、ゲート端子から電流を引き去るようにしているので、スイッチング素子7のゲート容量を増大することなく、かつノイズなどに影響されることなく、フライホイールダイオード10の電圧が急激に立ち上がり、スイッチング素子7の内部帰還容量を介し、ゲート側が持ち上げられたとき、ゲートから余分な電流を排出して、ゲート電圧を安定することができ、これによってアクティブゲート駆動技術などを用いて、スイッチング素子7を駆動した場合でも、高い応答性能を確保して、最大性能を出力できる。

【0078】

また、第5の実施形態においても、第1の実施形態と同様に、コンデンサ14と抵抗15とによって構成される簡単な微分器16によって、スイッチング素子7に印加される主電圧の時間変化率を検出するようにしているので、回路構成を簡素化して、コスト上昇を抑制できる。

【0079】

《他の実施形態》

また、上述した第1の実施形態〜第5の実施形態では、スイッチング素子7として、IGBTを使用するようにしているが、制御対象となるスイッチング素子7として、MOSFETなどを使用するようにしても良い。

【図面の簡単な説明】

【0080】

【図1】本発明によるスイッチング素子駆動回路の第1の実施形態を示す回路図。

【図2】本発明によるスイッチング素子駆動回路の第2の実施形態を示す回路図。

【図3】本発明によるスイッチング素子駆動回路の第3の実施形態を示す回路図。

【図4】本発明によるスイッチング素子駆動回路の第4の実施形態を示す回路図。

【図5】本発明によるスイッチング素子駆動回路の第5の実施形態を示す回路図。

【図6】従来から知られているスイッチング素子駆動回路の一例を示す回路図。

【符号の説明】

【0081】

1,21,31,41,51:スイッチング素子駆動回路、2:接地ライン、3:正側ゲート駆動電源、4:負側ゲート駆動電源、5:電圧増幅器、6:ゲート抵抗、7:スイッチング素子、8,9:分圧抵抗、10:フライホイールダイオード、11:分圧器、12:電圧増幅器、13:制御電流源(注入側制御電流源、注入/排出共用制御電流源)、14:コンデンサ、15:抵抗、16:微分器(時間変化率検出器)、17:電圧増幅器、18:制御電流源(排出側制御電流源)

22,23,26,27:抵抗、24:分圧器、25:電圧増幅器、28:分圧器、32:電圧制御器、33:制御電圧。

【特許請求の範囲】

【請求項1】

電圧増幅器によって、スイッチング素子のゲート端子に電圧信号を供給して、前記スイッチング素子の主電圧を制御するスイッチング素子駆動回路において、

前記スイッチング素子の主電極間に印加される主電圧に応じて、前記ゲート端子に電流を注入する注入側制御電流源と、

前記スイッチング素子の主電極間に印加される主電圧の時間変化率を検出して時間変化率検出信号を生成する時間変化率検出器と、

この時間変化率検出器から出力される時間変化率検出信号に応じて、前記ゲート端子から電流を排出する排出側制御電流源と、

を備えたことを特徴とするスイッチング素子駆動回路。

【請求項2】

電圧増幅器からスイッチング素子のゲート端子に電圧信号を供給して、前記スイッチング素子の主電圧を制御するスイッチング素子駆動回路において、

前記スイッチング素子の主電極間に印加される主電圧の時間変化率を検出して、時間変化率検出信号を生成する時間変化率検出器と、

この時間変化率検出器から出力される時間変化率検出信号、前記スイッチング素子の主電極間に印加される主電圧に応じて、前記ゲート端子に電流を注入、または排出する注入/排出共用制御電流源と、

を備えたことを特徴とするスイッチング素子駆動回路。

【請求項3】

請求項1、2のいずれかに記載のスイッチング素子駆動回路において、

前記スイッチング素子の主電極間に印加される主電圧が予め設定されている一定値を超えているとき、前記時間変化率検出器から出力される時間変化率検出信号の電圧値を制限する電圧制限器を備え、この電圧制限器から出力される時間変化率検出信号に応じて、前記排出側制御電流源、または前記注入/排出共用制御電流源のゲート電流の排出量を制御する、

ことを特徴とするスイッチング素子駆動回路。

【請求項4】

請求項1、2のいずれかに記載のスイッチング素子駆動回路において、

前記時間変化率検出器から出力される時間変化率検出信号が予め設定されているノイズ弁別しきい値を超えているとき、時間変化率検出信号を通過する電圧制限器を備え、この電圧制限器から出力される時間変化率検出信号に応じて、前記排出側制御電流源、または前記注入/排出共用制御電流源のゲート電流の排出量を制御する、

ことを特徴とするスイッチング素子駆動回路。

【請求項5】

請求項1乃至4のいずれか1項に記載のスイッチング素子駆動回路において、

前記時間変化率検出器は、直列に接続されたコンデンサと、抵抗とによって構成され、前記スイッチング素子の主電極間に並列に接続されて、前記スイッチング素子の主電極間に印加される主電圧を微分し、前記時間変化率検出信号を生成する、

ことを特徴とするスイッチング素子駆動回路。

【請求項1】

電圧増幅器によって、スイッチング素子のゲート端子に電圧信号を供給して、前記スイッチング素子の主電圧を制御するスイッチング素子駆動回路において、

前記スイッチング素子の主電極間に印加される主電圧に応じて、前記ゲート端子に電流を注入する注入側制御電流源と、

前記スイッチング素子の主電極間に印加される主電圧の時間変化率を検出して時間変化率検出信号を生成する時間変化率検出器と、

この時間変化率検出器から出力される時間変化率検出信号に応じて、前記ゲート端子から電流を排出する排出側制御電流源と、

を備えたことを特徴とするスイッチング素子駆動回路。

【請求項2】

電圧増幅器からスイッチング素子のゲート端子に電圧信号を供給して、前記スイッチング素子の主電圧を制御するスイッチング素子駆動回路において、

前記スイッチング素子の主電極間に印加される主電圧の時間変化率を検出して、時間変化率検出信号を生成する時間変化率検出器と、

この時間変化率検出器から出力される時間変化率検出信号、前記スイッチング素子の主電極間に印加される主電圧に応じて、前記ゲート端子に電流を注入、または排出する注入/排出共用制御電流源と、

を備えたことを特徴とするスイッチング素子駆動回路。

【請求項3】

請求項1、2のいずれかに記載のスイッチング素子駆動回路において、

前記スイッチング素子の主電極間に印加される主電圧が予め設定されている一定値を超えているとき、前記時間変化率検出器から出力される時間変化率検出信号の電圧値を制限する電圧制限器を備え、この電圧制限器から出力される時間変化率検出信号に応じて、前記排出側制御電流源、または前記注入/排出共用制御電流源のゲート電流の排出量を制御する、

ことを特徴とするスイッチング素子駆動回路。

【請求項4】

請求項1、2のいずれかに記載のスイッチング素子駆動回路において、

前記時間変化率検出器から出力される時間変化率検出信号が予め設定されているノイズ弁別しきい値を超えているとき、時間変化率検出信号を通過する電圧制限器を備え、この電圧制限器から出力される時間変化率検出信号に応じて、前記排出側制御電流源、または前記注入/排出共用制御電流源のゲート電流の排出量を制御する、

ことを特徴とするスイッチング素子駆動回路。

【請求項5】

請求項1乃至4のいずれか1項に記載のスイッチング素子駆動回路において、

前記時間変化率検出器は、直列に接続されたコンデンサと、抵抗とによって構成され、前記スイッチング素子の主電極間に並列に接続されて、前記スイッチング素子の主電極間に印加される主電圧を微分し、前記時間変化率検出信号を生成する、

ことを特徴とするスイッチング素子駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2006−25516(P2006−25516A)

【公開日】平成18年1月26日(2006.1.26)

【国際特許分類】

【出願番号】特願2004−200460(P2004−200460)

【出願日】平成16年7月7日(2004.7.7)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成18年1月26日(2006.1.26)

【国際特許分類】

【出願日】平成16年7月7日(2004.7.7)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]