テープ基板

【課題】半導体素子の性能を維持しつつ、小型化、及び設計の効率化が実現できる半導体装置及び基板を得る。

【解決手段】半導体素子12に対し、表示装置を駆動させる信号を出力する半導体素子内部出力部30A〜30Dの近傍にグランド端子電極52a及び電源端子電極52bを設ける一方、絶縁性フィルム18に対し、従来より半導体素子12の第1の辺に沿って設けられているグランド端子電極14a及び電源端子電極14bと、グランド端子電極52a及び電源端子電極52bとを接続する半導体素子上金属配線パターン54を設ける。

【解決手段】半導体素子12に対し、表示装置を駆動させる信号を出力する半導体素子内部出力部30A〜30Dの近傍にグランド端子電極52a及び電源端子電極52bを設ける一方、絶縁性フィルム18に対し、従来より半導体素子12の第1の辺に沿って設けられているグランド端子電極14a及び電源端子電極14bと、グランド端子電極52a及び電源端子電極52bとを接続する半導体素子上金属配線パターン54を設ける。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、テープ基板に関する。

【背景技術】

【0002】

一般的に液晶表示装置に搭載されるドライバは、半導体素子がテープで構成された基板上に封止された状態で表示装置に搭載される。近年の表示装置用ドライバでは、多階調化に伴ってデジタル信号をアナログ信号へ変換するD/A変換器が半導体素子内で占める割合が非常に大きくなっている。また、表示装置の大型化や、表示装置へ搭載するドライバ数の削減に伴って、一つ当たりのドライバの出力端子数が720本を超えるようになってきている。これらの要求に応えるために近年のドライバは、非常に多くの配線領域を半導体素子の内部に形成する必要があるため、半導体素子の面積が著しく大きくなってしまう、という問題を各社が抱えている。

【0003】

下記特許文献1には、半導体素子内の配線の増大、特に半導体素子の電気回路から外部へ信号を取り出す際に電気回路からバンプまで配線を張り巡らせなければならない課題に着目し、半導体装置の小型化及び軽量化を実現することを目的として、電気回路の出力である半導体素子の中央部に設けられた半導体素子表面バンプと、半導体素子外周部に設けられたバンプとを、基板上に設けられた配線パターンで接続する技術が開示されている。

【0004】

この技術によれば、半導体素子回路と配線パターンとの接続を接続用配線でも行うことができるため、表面又は内部で引き回していた配線を接続用配線で代用することができる結果、半導体素子の小型化及び軽量化を実現することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−80167号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記特許文献1に開示されている技術では、電気回路からの出力に対しての配線を減らすことは可能となるものの、表示装置用ドライバにおいては、出力端子間での出力AC特性のバラツキを非常に考慮する必要があり、特に半導体素子内部出力部に対して均一に電源電力を供給する必要がある。そのため、半導体素子の内部全体に引き回す電源配線及びグランド配線は、インピーダンスを低くするために太くする必要があり、この結果として更に半導体素子の面積が更に大きくなってしまう。したがって、上記問題を考慮した上で小型化、及び軽量化を実現することが必要である。

【0007】

また、表示装置用のドライバは、搭載する表示装置(表示パネル)のピン配置に応じて製造されるが、半導体素子上のピン配置と表示装置のピン配置が必ずしも一致しない場合がある。そういった場合には、既存の半導体素子を大幅に改良する必要性が生じてしまう。

【0008】

本発明は、上記問題点を解決するためになされたものであり、半導体素子の性能、特に電源供給能力を維持しつつ、小型化、及び設計の効率化が実現できるテープ基板を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、請求項1に記載のテープ基板は、複数の機能ブロックが配置された半導体素子を搭載する矩形の搭載領域と、前記搭載領域外周に規定される非搭載領域とを備え、表示装置を駆動する半導体素子搭載用のテープ基板であって、前記非搭載領域に設けられた外部入力端子と、前記非搭載領域に設けられた外部出力端子と、前記搭載領域の第1の辺に沿って設けられた複数の第1接続ノードと、前記搭載領域の第1の辺に対向する辺に沿って設けられた複数の第2接続ノードと、前記搭載領域であって、前記第1接続ノード及び前記第2接続ノードよりも内側、かつ前記機能ブロックの外周領域に対応する当該基板の領域に設けられた第3接続ノードと、前記外部入力端子と前記第1接続ノードを接続する第1配線パターンと、前記外部出力端子と前記第2接続ノードを接続する第2配線パターンと、前記複数の第1接続ノードと前記複数の第3接続ノードを接続し、前記第1配線パターンに接続された第3配線パターンと、前記第3配線パターンの前記第1接続ノードと前記第3接続ノードとの接続は少なくとも一部が前記非搭載領域を経由して接続されることを特徴とする。

【発明の効果】

【0010】

本発明のテープ基板によれば、半導体素子の性能、特に電源供給能力を維持しつつ、小型化、及び設計の効率化が実現できる、という効果が得られる。

【図面の簡単な説明】

【0011】

【図1】第1の実施の形態に係る半導体装置の全体構成を示す平面図である。

【図2】(A)は第1の実施の形態に係る半導体装置のグランド配線に関する部分の構成を示す平面図であり、(B)は第1の実施の形態に係る半導体装置の電源配線に関する部分の構成を示す平面図である。

【図3】第2の実施の形態に係る半導体装置の全体構成を示す平面図である。

【図4】(A)は第2の実施の形態に係る半導体装置のグランド配線に関する部分の構成を示す平面図であり、(B)は第2の実施の形態に係る半導体装置の電源配線に関する部分の構成を示す平面図である。

【図5】第3の実施の形態に係る半導体装置の全体構成を示す平面図である。

【図6】(A)は第3の実施の形態に係る半導体装置のグランド配線に関する部分の構成を示す平面図であり、(B)は第3の実施の形態に係る半導体装置の電源配線に関する部分の構成を示す平面図である。

【図7】第4の実施の形態に係る半導体装置の概略構成を示す平面図である。

【図8】第4の実施の形態に係る半導体装置の詳細構成を示す平面図である。

【図9】第4の実施の形態に係る半導体装置の変形例を示す平面図である。

【図10】第4の実施の形態に係る半導体装置の変形例を示す平面図である。

【図11】実施の形態に係る半導体装置の複数を組み合わせた場合の構成例を示す平面図である。

【発明を実施するための形態】

【0012】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

【0013】

[第1の実施の形態]

【0014】

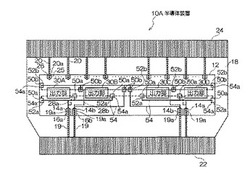

図1及び図2には、表示装置用ドライバとしてCOF(Chip On Film)法を適用して作製された、本実施の形態に係る半導体装置10Aの構成が示されている。なお、図1は半導体装置10Aの構成を示す平面図であり、図2(A)は半導体装置10Aのグランド配線に関する部分の構成を示す平面図であり、図2(B)は半導体装置10Aの電源配線に関する部分の構成を示す平面図である。

【0015】

図1及び図2に示されるように、この半導体装置10Aは、IC(Integrated Circuit)チップとして構成された半導体素子12と、基板として機能するフィルム(テープ)により構成された絶縁性フィルム18とを有しており、半導体素子12が絶縁性フィルム18に搭載されることにより構成されている。

【0016】

略矩形の半導体素子12には、当該半導体素子12の表面の第1の辺に沿って形成されたグランドレベル入力用の電極であるグランド端子電極(アルミパッド)14aと、グランド端子電極14aの表面上に設けられたAu(金)バンプ16aと、当該半導体素子12の上記第1の辺に沿って形成された電源入力用の電極である電源端子電極(アルミパッド)14bと、電源端子電極14bの表面上に設けられたAuバンプ16bとが備えられている。グランド端子電極14aと電源端子電極14bとを総称して第1電極14と呼ぶ。また、半導体素子12には、当該半導体素子12の上記第1の辺の対辺に沿って形成された信号出力用の電極であるドライバ出力端子電極(アルミパッド)25と、ドライバ出力端子電極25の表面上に設けられたAuバンプ26と、半導体素子内部グランド配線28aと、半導体素子内部電源配線28bと、上記第1の辺の対辺に沿って形成され、各々予め定められた表示装置を駆動させる信号を出力する半導体素子内部出力部30A〜半導体素子内部出力部30Dとが備えられている。半導体素子内部グランド配線28aと半導体素子内部電源配線28bを総称して内部電源配線28と呼ぶ。また、ドライバ出力端子電極25を第2電極25とも呼ぶ。なお、半導体素子内部グランド配線28a及び半導体素子内部電源配線28bは、半導体素子12の全般に設けられており、そのうち半導体素子内部出力部30近傍では上記第1の辺の対辺に沿っている。

【0017】

一方、絶縁性フィルム18には、半導体素子12が搭載される搭載領域と、搭載領域の外周に規定される非搭載領域が定義されている。ここで、半導体素子12が矩形であるため、ここで定義される搭載領域も矩形を意味する。特にドライバICの場合、長方形型であることがほとんどであり、以下、長辺の方向を長手方向と定義する。

【0018】

絶縁性フィルム18上には、ドライバICを制御する制御IC(例えばタイミングコントローラ等)からの信号が入力される入力側アウターリード(外部入力端子)22と、表示装置(LCDパネル等)へ搭載され信号を出力する出力側アウターリード(外部出力端子)24とが、非搭載領域に形成されている。

【0019】

また、絶縁性フィルム18上の搭載領域には、第1接続ノード19a、第2接続ノード20a、および第3接続ノード54aが形成されている。

【0020】

ここで、第1接続ノード19aは、矩形の搭載領域に規定される第1の辺に沿って設けられている。また、第2接続ノード20aは、上記第1の辺の対辺に沿って設けられている。さらに、第3接続ノード54aは、搭載領域において、第1接続ノード19aおよび第2接続ノード20aの内側に設けられている。本実施の形態では、第3接続ノード54aは第2接続ノード20a近傍に形成されているとも表現することができる。

【0021】

さらに絶縁性フィルム18上には、金属配線パターン(第1〜3接続パターン)19,20,54が形成されている。金属配線パターン19は、第1接続ノード19aと入力側アウターリード22を接続する。金属配線パターン20は、第2接続ノード20aと出力側アウターリード24を接続する。金属配線パターン54は、第1接続ノード19aと第3接続ノード54aを接続するものである。なお、各アウターリード、金属配線パターン及び接続ノードは、必要に応じて一体形成されるものである。

【0022】

ここで、Auバンプ16a,16b,26は、半導体素子12の外周に沿って設けられた電極14a,14b,25上に設けられており、半導体素子12が絶縁性フィルム18に搭載された状態において、金属配線パターン19,20、及び当該金属配線パターン19,20の一部に設けられた第1接続ノード19aまたは第2接続ノード20aを介して、Auバンプ16a,16bは入力側アウターリード22に、Auバンプ26は出力側アウターリード24に、各々電気的に接続される。このように、第1接続ノード19aは、半導体素子12に設けられたAuバンプ及び当該Auバンプが設けられた端子電極に電気的に接続されるものであるので、上記搭載領域に形成されると共に、半導体素子内部グランド配線28a又は半導体素子内部電源配線28bに電気的に接続される。

【0023】

また、半導体素子12では、各Auバンプの下に設けられた端子電極と、半導体素子12の内部回路とが、当該半導体素子12の内部配線により電気的に接続されている。

【0024】

また、グランド端子電極14aは半導体素子内部グランド配線28aに、電源端子電極14bは半導体素子内部電源配線28bに、各々電気的に接続されている。これにより、半導体素子内部グランド配線28a及び半導体素子内部電源配線28bは、第1接続ノード20a及び金属配線パターン20を介して入力側アウターリード22に電気的に接続されている。

【0025】

半導体装置10Aでは、入力側アウターリード22より信号を入力し、半導体素子12内において所定の変換を施した後、出力側アウターリード24より変換後の信号を出力する。なお、図1及び図2では、錯綜を回避するために、半導体素子12の内部回路(各機能ブロック)については半導体素子内部出力部30A〜半導体素子内部出力部30Dのみを図示し、その他の内部回路(例えば、ロジック部、レベル変換部、ラッチ部、DA変換部、階調電圧生成部等)の図示は省略している。

【0026】

また、半導体素子内部出力部30A〜半導体素子内部出力部30Dは一般的にオペアンプを主構成要素として構成される。以下、出力部を総称して半導体素子内部出力部30として、当該半導体素子内部出力部30について説明する。

【0027】

半導体素子内部出力部30は一般的に、対応するドライバ出力端子電極25の数と同等かそれ以上のオペアンプが設けられるものである。ドライバ出力端子電極25の数が非常に多いため、設計上、半導体素子内部出力部30A〜Dのようにブロックに分けられている。720チャネルの出力を有するドライバICの場合、4分割される結果、半導体素子内部出力部30Aは180チャネルに相当するオペアンプが設けられている。なお、正極及び負極の駆動を別々のオペアンプで行う場合は、チャネル数の数倍のオペアンプが形成されている場合もある。ここでは、上記オペアンプの集合体を一つの出力部として表している。半導体素子内部出力部30は、ドライバ出力端子電極25の近傍に設けられている。

【0028】

なお、半導体素子内部出力部30Bと半導体素子内部出力部30Cとの間は図面上、他の半導体素子内部出力部30間よりも広い空間が確保されているが、ここには、階調電圧生成回路等の各種機能ブロックが配置される。

【0029】

ここで、本実施の形態に係る半導体素子12には、その表面で、かつ半導体素子内部出力部30A〜30Dの近傍に、グランド端子電極52aと、電源端子電極52bとが形成されている。ここで、グランド端子電極52a上にはグランド用半導体素子表面Auバンプ50aが形成されており、電源端子電極52b上には電源用半導体素子表面Auバンプ50bが形成されている。なお、以下では、グランド端子電極52a及び電源端子電極52bを総称して第3電極52という。なお、上記半導体素子内部出力部の近傍とは、最も近くに存在する機能ブロックが半導体素子内部出力部である位置や、半導体内部出力部の外周に位置することを意味する。

【0030】

ここで、第3電極52は、ドライバ出力端子電極25の近傍に設けられているとも表現することが可能である。さらに言い換えると第3電極52は、半導体素子内部出力部30の外周に設けられている。また、場合によっては、半導体素子内部出力部30Aと半導体素子内部出力部30Bのブロック間に設けられることもある。ここで、第3電極52は、複数設けられている方が望ましい。複数の第3電極52は、それぞれ金属配線パターン54により、グランド端子電極52a間、あるいは電源端子電極52b間で共通接続される。第3電極52が複数設けられる位置としては、半導体素子12の中央部と、出力部30のブロック間、及び半導体素子12の表面の短辺に相当する側辺近傍等である。半導体素子12の長手方向の左右においてそれぞれ設けられることも望ましい。

【0031】

ここで、上記共通接続された金属配線パターン54は、長手方向に直線的に配置されている部分を有する。また、グランド端子電極52a間を共通接続した金属配線パターン54と、電源端子電極52b間を共通接続した金属配線パターン54は、半導体素子内部出力部30を挟むように配置されている。言い換えるとグランド端子電極52a間を共通接続した金属配線パターン54と、電源端子電極52b間を共通接続した金属配線パターン54との間に出力部30が位置する。さらに、共通接続した金属配線パターン54は、半導体素子内部グランド配線28a及び半導体素子内部電源配線28bの近傍に配置されている。なお、半導体素子内部グランド配線28a及び半導体素子内部電源配線28bも長手方向に延在して設けられている。

【0032】

第1電極であるグランド端子電極14a及び電源端子電極14bは、半導体素子12の上記第1の辺に沿って複数設けられている。言い換えると、長手方向において、上記第1の辺を2分割した左右にそれぞれグランド端子電極14a及び電源端子電極14bが設けられている。ここで、電源端子電極14bは、グランド端子電極14aよりも中央寄りに配置されている。また、電源端子電極14bと接続される金属配線パターン54は、半導体素子12の中央近傍を経由して、電源端子電極52b間を共通接続した金属配線パターン54と接続されている。

【0033】

更に、グランド端子電極14aとグランド端子電極52aは半導体素子内部グランド配線28aにより接続され、電源端子電極14bと電源端子電極52bは半導体素子内部電源配線28bにより接続されている。

【0034】

一方、絶縁性フィルム18には、半導体素子12が搭載された状態で、当該半導体素子12のAuバンプ16aとグランド用半導体素子表面Auバンプ50aとの間を電気的に接続すると共に、Auバンプ16bと電源用半導体素子表面Auバンプ50bとの間を電気的に接続する金属配線パターン54が形成されている。従って、半導体素子12が絶縁性フィルム18に搭載された状態で、金属配線パターン54の一部に設けられた第3接続ノード54aがグランド端子電極52a又は電源端子電極52bに電気的に接続される結果、グランド端子電極14aとグランド端子電極52a、及び電源端子電極14bと電源端子電極52bが電気的に接続される。なお、一般に、金属配線パターン54は、Cu(銅)等の比較的導電率の高い導電性物質により形成されるので、当該金属配線パターン54による抵抗は半導体素子の内部に形成されるアルミに比べて非常に低い。

【0035】

なお、本実施の形態に係る半導体装置10Aの製造は、一例として特許文献1に開示されている技術等、従来既知の技術により行うことができるため、ここでの説明は省略する。

【0036】

このように、本実施の形態によれば、半導体素子12の機能ブロック近傍に第3電極52を配置し、基板である絶縁フィルム18に設けられた入力側アウターリード22と接続された金属配線パターン19及び金属配線パターン54を設け、金属配線パターン54と第3電極52を接続することにより機能ブロックに均一に電源を供給することが可能となる。特に、精度が求められる半導体素子内部出力部30近傍に第3電極52を配置し、第3電極52と内部電源配線28とを接続することにより、第1電極14から内部電源配線28を介して出力部30へ電源を供給する経路と第3電極52から内部電源配線28を介して出力部30へ電源を供給する経路とを確保することができ、内部電源配線28の領域を減らしたとしても実質的に抵抗値を同等又は低減することが可能となる。よって内部電源配線28の低減による半導体素子12の面積を小さくすることと、半導体素子12の性能の維持とを実現することが可能となる。また、実質的に内部電源配線28の抵抗値の低減により発熱量を低減することができる。

【0037】

また、このとき、半導体素子12内の電源配線を削除することなく用いており、表示装置用ドライバとしての特性が変化することを抑制することができるため、当該特性の変化に対応するための各種調整が不要となる結果、効率的に設計することができる。

【0038】

また、電源端子電極52bに接続される金属配線パターン54を、ドライバ出力端子電極25の近傍及び半導体素子内部出力部30の近傍まで配置したことで、より効果的に電源電圧の変動を抑制することを可能とする。半導体素子12の左右においてそれぞれ上記構成を設け、さらに共通接続することで、より一層内部電源配線28の抵抗値を下げることを可能とし、均一に電源を供給できる効果が増す。金属配線パターン54を半導体素子12の中央部を経由させることにより、本実施の形態を実現可能とする。さらに半導体素子内部出力部30近傍に第3電極52を設け、金属配線パターン54で接続していることにより、特に発熱量が高い半導体素子内部出力部30の熱を伝導する役割が期待できる。

【0039】

なお、本実施の形態の構成を有する絶縁性フィルム18を用いることで効率的な設計を可能とする。

【0040】

[第2の実施の形態]

【0041】

図3及び図4には、表示装置用ドライバとしてCOF法を適用して作製された、本実施の形態に係る半導体装置10Bの構成が示されている。なお、図3は半導体装置10Bの構成を示す平面図であり、図4(A)は半導体装置10Bのグランド配線に関する部分の構成を示す平面図であり、図4(B)は半導体装置10Bの電源配線に関する部分の構成を示す平面図である。なお、図3及び図4における図1及び図2と同一の構成要素については図1及び図2と同一の符号を付して、その説明を省略する。

【0042】

半導体装置10Bには、当該半導体素子12の上記第1の辺に沿って形成された信号入力用の電極である第1接続端子62a及び第2接続端子62bと、第1接続端子62aの表面上に設けられたAu(金)バンプ60a及び第2接続端子62bの表面上に設けられたAu(金)バンプ60bとが備えられている。なお、第1接続端子62a及び第2接続端子62bは電源端子電極14bの近傍に設けられている。

【0043】

一方、絶縁性フィルム18上の搭載領域には、信号入力用接続ノード54bが形成されている。信号入力用接続ノード54bは、上記第1の辺に沿って設けられている。

【0044】

さらに絶縁性フィルム18上には、信号入力用接続ノード54bと入力用アウターリード22を接続する金属配線パターン19及び金属配線パターン54が形成されている。なお、入力アウターリード22、各金属配線パターン及び信号入力用接続ノード54bは、必要に応じて一体形成されるものである。

【0045】

ここで、Auバンプ60a及びAuバンプ60bは、半導体素子12の外周に沿って設けられた第1接続端子62a上及び第2接続端子62b上に設けられており、半導体素子12が絶縁性フィルム18に搭載された状態において、金属配線パターン19、金属配線パターン54、及び当該金属配線パターン54の一部に設けられた信号入力用接続ノード54bを介して入力側アウターリード22に電気的に接続される。このように、信号入力用接続ノード54bは、半導体素子12に設けられたAuバンプ60a,60b及び当該Auバンプが設けられた第1接続端子62a及び第2接続端子62bに電気的に接続されるものであるので、上記搭載領域に形成される。

【0046】

なお、半導体素子12では、各Auバンプ60a,60bの下に設けられた第1接続端子62a及び第2接続端子62bと、半導体素子12の内部回路とが、当該半導体素子12の内部配線により電気的に接続されている。

【0047】

また、半導体装置10Bでは、半導体素子の長手方向中央部より左側に、信号入力用接続ノード54bと入力用アウターリード22を接続する金属配線パターン19及び金属配線パターン54(以下、「左側入力信号配線パターン」という。)、第1接続端子62a、グランド端子電極52a、及び電源端子電極52bが配置されると共に、長手方向中央部より右側に、信号入力用接続ノード54bと入力用アウターリード22を接続する金属配線パターン19及び金属配線パターン54(以下、「右側入力信号配線パターン」という。)、第2接続端子62b、グランド端子電極52a、及び電源端子電極52bが配置されている。

【0048】

ここで、絶縁性フィルム18では、左側入力信号配線パターンと、入力アウターリード22と長手方向左側のグランド端子電極14a及び電源端子電極14bとを接続する金属配線パターンは列を成して配置されると共に、左側入力信号配線パターンが、入力アウターリード22と長手方向左側のグランド端子電極14a及び電源端子電極14bとを接続する金属配線パターンの外側(左側)に配置されている。また、右側入力信号配線パターンと、入力アウターリード22と長手方向右側のグランド端子電極14a及び電源端子電極14bとを接続する金属配線パターンは列を成して配置されると共に、右側入力信号配線パターンが、入力アウターリード22と長手方向右側のグランド端子電極14a及び電源端子電極14bとを接続する金属配線パターンの外側(右側)に配置されている。

【0049】

また、第1接続端子62a及び第2接続端子62bは、共にグランド端子電極14a及び電源端子電極14bよりも上記第1の辺の中央部側に配置されており、左側入力信号配線パターンは、上記第1の辺から見て、長手方向左側のグランド端子電極14a及び電源端子電極14bよりも外側(左側)に配置されており、右側入力信号配線パターンは、上記第1の辺から見て、長手方向右側のグランド端子電極14a及び電源端子電極14bよりも外側(右側)に配置されている。

【0050】

ここで、絶縁性フィルム18では、長手方向左側のグランド端子電極14aとグランド端子電極52aとを接続する金属配線パターン(以下、「左側グランド配線パターン」という。)と、長手方向左側の電源端子電極14bと電源端子電極52bとを接続する金属配線パターン(以下、「左側電源配線パターン」という。)が、左側入力信号配線パターンを迂回するように配置される一方、長手方向右側のグランド端子電極14aとグランド端子電極52aとを接続する金属配線パターン(以下、「右側グランド配線パターン」という。)と、長手方向右側の電源端子電極14bと電源端子電極52bとを接続する金属配線パターン(以下、「右側電源配線パターン」という。)が、右側入力信号配線パターンを迂回するように配置されている。

【0051】

また、絶縁性フィルム18では、左側グランド配線パターン及び左側電源配線パターンによるインピーダンスと、右側グランド配線パターン及び右側電源配線パターンによるインピーダンスとが互いに等しくなるように調整されている。

【0052】

なお、図3及び図4(B)に示されるように、左側電源配線パターンを構成する金属配線パターン19と金属配線パターン54、及び右側電源配線パターンを構成する金属配線パターン19と金属配線パターン54は、一部で一体形成されると共に、上記非搭載領域上を経由して電源端子電極52bに接続されている。

【0053】

このように、本実施の形態の構成をとることで、第1の実施の形態の効果に加えて、既存のドライバICのピン配置と搭載パネル側のピン配置が異なる場合でも、基板の設計のみで対応することが可能となる。言い換えると、従来の半導体素子12のレイアウト設計等にかかっていた時間に比較して、設計にかかる時間を格段に短くすることが可能となる。特に、左側グランド配線パターン及び左側電源配線パターンが第1接続端子62a及び左側入力信号配線パターンを迂回し、右側グランド配線パターン及び右側電源配線パターンが第2接続端子62b及び右側入力信号配線パターンを迂回することで、グランド端子電極52a及び電源端子電極52bとの接続が可能となる。また、半導体素子12の左右で、それぞれ左側グランド配線パターン及び左側電源配線パターンによるインピーダンスと、右側グランド配線パターン及び右側電源配線パターンによるインピーダンスを揃えたことで、左右で均一に電源供給することを可能とし、ピン間のばらつきを、より一層低減することを可能とする。

【0054】

[第3の実施の形態]

【0055】

図5及び図6には、表示装置用ドライバとしてCOF法を適用して作製された、本実施の形態に係る半導体装置10Cの構成が示されている。なお、図5は半導体装置10Cの構成を示す平面図であり、図6(A)は半導体装置10Cのグランド配線に関する部分の構成を示す平面図であり、図6(B)は半導体装置10Cの電源配線に関する部分の構成を示す平面図である。なお、図5及び図6における図1及び図2と同一の構成要素については図1及び図2と同一の符号を付して、その説明を省略する。

【0056】

本実施の形態に係る半導体装置10Cでは、グランド端子電極14a及び電源端子電極14bが、上記第1の辺に沿って交互に配置されている。詳細に説明すると、グランド端子電極14aと電源端子電極14bは、2つが隣り合って配置される。隣り合って配置されるグランド端子電極14aと電源端子電極14bを一組の電源電極対15とすると、第1の辺の中央部から左右にそれぞれ2組の電源電極対15が配置される。一組のグランド端子電極14aと電源端子電極14bは、グランド端子電極14aより電源端子電極14bの方が第1の辺の中央部に近く配置されている。左右のそれぞれ2組の電源電極対15間は、他の電極が形成されてもよい。例えば基準電圧が入力される電極等である。

【0057】

ここで、本実施の形態に係る絶縁性フィルム18では、グランド端子電極14aとグランド端子電極52aとを接続する金属配線パターンが半導体内部出力部30の外周を囲うように配置されると共に、電源端子電極14bと電源端子電極52bとを接続する金属配線パターンが半導体内部出力部30の外周を囲うように配置されている。詳細には、半導体素子12の長手方向における左右において、金属配線パターンはそれぞれ3つの部分から構成される。例えば、半導体素子12の左側部分を例に説明する。第2電極25と第3電極52間に形成され、第2電極25近傍に長手方向に直線的に形成された金属配線パターン54の第1部分31と、半導体素子12の長手方向において左側に配置された2組の電源電極対15のうち、第1の辺の中央部17寄りのグランド端子電極14aと半導体素子12の中央部17を経由して第1部分31と接続される第2部分32と、半導体素子12の長手方向において左側に配置された2組の電源電極対15のうち他方であるグランド端子電極14aが搭載領域から非搭載領域を経由して第1部分31と接続される第3部分33から金属配線パターンは構成される。前述の第1〜3部分を総合すると出力部30の外周を囲うように配置されている。なお、半導体素子12の右側部分も同様に3つの部分から構成され、左右それぞれの第1部分31は共通接続されている。

【0058】

このように、本実施の形態をとることで、半導体素子12の左右においてそれぞれ2組の電源電極対を有するピン配置であっても、第1の実施の形態の効果を得ることを可能とする。また、グランド端子電極14aとグランド端子電極52aとを接続する金属配線パターンが半導体内部出力部30の外周を囲うように配置されると共に、電源端子電極14bと電源端子電極52bとを接続する金属配線パターンが半導体内部出力部30の外周を囲うように配置されているので、均一に電源供給することを可能とし、ピン間のばらつきを、より一層低減することを可能とする。

【0059】

[第4の実施の形態]

【0060】

図7には、表示装置用ドライバとしてCOF法を適用して作製された、本実施の形態に係る半導体装置10Dの概略構成が示されている。なお、同図における図1と同一の構成要素には図1と同一の符号を付して、その説明を省略する。

【0061】

同図に示されるように、本実施の形態に係る半導体装置10Dは、半導体素子12の長手方向の略中央部に電圧生成部90が設けられている。

【0062】

この電圧生成部90は、入力側アウターリード22と、抵抗ラダー用接続パターン21及び金属パターン54とを介して印加された基準電圧間を抵抗ラダーによって分圧することにより、複数の階調電圧を生成するものである。

【0063】

ここで、本実施の形態に係る半導体装置10Dでは、半導体素子12の周辺部に抵抗ラダー用の端子電極を設けることなく、抵抗ラダーの近傍に端子電極を設ける一方、絶縁性フィルム18に対し、当該端子電極と入力側アウターリード22とを、抵抗ラダー用接続パターン21及び金属パターン54を介して直接接続している。このため、半導体素子12の周辺部に抵抗ラダー用の端子電極を設ける場合に比較して、半導体素子12を小型化することができる。

【0064】

なお、同図におけるデコーダ31A〜31Dは、各々半導体素子内部出力部30A〜半導体素子内部出力部30Dの何れか1つと1対1で対応し、電圧生成部90によって生成された階調電圧を用いて、対応する半導体素子内部出力部で適用する信号を生成するものである。

【0065】

図8には、電圧生成部90の詳細構成が示されている。なお、同図における図1と同一の構成要素には図1と同一の符号を付して、その説明を省略する。

【0066】

同図に示されるように、電圧生成部90には、各々予め定められた位置に配置された4つの抵抗器80a,80b,80c,80dが直列接続されて構成され、当該半導体素子12から表示装置に対して出力する出力電圧の基準となる階調電圧を生成する抵抗ラダー80が備えられている。

【0067】

ここで、電圧生成部90には、抵抗ラダー80の近傍に形成された5つの抵抗ラダー用電極82a,82b,82c,82d,82eが備えられている。また、電圧生成部90には、抵抗ラダー用電極82a及び抵抗ラダー用電極82eと抵抗ラダー80の上記直列接続の端部とを接続する半導体素子内部配線86と、抵抗ラダー用電極82b〜82dと抵抗ラダー80の上記直列接続の中間接続部とを接続する半導体素子内部配線88とが備えられている。なお、抵抗ラダー用電極82aの表面上にはAu(金)バンプ84aが、抵抗ラダー用電極82bの表面上にはAuバンプ84bが、抵抗ラダー用電極82cの表面上にはAuバンプ84cが、抵抗ラダー用電極82dの表面上にはAuバンプ84dが、抵抗ラダー用電極82eの表面上にはAuバンプ84eが、各々設けられている。

【0068】

一方、絶縁性フィルム18には、上記搭載領域に形成され、対応する抵抗ラダー用電極82a,82b,82c,82d,82eに接続される抵抗ラダー用接続ノード21aと、上記非搭載領域から上記搭載領域にわたって形成され、入力側アウターリード22と抵抗ラダー用接続ノード21aとを接続する抵抗ラダー用接続パターン21及び金属配線パターン54とが備えられている。

【0069】

半導体装置10Dでは、入力側アウターリード22より信号を入力し、半導体素子12内において所定の変換を施した後、出力側アウターリード24より変換後の信号を出力する。なお、図8では、錯綜を回避するために、半導体素子12の内部回路については抵抗ラダー80のみを図示し、その他の内部回路(例えば、ロジック部、レベル変換部、ラッチ部、DA変換部、階調電圧生成部等の図示は省略している。

【0070】

このように、本実施の形態によれば、Auバンプ84a〜84e、及びその下に各々設けられる抵抗ラダー用電極82a〜82eを、各々に接続される抵抗ラダー80の近傍に配置し、入力側アウターリード22とAuバンプ84a〜84eの接続状態を変化させないように半導体素子上金属配線パターン54を回り込むように配線しているので、抵抗ラダー80とAuバンプ84a〜84eの物理的距離を縮め、半導体素子内部配線86及び半導体素子内部配線88のインピーダンスを低下させることができる結果、半導体素子内部配線86及び半導体素子内部配線88の配線領域を縮小することができる。要するに、半導体素子12の面積を小さくすることができる。言い換えれば、半導体素子内部出力部30より出力される電圧の基となる電圧を生成する電圧生成部90に入力される基準電圧を、より変動のない形で供給することを可能とし、更には、半導体素子内部の配線領域の縮小に寄与することで、半導体素子の面積を縮小することができる。

【0071】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。発明の要旨を逸脱しない範囲で上記実施の形態に多様な変更または改良を加えることができ、当該変更または改良を加えた形態も本発明の技術的範囲に含まれる。

【0072】

また、上記の実施の形態は、クレーム(請求項)にかかる発明を限定するものではなく、また実施の形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。前述した実施の形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜の組み合わせにより種々の発明を抽出できる。実施の形態に示される全構成要件から幾つかの構成要件が削除されても、効果が得られる限りにおいて、この幾つかの構成要件が削除された構成が発明として抽出され得る。

【0073】

例えば、上記第4の実施の形態では、本発明の半導体装置の一例として図8に示される半導体装置10Dを適用した場合について説明したが、本発明はこれに限定されるものではなく、例えば、図9に示される半導体装置10Eや、図10に示される半導体装置10Fを適用することもできる。図10では、図8や図9とは異なって、基準電圧入力電極83が設けられている。望ましくは設けられない方が、基準電圧入力電極83を設けるための領域を確保する必要がなく、面積が少なくすむが、必要に応じて設けることを排除するものではないことを説明する図でもある。なお、図9及び図10では、図8に示されるものと同一の役割を有するものには図8と同一の符号を付している。これらの場合にも、上記第4の実施の形態と同様の効果を奏することができる。

【0074】

また、上記第1の実施の形態〜第4の実施の形態は、組み合わせて適用することができることは言うまでもない。

【0075】

図11には、上記第3の実施の形態と上記第4の実施の形態を組み合わせた場合の半導体装置の構成例が示されている。図11では、テープ基板を図示していないが、図上に記載された配線はすべてテープ基板上に形成されているものである。

【0076】

同図に示されるように、この構成例では、電圧生成部90として、電圧生成部90A及び電圧生成部90Bの2つが設けられている。電圧生成部90の詳細は図8〜10に示された内容である。電圧生成部90Aと電圧生成部90Bとの間の領域92は、出力部30や電圧生成部90を除く他の機能ブロックが配置される領域である。

【0077】

ここで、半導体素子内部出力部30A〜DはそれぞれPチャネルMOS−FETにより構成されたPデコーダとNチャネルMOS−FETにより構成されたNデコーダのいずれかで選択された階調電圧を出力する。そして、電圧生成部90Aは上記PチャネルMOS−FETにより構成されたデコーダに入力する階調電圧を生成するものとされており、電圧生成部90Bは上記PチャネルMOS−FETにより構成されたデコーダに入力する階調電圧を生成するものとされている。

【0078】

一般に、8ビット(256階調)の表示が可能なドライバであれば、電圧生成部90A及び電圧生成部90Bで、それぞれ256階調分の電圧が生成されており、各々に基準電圧が9個或いは11個程度供給される。

【0079】

また、この半導体素子12には、第1の辺に沿って、出力用電極形成領域98A、入力用電極形成領域98B、及び入力用電極非形成領域98Cの3つの領域が設けられている。入力用電極非形成領域98Cは、入力用電極形成領域98B間に設けられるものである。特に入力用電極形成領域98Bに設けられた第1電極(グランド端子電極又は電源端子電極)間に入力用電極非形成領域98Cは設けられる。この場合、入力用電極非形成領域98Cに対応する基板上の領域を介して、入力側アウターリードと抵抗ラダー用電極82とを、金属配線パターン54(VGMA)で接続することになる。

【0080】

また、図11に示す金属配線パターン54は特徴的な形状をしている。特に電源端子電極14aと電源端子電極52とを接続する金属配線パターン54(Vdd)について以下にその構造を説明する。金属配線パターン54(Vdd)は、出力部30の近傍に配置された電源端子電極52それぞれを共通接続する共通接続部94と、電源端子電極14aと共通接続部94とを接続し、内部電源配線のインピーダンスを調整するインピーダンス調整部96とから構成される。インピーダンス調整部96は、共通接続部94との接続を最短距離で結ばず、半導体素子12の角部から最も近い電源端子電極52aに近づくように共通接続部94と接続される。言い換えると、出力部30のうち半導体素子12の長手方向における端部の出力部30D(又は半導体素子12の左側の場合出力部30A)に近づくように共通接続部94と接続される。本構成をとることにより、出力部30Cと出力部30Dとの電源の均一性をさらに高く保つことが可能となる。

【0081】

なお、第1の実施の形態と第4の実施の形態を、同図に示されるように組み合わせた場合には、半導体素子12の左右にそれぞれ配置された2個の電源電極対のいずれか一方を使用して第1の実施の形態に相当する配線パターン54を配置することで実現が可能である。

【0082】

同様に、上記第1の実施の形態〜第3の実施の形態の複数を組み合わせて適用することもできる。これらの場合、組み合わせた実施の形態によって奏することのできる全ての効果を得ることができる。

【0083】

また、上記各実施の形態における各種Auバンプの数は一例であり、他の数とすることができることも言うまでもない。この場合も、上記各実施の形態と同様の効果を奏することができる。

【0084】

また、上記各実施の形態では、対象とする表示装置を特に限定しなかったが、当該表示装置として、液晶ディスプレイ装置、プラズマ・ディスプレイ装置、有機ELディスプレイ装置等の各種ディスプレイ装置に適用することができる。

【0085】

また、上記各実施の形態では、バンプの材質としてAuを適用した場合について説明したが、他の金属を適用することができることも言うまでもない。

【0086】

また、上記第1〜第3の実施の形態では、半導体素子内部出力部を半導体素子内部出力部30A〜30Dの4つのブロックに分けた場合について説明したが、本発明はこれに限定されるものではなく、他の数のブロックに分ける形態とすることができることも言うまでもない。この場合も、上記各実施の形態と同様の効果を奏することができる。

【0087】

また、上記第4の実施の形態では、抵抗ラダーを4つのブロックに分けた場合について説明したが、本発明はこれに限定されるものではなく、他の数のブロックに分ける形態とすることができることも言うまでもない。この場合も、上記第4の実施の形態と同様の効果を奏することができる。

【符号の説明】

【0088】

10A〜10G 半導体装置

12 半導体素子

14a グランド端子電極(第1電極,第1グランド電極)

14b 電源端子電極(第1電極,第1電源電極)

16a Auバンプ

16b Auバンプ

18 絶縁性フィルム(基板)

19 金属配線パターン(第1配線パターン)

19a 第1接続ノード

20 金属配線パターン(第2接続パターン)

20a 第2接続ノード

21 抵抗ラダー用接続パターン

21a 抵抗ラダー用接続ノード

22 入力側アウターリード(外部入力端子)

24 出力側アウターリード(外部出力端子)

25 ドライバ出力端子電極(第2電極)

26 Auバンプ

28a 半導体素子内部グランド配線(グランド配線)

28b 半導体素子内部電源配線(電源配線)

30A〜30D 半導体素子内部出力部(出力部)

50a グランド用半導体素子表面Auバンプ

50b 電源用半導体素子表面Auバンプ

52a グランド端子電極(第3電極,第2グランド電極)

52b 電源端子電極(第3電極,第2電源電極)

54 金属配線パターン(第3配線パターン,入力信号配線パターン)

54a 第3接続ノード

54b 信号入力用接続ノード(信号入力ノード)

62a 第1接続端子(信号入力電極)

62b 第2接続端子(信号入力電極)

80 抵抗ラダー

80a〜80d 抵抗器

82a〜82e 抵抗ラダー用電極

84a〜84e Auバンプ

86 半導体素子内部配線(端部用接続配線)

88 半導体素子内部配線(中間部用接続配線)

【技術分野】

【0001】

本発明は、テープ基板に関する。

【背景技術】

【0002】

一般的に液晶表示装置に搭載されるドライバは、半導体素子がテープで構成された基板上に封止された状態で表示装置に搭載される。近年の表示装置用ドライバでは、多階調化に伴ってデジタル信号をアナログ信号へ変換するD/A変換器が半導体素子内で占める割合が非常に大きくなっている。また、表示装置の大型化や、表示装置へ搭載するドライバ数の削減に伴って、一つ当たりのドライバの出力端子数が720本を超えるようになってきている。これらの要求に応えるために近年のドライバは、非常に多くの配線領域を半導体素子の内部に形成する必要があるため、半導体素子の面積が著しく大きくなってしまう、という問題を各社が抱えている。

【0003】

下記特許文献1には、半導体素子内の配線の増大、特に半導体素子の電気回路から外部へ信号を取り出す際に電気回路からバンプまで配線を張り巡らせなければならない課題に着目し、半導体装置の小型化及び軽量化を実現することを目的として、電気回路の出力である半導体素子の中央部に設けられた半導体素子表面バンプと、半導体素子外周部に設けられたバンプとを、基板上に設けられた配線パターンで接続する技術が開示されている。

【0004】

この技術によれば、半導体素子回路と配線パターンとの接続を接続用配線でも行うことができるため、表面又は内部で引き回していた配線を接続用配線で代用することができる結果、半導体素子の小型化及び軽量化を実現することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−80167号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記特許文献1に開示されている技術では、電気回路からの出力に対しての配線を減らすことは可能となるものの、表示装置用ドライバにおいては、出力端子間での出力AC特性のバラツキを非常に考慮する必要があり、特に半導体素子内部出力部に対して均一に電源電力を供給する必要がある。そのため、半導体素子の内部全体に引き回す電源配線及びグランド配線は、インピーダンスを低くするために太くする必要があり、この結果として更に半導体素子の面積が更に大きくなってしまう。したがって、上記問題を考慮した上で小型化、及び軽量化を実現することが必要である。

【0007】

また、表示装置用のドライバは、搭載する表示装置(表示パネル)のピン配置に応じて製造されるが、半導体素子上のピン配置と表示装置のピン配置が必ずしも一致しない場合がある。そういった場合には、既存の半導体素子を大幅に改良する必要性が生じてしまう。

【0008】

本発明は、上記問題点を解決するためになされたものであり、半導体素子の性能、特に電源供給能力を維持しつつ、小型化、及び設計の効率化が実現できるテープ基板を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、請求項1に記載のテープ基板は、複数の機能ブロックが配置された半導体素子を搭載する矩形の搭載領域と、前記搭載領域外周に規定される非搭載領域とを備え、表示装置を駆動する半導体素子搭載用のテープ基板であって、前記非搭載領域に設けられた外部入力端子と、前記非搭載領域に設けられた外部出力端子と、前記搭載領域の第1の辺に沿って設けられた複数の第1接続ノードと、前記搭載領域の第1の辺に対向する辺に沿って設けられた複数の第2接続ノードと、前記搭載領域であって、前記第1接続ノード及び前記第2接続ノードよりも内側、かつ前記機能ブロックの外周領域に対応する当該基板の領域に設けられた第3接続ノードと、前記外部入力端子と前記第1接続ノードを接続する第1配線パターンと、前記外部出力端子と前記第2接続ノードを接続する第2配線パターンと、前記複数の第1接続ノードと前記複数の第3接続ノードを接続し、前記第1配線パターンに接続された第3配線パターンと、前記第3配線パターンの前記第1接続ノードと前記第3接続ノードとの接続は少なくとも一部が前記非搭載領域を経由して接続されることを特徴とする。

【発明の効果】

【0010】

本発明のテープ基板によれば、半導体素子の性能、特に電源供給能力を維持しつつ、小型化、及び設計の効率化が実現できる、という効果が得られる。

【図面の簡単な説明】

【0011】

【図1】第1の実施の形態に係る半導体装置の全体構成を示す平面図である。

【図2】(A)は第1の実施の形態に係る半導体装置のグランド配線に関する部分の構成を示す平面図であり、(B)は第1の実施の形態に係る半導体装置の電源配線に関する部分の構成を示す平面図である。

【図3】第2の実施の形態に係る半導体装置の全体構成を示す平面図である。

【図4】(A)は第2の実施の形態に係る半導体装置のグランド配線に関する部分の構成を示す平面図であり、(B)は第2の実施の形態に係る半導体装置の電源配線に関する部分の構成を示す平面図である。

【図5】第3の実施の形態に係る半導体装置の全体構成を示す平面図である。

【図6】(A)は第3の実施の形態に係る半導体装置のグランド配線に関する部分の構成を示す平面図であり、(B)は第3の実施の形態に係る半導体装置の電源配線に関する部分の構成を示す平面図である。

【図7】第4の実施の形態に係る半導体装置の概略構成を示す平面図である。

【図8】第4の実施の形態に係る半導体装置の詳細構成を示す平面図である。

【図9】第4の実施の形態に係る半導体装置の変形例を示す平面図である。

【図10】第4の実施の形態に係る半導体装置の変形例を示す平面図である。

【図11】実施の形態に係る半導体装置の複数を組み合わせた場合の構成例を示す平面図である。

【発明を実施するための形態】

【0012】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

【0013】

[第1の実施の形態]

【0014】

図1及び図2には、表示装置用ドライバとしてCOF(Chip On Film)法を適用して作製された、本実施の形態に係る半導体装置10Aの構成が示されている。なお、図1は半導体装置10Aの構成を示す平面図であり、図2(A)は半導体装置10Aのグランド配線に関する部分の構成を示す平面図であり、図2(B)は半導体装置10Aの電源配線に関する部分の構成を示す平面図である。

【0015】

図1及び図2に示されるように、この半導体装置10Aは、IC(Integrated Circuit)チップとして構成された半導体素子12と、基板として機能するフィルム(テープ)により構成された絶縁性フィルム18とを有しており、半導体素子12が絶縁性フィルム18に搭載されることにより構成されている。

【0016】

略矩形の半導体素子12には、当該半導体素子12の表面の第1の辺に沿って形成されたグランドレベル入力用の電極であるグランド端子電極(アルミパッド)14aと、グランド端子電極14aの表面上に設けられたAu(金)バンプ16aと、当該半導体素子12の上記第1の辺に沿って形成された電源入力用の電極である電源端子電極(アルミパッド)14bと、電源端子電極14bの表面上に設けられたAuバンプ16bとが備えられている。グランド端子電極14aと電源端子電極14bとを総称して第1電極14と呼ぶ。また、半導体素子12には、当該半導体素子12の上記第1の辺の対辺に沿って形成された信号出力用の電極であるドライバ出力端子電極(アルミパッド)25と、ドライバ出力端子電極25の表面上に設けられたAuバンプ26と、半導体素子内部グランド配線28aと、半導体素子内部電源配線28bと、上記第1の辺の対辺に沿って形成され、各々予め定められた表示装置を駆動させる信号を出力する半導体素子内部出力部30A〜半導体素子内部出力部30Dとが備えられている。半導体素子内部グランド配線28aと半導体素子内部電源配線28bを総称して内部電源配線28と呼ぶ。また、ドライバ出力端子電極25を第2電極25とも呼ぶ。なお、半導体素子内部グランド配線28a及び半導体素子内部電源配線28bは、半導体素子12の全般に設けられており、そのうち半導体素子内部出力部30近傍では上記第1の辺の対辺に沿っている。

【0017】

一方、絶縁性フィルム18には、半導体素子12が搭載される搭載領域と、搭載領域の外周に規定される非搭載領域が定義されている。ここで、半導体素子12が矩形であるため、ここで定義される搭載領域も矩形を意味する。特にドライバICの場合、長方形型であることがほとんどであり、以下、長辺の方向を長手方向と定義する。

【0018】

絶縁性フィルム18上には、ドライバICを制御する制御IC(例えばタイミングコントローラ等)からの信号が入力される入力側アウターリード(外部入力端子)22と、表示装置(LCDパネル等)へ搭載され信号を出力する出力側アウターリード(外部出力端子)24とが、非搭載領域に形成されている。

【0019】

また、絶縁性フィルム18上の搭載領域には、第1接続ノード19a、第2接続ノード20a、および第3接続ノード54aが形成されている。

【0020】

ここで、第1接続ノード19aは、矩形の搭載領域に規定される第1の辺に沿って設けられている。また、第2接続ノード20aは、上記第1の辺の対辺に沿って設けられている。さらに、第3接続ノード54aは、搭載領域において、第1接続ノード19aおよび第2接続ノード20aの内側に設けられている。本実施の形態では、第3接続ノード54aは第2接続ノード20a近傍に形成されているとも表現することができる。

【0021】

さらに絶縁性フィルム18上には、金属配線パターン(第1〜3接続パターン)19,20,54が形成されている。金属配線パターン19は、第1接続ノード19aと入力側アウターリード22を接続する。金属配線パターン20は、第2接続ノード20aと出力側アウターリード24を接続する。金属配線パターン54は、第1接続ノード19aと第3接続ノード54aを接続するものである。なお、各アウターリード、金属配線パターン及び接続ノードは、必要に応じて一体形成されるものである。

【0022】

ここで、Auバンプ16a,16b,26は、半導体素子12の外周に沿って設けられた電極14a,14b,25上に設けられており、半導体素子12が絶縁性フィルム18に搭載された状態において、金属配線パターン19,20、及び当該金属配線パターン19,20の一部に設けられた第1接続ノード19aまたは第2接続ノード20aを介して、Auバンプ16a,16bは入力側アウターリード22に、Auバンプ26は出力側アウターリード24に、各々電気的に接続される。このように、第1接続ノード19aは、半導体素子12に設けられたAuバンプ及び当該Auバンプが設けられた端子電極に電気的に接続されるものであるので、上記搭載領域に形成されると共に、半導体素子内部グランド配線28a又は半導体素子内部電源配線28bに電気的に接続される。

【0023】

また、半導体素子12では、各Auバンプの下に設けられた端子電極と、半導体素子12の内部回路とが、当該半導体素子12の内部配線により電気的に接続されている。

【0024】

また、グランド端子電極14aは半導体素子内部グランド配線28aに、電源端子電極14bは半導体素子内部電源配線28bに、各々電気的に接続されている。これにより、半導体素子内部グランド配線28a及び半導体素子内部電源配線28bは、第1接続ノード20a及び金属配線パターン20を介して入力側アウターリード22に電気的に接続されている。

【0025】

半導体装置10Aでは、入力側アウターリード22より信号を入力し、半導体素子12内において所定の変換を施した後、出力側アウターリード24より変換後の信号を出力する。なお、図1及び図2では、錯綜を回避するために、半導体素子12の内部回路(各機能ブロック)については半導体素子内部出力部30A〜半導体素子内部出力部30Dのみを図示し、その他の内部回路(例えば、ロジック部、レベル変換部、ラッチ部、DA変換部、階調電圧生成部等)の図示は省略している。

【0026】

また、半導体素子内部出力部30A〜半導体素子内部出力部30Dは一般的にオペアンプを主構成要素として構成される。以下、出力部を総称して半導体素子内部出力部30として、当該半導体素子内部出力部30について説明する。

【0027】

半導体素子内部出力部30は一般的に、対応するドライバ出力端子電極25の数と同等かそれ以上のオペアンプが設けられるものである。ドライバ出力端子電極25の数が非常に多いため、設計上、半導体素子内部出力部30A〜Dのようにブロックに分けられている。720チャネルの出力を有するドライバICの場合、4分割される結果、半導体素子内部出力部30Aは180チャネルに相当するオペアンプが設けられている。なお、正極及び負極の駆動を別々のオペアンプで行う場合は、チャネル数の数倍のオペアンプが形成されている場合もある。ここでは、上記オペアンプの集合体を一つの出力部として表している。半導体素子内部出力部30は、ドライバ出力端子電極25の近傍に設けられている。

【0028】

なお、半導体素子内部出力部30Bと半導体素子内部出力部30Cとの間は図面上、他の半導体素子内部出力部30間よりも広い空間が確保されているが、ここには、階調電圧生成回路等の各種機能ブロックが配置される。

【0029】

ここで、本実施の形態に係る半導体素子12には、その表面で、かつ半導体素子内部出力部30A〜30Dの近傍に、グランド端子電極52aと、電源端子電極52bとが形成されている。ここで、グランド端子電極52a上にはグランド用半導体素子表面Auバンプ50aが形成されており、電源端子電極52b上には電源用半導体素子表面Auバンプ50bが形成されている。なお、以下では、グランド端子電極52a及び電源端子電極52bを総称して第3電極52という。なお、上記半導体素子内部出力部の近傍とは、最も近くに存在する機能ブロックが半導体素子内部出力部である位置や、半導体内部出力部の外周に位置することを意味する。

【0030】

ここで、第3電極52は、ドライバ出力端子電極25の近傍に設けられているとも表現することが可能である。さらに言い換えると第3電極52は、半導体素子内部出力部30の外周に設けられている。また、場合によっては、半導体素子内部出力部30Aと半導体素子内部出力部30Bのブロック間に設けられることもある。ここで、第3電極52は、複数設けられている方が望ましい。複数の第3電極52は、それぞれ金属配線パターン54により、グランド端子電極52a間、あるいは電源端子電極52b間で共通接続される。第3電極52が複数設けられる位置としては、半導体素子12の中央部と、出力部30のブロック間、及び半導体素子12の表面の短辺に相当する側辺近傍等である。半導体素子12の長手方向の左右においてそれぞれ設けられることも望ましい。

【0031】

ここで、上記共通接続された金属配線パターン54は、長手方向に直線的に配置されている部分を有する。また、グランド端子電極52a間を共通接続した金属配線パターン54と、電源端子電極52b間を共通接続した金属配線パターン54は、半導体素子内部出力部30を挟むように配置されている。言い換えるとグランド端子電極52a間を共通接続した金属配線パターン54と、電源端子電極52b間を共通接続した金属配線パターン54との間に出力部30が位置する。さらに、共通接続した金属配線パターン54は、半導体素子内部グランド配線28a及び半導体素子内部電源配線28bの近傍に配置されている。なお、半導体素子内部グランド配線28a及び半導体素子内部電源配線28bも長手方向に延在して設けられている。

【0032】

第1電極であるグランド端子電極14a及び電源端子電極14bは、半導体素子12の上記第1の辺に沿って複数設けられている。言い換えると、長手方向において、上記第1の辺を2分割した左右にそれぞれグランド端子電極14a及び電源端子電極14bが設けられている。ここで、電源端子電極14bは、グランド端子電極14aよりも中央寄りに配置されている。また、電源端子電極14bと接続される金属配線パターン54は、半導体素子12の中央近傍を経由して、電源端子電極52b間を共通接続した金属配線パターン54と接続されている。

【0033】

更に、グランド端子電極14aとグランド端子電極52aは半導体素子内部グランド配線28aにより接続され、電源端子電極14bと電源端子電極52bは半導体素子内部電源配線28bにより接続されている。

【0034】

一方、絶縁性フィルム18には、半導体素子12が搭載された状態で、当該半導体素子12のAuバンプ16aとグランド用半導体素子表面Auバンプ50aとの間を電気的に接続すると共に、Auバンプ16bと電源用半導体素子表面Auバンプ50bとの間を電気的に接続する金属配線パターン54が形成されている。従って、半導体素子12が絶縁性フィルム18に搭載された状態で、金属配線パターン54の一部に設けられた第3接続ノード54aがグランド端子電極52a又は電源端子電極52bに電気的に接続される結果、グランド端子電極14aとグランド端子電極52a、及び電源端子電極14bと電源端子電極52bが電気的に接続される。なお、一般に、金属配線パターン54は、Cu(銅)等の比較的導電率の高い導電性物質により形成されるので、当該金属配線パターン54による抵抗は半導体素子の内部に形成されるアルミに比べて非常に低い。

【0035】

なお、本実施の形態に係る半導体装置10Aの製造は、一例として特許文献1に開示されている技術等、従来既知の技術により行うことができるため、ここでの説明は省略する。

【0036】

このように、本実施の形態によれば、半導体素子12の機能ブロック近傍に第3電極52を配置し、基板である絶縁フィルム18に設けられた入力側アウターリード22と接続された金属配線パターン19及び金属配線パターン54を設け、金属配線パターン54と第3電極52を接続することにより機能ブロックに均一に電源を供給することが可能となる。特に、精度が求められる半導体素子内部出力部30近傍に第3電極52を配置し、第3電極52と内部電源配線28とを接続することにより、第1電極14から内部電源配線28を介して出力部30へ電源を供給する経路と第3電極52から内部電源配線28を介して出力部30へ電源を供給する経路とを確保することができ、内部電源配線28の領域を減らしたとしても実質的に抵抗値を同等又は低減することが可能となる。よって内部電源配線28の低減による半導体素子12の面積を小さくすることと、半導体素子12の性能の維持とを実現することが可能となる。また、実質的に内部電源配線28の抵抗値の低減により発熱量を低減することができる。

【0037】

また、このとき、半導体素子12内の電源配線を削除することなく用いており、表示装置用ドライバとしての特性が変化することを抑制することができるため、当該特性の変化に対応するための各種調整が不要となる結果、効率的に設計することができる。

【0038】

また、電源端子電極52bに接続される金属配線パターン54を、ドライバ出力端子電極25の近傍及び半導体素子内部出力部30の近傍まで配置したことで、より効果的に電源電圧の変動を抑制することを可能とする。半導体素子12の左右においてそれぞれ上記構成を設け、さらに共通接続することで、より一層内部電源配線28の抵抗値を下げることを可能とし、均一に電源を供給できる効果が増す。金属配線パターン54を半導体素子12の中央部を経由させることにより、本実施の形態を実現可能とする。さらに半導体素子内部出力部30近傍に第3電極52を設け、金属配線パターン54で接続していることにより、特に発熱量が高い半導体素子内部出力部30の熱を伝導する役割が期待できる。

【0039】

なお、本実施の形態の構成を有する絶縁性フィルム18を用いることで効率的な設計を可能とする。

【0040】

[第2の実施の形態]

【0041】

図3及び図4には、表示装置用ドライバとしてCOF法を適用して作製された、本実施の形態に係る半導体装置10Bの構成が示されている。なお、図3は半導体装置10Bの構成を示す平面図であり、図4(A)は半導体装置10Bのグランド配線に関する部分の構成を示す平面図であり、図4(B)は半導体装置10Bの電源配線に関する部分の構成を示す平面図である。なお、図3及び図4における図1及び図2と同一の構成要素については図1及び図2と同一の符号を付して、その説明を省略する。

【0042】

半導体装置10Bには、当該半導体素子12の上記第1の辺に沿って形成された信号入力用の電極である第1接続端子62a及び第2接続端子62bと、第1接続端子62aの表面上に設けられたAu(金)バンプ60a及び第2接続端子62bの表面上に設けられたAu(金)バンプ60bとが備えられている。なお、第1接続端子62a及び第2接続端子62bは電源端子電極14bの近傍に設けられている。

【0043】

一方、絶縁性フィルム18上の搭載領域には、信号入力用接続ノード54bが形成されている。信号入力用接続ノード54bは、上記第1の辺に沿って設けられている。

【0044】

さらに絶縁性フィルム18上には、信号入力用接続ノード54bと入力用アウターリード22を接続する金属配線パターン19及び金属配線パターン54が形成されている。なお、入力アウターリード22、各金属配線パターン及び信号入力用接続ノード54bは、必要に応じて一体形成されるものである。

【0045】

ここで、Auバンプ60a及びAuバンプ60bは、半導体素子12の外周に沿って設けられた第1接続端子62a上及び第2接続端子62b上に設けられており、半導体素子12が絶縁性フィルム18に搭載された状態において、金属配線パターン19、金属配線パターン54、及び当該金属配線パターン54の一部に設けられた信号入力用接続ノード54bを介して入力側アウターリード22に電気的に接続される。このように、信号入力用接続ノード54bは、半導体素子12に設けられたAuバンプ60a,60b及び当該Auバンプが設けられた第1接続端子62a及び第2接続端子62bに電気的に接続されるものであるので、上記搭載領域に形成される。

【0046】

なお、半導体素子12では、各Auバンプ60a,60bの下に設けられた第1接続端子62a及び第2接続端子62bと、半導体素子12の内部回路とが、当該半導体素子12の内部配線により電気的に接続されている。

【0047】

また、半導体装置10Bでは、半導体素子の長手方向中央部より左側に、信号入力用接続ノード54bと入力用アウターリード22を接続する金属配線パターン19及び金属配線パターン54(以下、「左側入力信号配線パターン」という。)、第1接続端子62a、グランド端子電極52a、及び電源端子電極52bが配置されると共に、長手方向中央部より右側に、信号入力用接続ノード54bと入力用アウターリード22を接続する金属配線パターン19及び金属配線パターン54(以下、「右側入力信号配線パターン」という。)、第2接続端子62b、グランド端子電極52a、及び電源端子電極52bが配置されている。

【0048】

ここで、絶縁性フィルム18では、左側入力信号配線パターンと、入力アウターリード22と長手方向左側のグランド端子電極14a及び電源端子電極14bとを接続する金属配線パターンは列を成して配置されると共に、左側入力信号配線パターンが、入力アウターリード22と長手方向左側のグランド端子電極14a及び電源端子電極14bとを接続する金属配線パターンの外側(左側)に配置されている。また、右側入力信号配線パターンと、入力アウターリード22と長手方向右側のグランド端子電極14a及び電源端子電極14bとを接続する金属配線パターンは列を成して配置されると共に、右側入力信号配線パターンが、入力アウターリード22と長手方向右側のグランド端子電極14a及び電源端子電極14bとを接続する金属配線パターンの外側(右側)に配置されている。

【0049】

また、第1接続端子62a及び第2接続端子62bは、共にグランド端子電極14a及び電源端子電極14bよりも上記第1の辺の中央部側に配置されており、左側入力信号配線パターンは、上記第1の辺から見て、長手方向左側のグランド端子電極14a及び電源端子電極14bよりも外側(左側)に配置されており、右側入力信号配線パターンは、上記第1の辺から見て、長手方向右側のグランド端子電極14a及び電源端子電極14bよりも外側(右側)に配置されている。

【0050】

ここで、絶縁性フィルム18では、長手方向左側のグランド端子電極14aとグランド端子電極52aとを接続する金属配線パターン(以下、「左側グランド配線パターン」という。)と、長手方向左側の電源端子電極14bと電源端子電極52bとを接続する金属配線パターン(以下、「左側電源配線パターン」という。)が、左側入力信号配線パターンを迂回するように配置される一方、長手方向右側のグランド端子電極14aとグランド端子電極52aとを接続する金属配線パターン(以下、「右側グランド配線パターン」という。)と、長手方向右側の電源端子電極14bと電源端子電極52bとを接続する金属配線パターン(以下、「右側電源配線パターン」という。)が、右側入力信号配線パターンを迂回するように配置されている。

【0051】

また、絶縁性フィルム18では、左側グランド配線パターン及び左側電源配線パターンによるインピーダンスと、右側グランド配線パターン及び右側電源配線パターンによるインピーダンスとが互いに等しくなるように調整されている。

【0052】

なお、図3及び図4(B)に示されるように、左側電源配線パターンを構成する金属配線パターン19と金属配線パターン54、及び右側電源配線パターンを構成する金属配線パターン19と金属配線パターン54は、一部で一体形成されると共に、上記非搭載領域上を経由して電源端子電極52bに接続されている。

【0053】

このように、本実施の形態の構成をとることで、第1の実施の形態の効果に加えて、既存のドライバICのピン配置と搭載パネル側のピン配置が異なる場合でも、基板の設計のみで対応することが可能となる。言い換えると、従来の半導体素子12のレイアウト設計等にかかっていた時間に比較して、設計にかかる時間を格段に短くすることが可能となる。特に、左側グランド配線パターン及び左側電源配線パターンが第1接続端子62a及び左側入力信号配線パターンを迂回し、右側グランド配線パターン及び右側電源配線パターンが第2接続端子62b及び右側入力信号配線パターンを迂回することで、グランド端子電極52a及び電源端子電極52bとの接続が可能となる。また、半導体素子12の左右で、それぞれ左側グランド配線パターン及び左側電源配線パターンによるインピーダンスと、右側グランド配線パターン及び右側電源配線パターンによるインピーダンスを揃えたことで、左右で均一に電源供給することを可能とし、ピン間のばらつきを、より一層低減することを可能とする。

【0054】

[第3の実施の形態]

【0055】

図5及び図6には、表示装置用ドライバとしてCOF法を適用して作製された、本実施の形態に係る半導体装置10Cの構成が示されている。なお、図5は半導体装置10Cの構成を示す平面図であり、図6(A)は半導体装置10Cのグランド配線に関する部分の構成を示す平面図であり、図6(B)は半導体装置10Cの電源配線に関する部分の構成を示す平面図である。なお、図5及び図6における図1及び図2と同一の構成要素については図1及び図2と同一の符号を付して、その説明を省略する。

【0056】

本実施の形態に係る半導体装置10Cでは、グランド端子電極14a及び電源端子電極14bが、上記第1の辺に沿って交互に配置されている。詳細に説明すると、グランド端子電極14aと電源端子電極14bは、2つが隣り合って配置される。隣り合って配置されるグランド端子電極14aと電源端子電極14bを一組の電源電極対15とすると、第1の辺の中央部から左右にそれぞれ2組の電源電極対15が配置される。一組のグランド端子電極14aと電源端子電極14bは、グランド端子電極14aより電源端子電極14bの方が第1の辺の中央部に近く配置されている。左右のそれぞれ2組の電源電極対15間は、他の電極が形成されてもよい。例えば基準電圧が入力される電極等である。

【0057】

ここで、本実施の形態に係る絶縁性フィルム18では、グランド端子電極14aとグランド端子電極52aとを接続する金属配線パターンが半導体内部出力部30の外周を囲うように配置されると共に、電源端子電極14bと電源端子電極52bとを接続する金属配線パターンが半導体内部出力部30の外周を囲うように配置されている。詳細には、半導体素子12の長手方向における左右において、金属配線パターンはそれぞれ3つの部分から構成される。例えば、半導体素子12の左側部分を例に説明する。第2電極25と第3電極52間に形成され、第2電極25近傍に長手方向に直線的に形成された金属配線パターン54の第1部分31と、半導体素子12の長手方向において左側に配置された2組の電源電極対15のうち、第1の辺の中央部17寄りのグランド端子電極14aと半導体素子12の中央部17を経由して第1部分31と接続される第2部分32と、半導体素子12の長手方向において左側に配置された2組の電源電極対15のうち他方であるグランド端子電極14aが搭載領域から非搭載領域を経由して第1部分31と接続される第3部分33から金属配線パターンは構成される。前述の第1〜3部分を総合すると出力部30の外周を囲うように配置されている。なお、半導体素子12の右側部分も同様に3つの部分から構成され、左右それぞれの第1部分31は共通接続されている。

【0058】

このように、本実施の形態をとることで、半導体素子12の左右においてそれぞれ2組の電源電極対を有するピン配置であっても、第1の実施の形態の効果を得ることを可能とする。また、グランド端子電極14aとグランド端子電極52aとを接続する金属配線パターンが半導体内部出力部30の外周を囲うように配置されると共に、電源端子電極14bと電源端子電極52bとを接続する金属配線パターンが半導体内部出力部30の外周を囲うように配置されているので、均一に電源供給することを可能とし、ピン間のばらつきを、より一層低減することを可能とする。

【0059】

[第4の実施の形態]

【0060】

図7には、表示装置用ドライバとしてCOF法を適用して作製された、本実施の形態に係る半導体装置10Dの概略構成が示されている。なお、同図における図1と同一の構成要素には図1と同一の符号を付して、その説明を省略する。

【0061】

同図に示されるように、本実施の形態に係る半導体装置10Dは、半導体素子12の長手方向の略中央部に電圧生成部90が設けられている。

【0062】

この電圧生成部90は、入力側アウターリード22と、抵抗ラダー用接続パターン21及び金属パターン54とを介して印加された基準電圧間を抵抗ラダーによって分圧することにより、複数の階調電圧を生成するものである。

【0063】

ここで、本実施の形態に係る半導体装置10Dでは、半導体素子12の周辺部に抵抗ラダー用の端子電極を設けることなく、抵抗ラダーの近傍に端子電極を設ける一方、絶縁性フィルム18に対し、当該端子電極と入力側アウターリード22とを、抵抗ラダー用接続パターン21及び金属パターン54を介して直接接続している。このため、半導体素子12の周辺部に抵抗ラダー用の端子電極を設ける場合に比較して、半導体素子12を小型化することができる。

【0064】

なお、同図におけるデコーダ31A〜31Dは、各々半導体素子内部出力部30A〜半導体素子内部出力部30Dの何れか1つと1対1で対応し、電圧生成部90によって生成された階調電圧を用いて、対応する半導体素子内部出力部で適用する信号を生成するものである。

【0065】

図8には、電圧生成部90の詳細構成が示されている。なお、同図における図1と同一の構成要素には図1と同一の符号を付して、その説明を省略する。

【0066】

同図に示されるように、電圧生成部90には、各々予め定められた位置に配置された4つの抵抗器80a,80b,80c,80dが直列接続されて構成され、当該半導体素子12から表示装置に対して出力する出力電圧の基準となる階調電圧を生成する抵抗ラダー80が備えられている。

【0067】

ここで、電圧生成部90には、抵抗ラダー80の近傍に形成された5つの抵抗ラダー用電極82a,82b,82c,82d,82eが備えられている。また、電圧生成部90には、抵抗ラダー用電極82a及び抵抗ラダー用電極82eと抵抗ラダー80の上記直列接続の端部とを接続する半導体素子内部配線86と、抵抗ラダー用電極82b〜82dと抵抗ラダー80の上記直列接続の中間接続部とを接続する半導体素子内部配線88とが備えられている。なお、抵抗ラダー用電極82aの表面上にはAu(金)バンプ84aが、抵抗ラダー用電極82bの表面上にはAuバンプ84bが、抵抗ラダー用電極82cの表面上にはAuバンプ84cが、抵抗ラダー用電極82dの表面上にはAuバンプ84dが、抵抗ラダー用電極82eの表面上にはAuバンプ84eが、各々設けられている。

【0068】

一方、絶縁性フィルム18には、上記搭載領域に形成され、対応する抵抗ラダー用電極82a,82b,82c,82d,82eに接続される抵抗ラダー用接続ノード21aと、上記非搭載領域から上記搭載領域にわたって形成され、入力側アウターリード22と抵抗ラダー用接続ノード21aとを接続する抵抗ラダー用接続パターン21及び金属配線パターン54とが備えられている。

【0069】

半導体装置10Dでは、入力側アウターリード22より信号を入力し、半導体素子12内において所定の変換を施した後、出力側アウターリード24より変換後の信号を出力する。なお、図8では、錯綜を回避するために、半導体素子12の内部回路については抵抗ラダー80のみを図示し、その他の内部回路(例えば、ロジック部、レベル変換部、ラッチ部、DA変換部、階調電圧生成部等の図示は省略している。

【0070】

このように、本実施の形態によれば、Auバンプ84a〜84e、及びその下に各々設けられる抵抗ラダー用電極82a〜82eを、各々に接続される抵抗ラダー80の近傍に配置し、入力側アウターリード22とAuバンプ84a〜84eの接続状態を変化させないように半導体素子上金属配線パターン54を回り込むように配線しているので、抵抗ラダー80とAuバンプ84a〜84eの物理的距離を縮め、半導体素子内部配線86及び半導体素子内部配線88のインピーダンスを低下させることができる結果、半導体素子内部配線86及び半導体素子内部配線88の配線領域を縮小することができる。要するに、半導体素子12の面積を小さくすることができる。言い換えれば、半導体素子内部出力部30より出力される電圧の基となる電圧を生成する電圧生成部90に入力される基準電圧を、より変動のない形で供給することを可能とし、更には、半導体素子内部の配線領域の縮小に寄与することで、半導体素子の面積を縮小することができる。

【0071】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。発明の要旨を逸脱しない範囲で上記実施の形態に多様な変更または改良を加えることができ、当該変更または改良を加えた形態も本発明の技術的範囲に含まれる。

【0072】

また、上記の実施の形態は、クレーム(請求項)にかかる発明を限定するものではなく、また実施の形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。前述した実施の形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜の組み合わせにより種々の発明を抽出できる。実施の形態に示される全構成要件から幾つかの構成要件が削除されても、効果が得られる限りにおいて、この幾つかの構成要件が削除された構成が発明として抽出され得る。

【0073】

例えば、上記第4の実施の形態では、本発明の半導体装置の一例として図8に示される半導体装置10Dを適用した場合について説明したが、本発明はこれに限定されるものではなく、例えば、図9に示される半導体装置10Eや、図10に示される半導体装置10Fを適用することもできる。図10では、図8や図9とは異なって、基準電圧入力電極83が設けられている。望ましくは設けられない方が、基準電圧入力電極83を設けるための領域を確保する必要がなく、面積が少なくすむが、必要に応じて設けることを排除するものではないことを説明する図でもある。なお、図9及び図10では、図8に示されるものと同一の役割を有するものには図8と同一の符号を付している。これらの場合にも、上記第4の実施の形態と同様の効果を奏することができる。

【0074】

また、上記第1の実施の形態〜第4の実施の形態は、組み合わせて適用することができることは言うまでもない。

【0075】

図11には、上記第3の実施の形態と上記第4の実施の形態を組み合わせた場合の半導体装置の構成例が示されている。図11では、テープ基板を図示していないが、図上に記載された配線はすべてテープ基板上に形成されているものである。

【0076】

同図に示されるように、この構成例では、電圧生成部90として、電圧生成部90A及び電圧生成部90Bの2つが設けられている。電圧生成部90の詳細は図8〜10に示された内容である。電圧生成部90Aと電圧生成部90Bとの間の領域92は、出力部30や電圧生成部90を除く他の機能ブロックが配置される領域である。

【0077】

ここで、半導体素子内部出力部30A〜DはそれぞれPチャネルMOS−FETにより構成されたPデコーダとNチャネルMOS−FETにより構成されたNデコーダのいずれかで選択された階調電圧を出力する。そして、電圧生成部90Aは上記PチャネルMOS−FETにより構成されたデコーダに入力する階調電圧を生成するものとされており、電圧生成部90Bは上記PチャネルMOS−FETにより構成されたデコーダに入力する階調電圧を生成するものとされている。

【0078】

一般に、8ビット(256階調)の表示が可能なドライバであれば、電圧生成部90A及び電圧生成部90Bで、それぞれ256階調分の電圧が生成されており、各々に基準電圧が9個或いは11個程度供給される。

【0079】

また、この半導体素子12には、第1の辺に沿って、出力用電極形成領域98A、入力用電極形成領域98B、及び入力用電極非形成領域98Cの3つの領域が設けられている。入力用電極非形成領域98Cは、入力用電極形成領域98B間に設けられるものである。特に入力用電極形成領域98Bに設けられた第1電極(グランド端子電極又は電源端子電極)間に入力用電極非形成領域98Cは設けられる。この場合、入力用電極非形成領域98Cに対応する基板上の領域を介して、入力側アウターリードと抵抗ラダー用電極82とを、金属配線パターン54(VGMA)で接続することになる。

【0080】

また、図11に示す金属配線パターン54は特徴的な形状をしている。特に電源端子電極14aと電源端子電極52とを接続する金属配線パターン54(Vdd)について以下にその構造を説明する。金属配線パターン54(Vdd)は、出力部30の近傍に配置された電源端子電極52それぞれを共通接続する共通接続部94と、電源端子電極14aと共通接続部94とを接続し、内部電源配線のインピーダンスを調整するインピーダンス調整部96とから構成される。インピーダンス調整部96は、共通接続部94との接続を最短距離で結ばず、半導体素子12の角部から最も近い電源端子電極52aに近づくように共通接続部94と接続される。言い換えると、出力部30のうち半導体素子12の長手方向における端部の出力部30D(又は半導体素子12の左側の場合出力部30A)に近づくように共通接続部94と接続される。本構成をとることにより、出力部30Cと出力部30Dとの電源の均一性をさらに高く保つことが可能となる。

【0081】

なお、第1の実施の形態と第4の実施の形態を、同図に示されるように組み合わせた場合には、半導体素子12の左右にそれぞれ配置された2個の電源電極対のいずれか一方を使用して第1の実施の形態に相当する配線パターン54を配置することで実現が可能である。

【0082】

同様に、上記第1の実施の形態〜第3の実施の形態の複数を組み合わせて適用することもできる。これらの場合、組み合わせた実施の形態によって奏することのできる全ての効果を得ることができる。

【0083】

また、上記各実施の形態における各種Auバンプの数は一例であり、他の数とすることができることも言うまでもない。この場合も、上記各実施の形態と同様の効果を奏することができる。

【0084】

また、上記各実施の形態では、対象とする表示装置を特に限定しなかったが、当該表示装置として、液晶ディスプレイ装置、プラズマ・ディスプレイ装置、有機ELディスプレイ装置等の各種ディスプレイ装置に適用することができる。

【0085】

また、上記各実施の形態では、バンプの材質としてAuを適用した場合について説明したが、他の金属を適用することができることも言うまでもない。

【0086】

また、上記第1〜第3の実施の形態では、半導体素子内部出力部を半導体素子内部出力部30A〜30Dの4つのブロックに分けた場合について説明したが、本発明はこれに限定されるものではなく、他の数のブロックに分ける形態とすることができることも言うまでもない。この場合も、上記各実施の形態と同様の効果を奏することができる。

【0087】

また、上記第4の実施の形態では、抵抗ラダーを4つのブロックに分けた場合について説明したが、本発明はこれに限定されるものではなく、他の数のブロックに分ける形態とすることができることも言うまでもない。この場合も、上記第4の実施の形態と同様の効果を奏することができる。

【符号の説明】

【0088】

10A〜10G 半導体装置

12 半導体素子

14a グランド端子電極(第1電極,第1グランド電極)

14b 電源端子電極(第1電極,第1電源電極)

16a Auバンプ

16b Auバンプ

18 絶縁性フィルム(基板)

19 金属配線パターン(第1配線パターン)

19a 第1接続ノード

20 金属配線パターン(第2接続パターン)

20a 第2接続ノード

21 抵抗ラダー用接続パターン

21a 抵抗ラダー用接続ノード

22 入力側アウターリード(外部入力端子)

24 出力側アウターリード(外部出力端子)

25 ドライバ出力端子電極(第2電極)

26 Auバンプ

28a 半導体素子内部グランド配線(グランド配線)

28b 半導体素子内部電源配線(電源配線)

30A〜30D 半導体素子内部出力部(出力部)

50a グランド用半導体素子表面Auバンプ

50b 電源用半導体素子表面Auバンプ

52a グランド端子電極(第3電極,第2グランド電極)

52b 電源端子電極(第3電極,第2電源電極)

54 金属配線パターン(第3配線パターン,入力信号配線パターン)

54a 第3接続ノード

54b 信号入力用接続ノード(信号入力ノード)

62a 第1接続端子(信号入力電極)

62b 第2接続端子(信号入力電極)

80 抵抗ラダー

80a〜80d 抵抗器

82a〜82e 抵抗ラダー用電極

84a〜84e Auバンプ

86 半導体素子内部配線(端部用接続配線)

88 半導体素子内部配線(中間部用接続配線)

【特許請求の範囲】

【請求項1】

複数の機能ブロックが配置された半導体素子を搭載する矩形の搭載領域と、前記搭載領域外周に規定される非搭載領域とを備え、表示装置を駆動する半導体素子搭載用のテープ基板であって、

前記非搭載領域に設けられた外部入力端子と、

前記非搭載領域に設けられた外部出力端子と、

前記搭載領域の第1の辺に沿って設けられた複数の第1接続ノードと、

前記搭載領域の第1の辺に対向する辺に沿って設けられた複数の第2接続ノードと、

前記搭載領域であって、前記第1接続ノード及び前記第2接続ノードよりも内側、かつ前記機能ブロックの外周領域に対応する当該基板の領域に設けられた第3接続ノードと、

前記外部入力端子と前記第1接続ノードを接続する第1配線パターンと、

前記外部出力端子と前記第2接続ノードを接続する第2配線パターンと、

前記複数の第1接続ノードと前記複数の第3接続ノードを接続し、前記第1配線パターンに接続された第3配線パターンと、

前記第3配線パターンの前記第1接続ノードと前記第3接続ノードとの接続は少なくとも一部が前記非搭載領域を経由して接続されることを特徴とするテープ基板。

【請求項2】

前記第1配線パターンと前記第3配線パターンは、一体形成されている

ことを特徴とする請求項1に記載のテープ基板。

【請求項3】

前記第3接続ノードは、前記第2接続ノード近傍に設けられている

ことを特徴とする請求項1または請求項2に記載のテープ基板。

【請求項4】

前記第1接続ノードは、第1電源ノードと第1グランドノードから構成され、

前記第3接続ノードは、複数の第2電源ノードと複数の第2グランドノードから構成され、

前記第2電源ノードのそれぞれを接続する前記第3配線パターンは、前記搭載領域長手方向において直線状に構成され、

前記第2グランドノードのそれぞれを接続する前記第3配線パターンは、前記搭載領域長手方向において直線状に構成される

ことを特徴とする請求項3に記載のテープ基板。

【請求項5】

前記第1電源ノードと前記第3接続ノードとの接続は、前記搭載領域上の中央を経由した前記第3配線パターンにより接続される

ことを特徴とする請求項4に記載のテープ基板。

【請求項6】

前記搭載領域の長手方向において、前記第1電源ノードは前記第1グランドノードより中央部側に配置されている

ことを特徴とする請求項4に記載のテープ基板。

【請求項7】

前記搭載領域上であって、前記第1接続ノード近傍かつ前記第1の辺に沿って配置された信号入力ノードと、

前記信号入力ノードと前記外部入力端子とを接続する入力信号配線パターンと、を更に有し、

前記第1配線パターンと前記入力信号配線パターンとは、列を成して配置されると共に、前記第1配線パターンの外側に前記入力信号配線パターンが配置され、

前記信号入力ノードは、前記第1接続ノードよりも前記第1の辺の中央部側に配置され、

前記入力信号配線パターンは、前記第1の辺から見て前記第1電極よりも外側を経由して前記信号入力ノードと接続され、

前記第3配線パターンは、前記入力信号配線パターンを迂回して前記第3接続ノードと接続される

ことを特徴とする請求項3に記載のテープ基板。

【請求項8】

前記搭載領域の長手方向の左右において、それぞれ前記入力信号配線パターン、前記信号入力ノード、前記第1接続ノード、および前記第3配線パターンが配置されている

ことを特徴とする請求項7に記載のテープ基板。

【請求項9】

前記左右に配置された前記第3配線パターンは、互いのインピーダンスが等しくなるように調整されている

ことを特徴とする請求項8に記載のテープ基板。

【請求項10】

前記第1配線パターンと前記第3配線パターンは、一部で一体形成されている

ことを特徴とする請求項7に記載のテープ基板。

【請求項11】

前記第1接続ノードは、第1電源ノードと第1グランドノードから構成されると共に、前記第1電源ノードと前記第1グランドノードのいずれか一方が少なくとも複数で構成され、かつ前記第1電源ノードと前記第1グランドノードが交互に配置され、

前記第3配線パターンは、前記複数で構成された一方のノードと前記第3接続ノードとを接続すると共に、前記一方のノードのそれぞれが、前記第2接続ノード近傍で共通接続されている

ことを特徴とする請求項3に記載のテープ基板。

【請求項12】

前記搭載領域の長手方向の左右において、それぞれ前記第1接続ノード、および前記第3配線パターンが配置されている

ことを特徴とする請求項11に記載のテープ基板。

【請求項13】

前記左右の第3配線パターンは、共通接続されている

ことを特徴とする請求項12に記載のテープ基板。

【請求項1】

複数の機能ブロックが配置された半導体素子を搭載する矩形の搭載領域と、前記搭載領域外周に規定される非搭載領域とを備え、表示装置を駆動する半導体素子搭載用のテープ基板であって、

前記非搭載領域に設けられた外部入力端子と、

前記非搭載領域に設けられた外部出力端子と、

前記搭載領域の第1の辺に沿って設けられた複数の第1接続ノードと、

前記搭載領域の第1の辺に対向する辺に沿って設けられた複数の第2接続ノードと、

前記搭載領域であって、前記第1接続ノード及び前記第2接続ノードよりも内側、かつ前記機能ブロックの外周領域に対応する当該基板の領域に設けられた第3接続ノードと、

前記外部入力端子と前記第1接続ノードを接続する第1配線パターンと、

前記外部出力端子と前記第2接続ノードを接続する第2配線パターンと、

前記複数の第1接続ノードと前記複数の第3接続ノードを接続し、前記第1配線パターンに接続された第3配線パターンと、

前記第3配線パターンの前記第1接続ノードと前記第3接続ノードとの接続は少なくとも一部が前記非搭載領域を経由して接続されることを特徴とするテープ基板。

【請求項2】

前記第1配線パターンと前記第3配線パターンは、一体形成されている

ことを特徴とする請求項1に記載のテープ基板。

【請求項3】

前記第3接続ノードは、前記第2接続ノード近傍に設けられている

ことを特徴とする請求項1または請求項2に記載のテープ基板。

【請求項4】

前記第1接続ノードは、第1電源ノードと第1グランドノードから構成され、

前記第3接続ノードは、複数の第2電源ノードと複数の第2グランドノードから構成され、

前記第2電源ノードのそれぞれを接続する前記第3配線パターンは、前記搭載領域長手方向において直線状に構成され、

前記第2グランドノードのそれぞれを接続する前記第3配線パターンは、前記搭載領域長手方向において直線状に構成される

ことを特徴とする請求項3に記載のテープ基板。

【請求項5】

前記第1電源ノードと前記第3接続ノードとの接続は、前記搭載領域上の中央を経由した前記第3配線パターンにより接続される

ことを特徴とする請求項4に記載のテープ基板。

【請求項6】

前記搭載領域の長手方向において、前記第1電源ノードは前記第1グランドノードより中央部側に配置されている

ことを特徴とする請求項4に記載のテープ基板。

【請求項7】

前記搭載領域上であって、前記第1接続ノード近傍かつ前記第1の辺に沿って配置された信号入力ノードと、

前記信号入力ノードと前記外部入力端子とを接続する入力信号配線パターンと、を更に有し、

前記第1配線パターンと前記入力信号配線パターンとは、列を成して配置されると共に、前記第1配線パターンの外側に前記入力信号配線パターンが配置され、

前記信号入力ノードは、前記第1接続ノードよりも前記第1の辺の中央部側に配置され、

前記入力信号配線パターンは、前記第1の辺から見て前記第1電極よりも外側を経由して前記信号入力ノードと接続され、

前記第3配線パターンは、前記入力信号配線パターンを迂回して前記第3接続ノードと接続される

ことを特徴とする請求項3に記載のテープ基板。

【請求項8】

前記搭載領域の長手方向の左右において、それぞれ前記入力信号配線パターン、前記信号入力ノード、前記第1接続ノード、および前記第3配線パターンが配置されている

ことを特徴とする請求項7に記載のテープ基板。

【請求項9】

前記左右に配置された前記第3配線パターンは、互いのインピーダンスが等しくなるように調整されている

ことを特徴とする請求項8に記載のテープ基板。

【請求項10】

前記第1配線パターンと前記第3配線パターンは、一部で一体形成されている

ことを特徴とする請求項7に記載のテープ基板。

【請求項11】

前記第1接続ノードは、第1電源ノードと第1グランドノードから構成されると共に、前記第1電源ノードと前記第1グランドノードのいずれか一方が少なくとも複数で構成され、かつ前記第1電源ノードと前記第1グランドノードが交互に配置され、

前記第3配線パターンは、前記複数で構成された一方のノードと前記第3接続ノードとを接続すると共に、前記一方のノードのそれぞれが、前記第2接続ノード近傍で共通接続されている

ことを特徴とする請求項3に記載のテープ基板。

【請求項12】

前記搭載領域の長手方向の左右において、それぞれ前記第1接続ノード、および前記第3配線パターンが配置されている

ことを特徴とする請求項11に記載のテープ基板。

【請求項13】

前記左右の第3配線パターンは、共通接続されている

ことを特徴とする請求項12に記載のテープ基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−192933(P2010−192933A)

【公開日】平成22年9月2日(2010.9.2)

【国際特許分類】

【出願番号】特願2010−108477(P2010−108477)

【出願日】平成22年5月10日(2010.5.10)

【分割の表示】特願2007−226812(P2007−226812)の分割

【原出願日】平成19年8月31日(2007.8.31)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【Fターム(参考)】

【公開日】平成22年9月2日(2010.9.2)

【国際特許分類】

【出願日】平成22年5月10日(2010.5.10)

【分割の表示】特願2007−226812(P2007−226812)の分割

【原出願日】平成19年8月31日(2007.8.31)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【Fターム(参考)】

[ Back to top ]