ローム株式会社により出願された特許

3,511 - 3,520 / 3,539

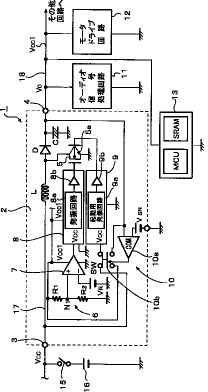

DC/DCコンバータ

【課題】乾電池1本乃至2本程度の低い電圧レベルで動作可能なMOSトランジスタによるDC/DCコンバータを提供することを目的とする。

【解決策】電池からの電力を受けて所定の電圧まで昇圧した電圧の電力を発生して負荷に供給するDC/DCコンバータにおいて、負荷に対して直列あるいは並列に挿入され電池の電源供給ラインに対してスイッチングを行う、寄生バイポーラトランジスタが出力電極側において並列に形成されたMOSトランジスタと、負荷側に出力する電力の一部を受けてこのMOSトランジスタのスイッチングの期間を負荷側の電圧に応じてこの電圧が所定の一定値になるように制御する制御回路と、電池からの電力を受け、制御回路がMOSトランジスタをON/OFFさせることができる所定電圧値より負荷の電圧が低いときに、寄生バイポーラトランジスタをスイッチングさせて負荷側に昇圧電圧を発生させる起動回路とを備えるものである。

(もっと読む)

光通信装置

【課題】 従来の光通信装置においては、エネルギー効率のよい光通信を実現するために、指向性の強い光ビームを用いている。しかし、指向性の強い光ビームは限られた方向でしか受光できないため、移動体への光通信は困難である。

【解決手段】 本発明に係る光通信装置においては、光ビーム(B)を発する光信号送信部3と、位置情報送信部2からの位置情報(A)に従って移動し光ビーム(B)を受光する移動体1とを有する光通信装置において、位置情報送信部2は光信号送信部3にも位置情報(A)を送信し、光信号送信部3は位置情報(A)に従って前記光ビームの進行方向を制御する。

(もっと読む)

半導体装置の製造方法およびプラズマ処理装置

【課題】被処理物へのチャージングダメージを抑制しつつ、被処理物に面内均一なプラズマ処理を施す。

【解決手段】下部電極2および上部電極3に高周波電力が供給されて、下部電極2および上部電極3間のプラズマによるエッチング処理が開始されてから第1次処理時間が経過すると、上部高周波電源6から出力される高周波電力の大きさがコントローラ7により制御されて、上部高周波電源6から上部電極3に印加される高周波電力の大きさが約200Wから約300Wに変更される。

【効果】エッチング処理の全期間を通じて、プラズマ中の電子の分布を均一に保つことができ、半導体ウエハW上のプラズマ密度をほぼ面内均一に保つことができる。

(もっと読む)

ガラスシール電子部品

【課題】 マイグレーションの発生を抑制することのできるガラスシールダイオードを提供する。

【解決手段】 半導体層6と、これの表面に形成された表面電極7と、半導体層6の裏面に形成された裏面電極8とを有するダイオードチップ1がガラス3によってシールされたガラスシールダイオードであって、裏面電極8は、水の存在によるイオン化のしにくい金属材料によって形成された。

(もっと読む)

半導体チップおよびそれを用いた半導体装置、ならびに半導体チップの製造方法

【課題】集積度の向上を可能とした半導体チップおよびそれを用いた半導体装置を提供する。

【解決手段】プリント配線基板10の表面11に、半導体チップ20がフェースアップ方式で接合される。半導体チップ20の側壁面24には、溝25が形成されている。溝25内には、導電ペースト26が配置されており、この導電ペースト26は、表面配線28を介して、機能領域22内の接続パッドPに接続されている。プリント配線基板10の表面の半田バンプ12と、接続パッドPとは、導電ペースト26および表面配線28を介して電気接続される。

【効果】スクライブライン領域23を利用することにより、ワイヤボンディングを行うことなく、プリント配線基板10への半導体チップ20の接合が達成されている。

(もっと読む)

電子装置

【課題】 ドライバ回路の回路構成、および伝送線路の特性インピーダンスを特定することによりバス配線系の信号伝送を高速化できる電子装置を提供する。

【解決手段】 差動相補ディジタル信号を伝達する伝送線路1と、それに整合した終端回路である終端抵抗2とからなるバス配線系に、カレントスイッチ型の差動ドライバ3を組み合わせた入出力回路を構成し、伝送線路1および終端抵抗2などを有する配線基板に、差動ドライバ3などを有する集積回路チップが搭載されて構成される電子装置であって、差動ドライバ3をカレントスイッチ型とし、かつ伝送線路1を25Ω以下の特性インピーダンスを有する線路の並列等長配線とすることで、伝送中の信号エネルギの減衰を抑え、かつ近接する伝送線路1間の電磁界干渉を抑制することができる。

(もっと読む)

半導体集積回路装置およびその製造方法

【構成】 高耐圧CMOSFET16におけるチャネル領域28cおよび28dの不純物濃度が低くされ、低耐圧CMOSFET14におけるチャネル領域28aおよび28bの不純物濃度がそれらよりも高くされる。したがって、高耐圧CMOSFET16においてはドレイン耐圧が高くなり、低耐圧CMOSFET14においては寄生容量が小さくなるとともに空乏層の広がりが抑えられる。

【効果】 高耐圧CMOSFET16においては十分な高耐圧性を得ることができ、低耐圧CMOSFET14においては動作速度を速くすることができるとともに素子サイズを小型化できる。

(もっと読む)

液晶表示素子の製法

【課題】 小さい基板と大きい基板とが貼着されて、小さい基板の側縁部に形成される角部の狭い範囲に樹脂を塗布して保護膜を形成する場合に、簡単に、しかも確実に狭い範囲に保護膜を形成することができ、製造コストを下げることができる液晶表示素子の製法を提供する。

【解決手段】 電極パターンの端部13aが露出する部分に形成される小さい基板12の側縁部12aと大きい基板11の表面11aとの接合部に樹脂による保護膜4を形成する場合に、小さい基板12の側縁部12aに弾力性のあるニードル5を用いて樹脂を塗布しながら、該塗布された樹脂にエアー供給管6によりエアーを吹き付けて大きい基板11の表面11aにその樹脂を垂らしてから硬化させることにより、2枚の基板11、12の接合部に樹脂による保護膜4を形成する。

(もっと読む)

カラー液晶表示素子の製法

【課題】 電極パターンの位置に対して精度よくカラーフィルターを設け、繊細なカラー画像を得ることができるカラー液晶表示素子の製法を提供する。

【解決手段】 液晶セル1の基板12の外表面に混合により発色する材料をそれぞれカプセル2a〜4a化して混ぜ込まれた樹脂を塗布して発色樹脂層2〜4を形成し、液晶セル1の点灯表示により電極パターン14の位置を確認し、所望の場所の発色材料のカプセル2a〜4aを破壊して発色させることによりカラーフィルタを形成する。液晶セル1は、電極パターンおよび配向膜を形成した基板11、12を2枚一定間隙を有するようにシール剤17により貼着して、その間隙に液晶材料18を充填することにより形成する。

(もっと読む)

昇圧回路

【課題】 実質的に電圧損失がない、良好な昇圧効率を有する昇圧回路を提供する。

【解決手段】 第mコンデンサCm(m=1、2、…、n−1)のスイッチング素子に接続されていない側(Sm)への印加電圧がローレベルからハイレベルに切り換わる際、及び、第(m+1)スイッチング素子Pm+1がOFFからONに切り換わる際には、第mスイッチング素子PmがOFFであり、また、第mコンデンサCmのスイッチング素子に接続されていない側(Sm)への印加電圧がハイレベルからローレベルに切り換わる際、及び、第mスイッチング素子PmがOFFからONに切り換わる際には、第(m+1)スイッチング素子Pm+1がOFFであることを特徴としている。

(もっと読む)

3,511 - 3,520 / 3,539

[ Back to top ]