株式会社日立超エル・エス・アイ・システムズにより出願された特許

51 - 60 / 327

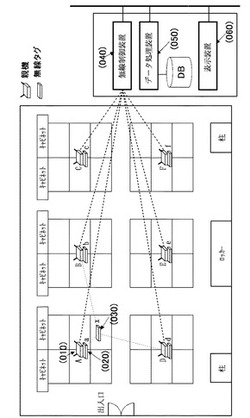

無線位置検出システムと無線位置検出方法

【課題】現場での調整・設置に要する工数を低減し、調整・設置後のレイアウト変更等にも柔軟に適用でき管理対象の無線タグの位置を高い精度で推定可能とする。

【解決手段】監視エリアにおける特定の位置に分散して配置された複数の親機及び基準となる複数の第1無線タグ、移動体に取り付けられ第2無線タグ、複数の親機に対して無線信号の授受を行う無線制御装置、データ処理装置を有する。データ処理装置は、無線制御装置を制御して各親機に対する第1無線タグの第1受信電界強度データと、各親機に対する第2無線タグの第2受信電界強度データを取得し、第2受信電界強度データのうち大きい順の所定データとそれに対応する親機に関する第1無線タグの第1受信電界強度データを参照して、該当する親機と基準となる複数の第1無線タグとの位置情報とから第2無線タグの位置を推定する。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置、半導体装置の試験方法、及びデータ処理システム

【課題】インターフェースチップを用いるタイプの半導体装置において、インターフェースチップとコアチップ間の複数の貫通電極にそれぞれ関する複数の電流パスで大きなAC特性の差がないことの確認試験を行えるようにする。

【解決手段】インターフェースチップ及びコアチップと、これらを電気的に接続するそれぞれが貫通電極を含む測定対象信号線130及び基準信号線131と、を備え、インターフェースチップは、信号発生回路100が発生したテストクロックをコアチップへ送出し、コアチップは、信号発生回路101がテストクロックから所定の測定信号を発生し、且つ所定の測定信号を測定対象信号線130及び基準信号線131へ同時に送出し、更に、インターフェースチップは、更に、測定対象信号線130及び基準信号線131を介して入力した複数の所定の測定信号の位相差をオペアンプ117によって検出し、判定回路102が試験結果を出力する。

(もっと読む)

ネットワーク処理装置

【課題】 本発明は、ネットワークに接続された印刷装置等の低消費電力化を図るものである。

【解決手段】 本発明である第一のネットワーク処理装置を、外部ネットワークに接続された印刷装置内部に配置された第二のネットワーク処理装置である物理層(PHY)とマルチメディア層(MAC)の間に接続し、前記第一のネットワーク処理装置が、印刷装置と第二のネットワーク処理装置がスリープ中、あるいは、休止中でも、前記外部ネットワークからの受信パケットを解釈し必要な応答をする。

(もっと読む)

記憶装置と半導体不揮発性メモリの記憶方法

【課題】不揮発性メモリのランダムライトアクセスの高速化を図る。

【解決手段】半導体不揮発性メモリは、複数の消去単位からなる初期割当領域及び初期未使用領域を有する。ホスト側論理アドレスが順次に並ぶ最小管理単位を設定し、入力されたデータをバッファに順次に書き込み、最小管理単位毎の論理アドレスと不揮発性メモリの物理アドレスとのアドレスの変換情報を生成する。バッファの全記憶容量に対して書き込まれたデータを、書き込み予定の第1の消去単位の未書き込み領域に順次に書き込む。第1の消去単位の未書込領域がなくなると、検索された第2の消去単位の有効データを予め準備されている消去済等の第3の消去単位に書き込んで変換情報を更新して新第1の消去単位に置き換える。第2の消去単位を一括消去して新第3の消去単位の生成準備と並行して新第2の消去単位を検索する。

(もっと読む)

積層型半導体装置およびチップ自動認識選択回路

【課題】貫通電極によって共通接続された積層型半導体装置を構成する各半導体チップを別々に動作させる。

【解決手段】積層される半導体チップに設けられたチップ自動認識選択回路900a〜900eは、それぞれ、入力されるパルス信号の周期を2倍の周期に変換し出力する周期変更回路12(TFF回路)と、周期変更回路12の入力の論理レベルが、他の全ての周期変更回路12の入力の論理レベルと異なる時間に、半導体チップに対し共通に供給されるチップ選択アドレス信号B0、B1、B2を取り込み、自己チップアドレスとして記憶する自己アドレス記憶回路(ラッチ回路LC1〜LC5)と、チップ選択アドレスと自己チップアドレスとを比較して一致判定を行う判定回路(比較回路13)とを備える。

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

半導体装置

【課題】予備の貫通電極を用いて貫通電極の不良を救済する場合に、置換の前後における信号パスの長さの差を短縮する。

【解決手段】ドライバ回路101〜108を有する半導体チップIFと、レシーバ回路201〜208を有する半導体チップCCと、半導体チップCCに設けられた貫通電極301〜309とを備える。半導体チップIFは、i番(iは1〜nの整数)のドライバ回路の出力端をi番からi+m番の貫通電極のいずれかに排他的に接続する出力切り替え回路120を有し、半導体チップCCは、i番(iは1〜nの整数)のレシーバ回路の入力端をi番からi+m番の貫通電極のいずれかに排他的に接続する入力切り替え回路220を有する。これにより、置換前の信号パスと置換後の信号パスとの間にほとんど配線長差が生じないことから、信号品質が高められる。

(もっと読む)

半導体装置及びその調整方法並びにデータ処理システム

【課題】複数のコアチップからそれぞれ出力される複数のリードデータをインターフェースチップにおいて正しく取り込む。

【解決手段】複数のコアチップCCiの夫々は、リードコマンドに応答してインターフェースチップIFにリードデータを出力するデータ出力回路54oと、リードコマンドを受け付けてからデータ出力回路54oによってリードデータが出力されるまでの時間を複数のコアチップ間において一致させる出力タイミング調整回路400とをそれぞれ含む。これにより、インターフェースチップ側における入力されるリードデータのラッチマージンを十分に確保することが可能となる。しかも、出力タイミングの調整を夫々のコアチップ側で行っていることから、インターフェースチップ側にコアチップの枚数分のラッチタイミング制御回路などを設ける必要もない。

(もっと読む)

センスアンプ回路及びそれを備えた半導体装置

【課題】低電圧の読み出し動作に際し十分な動作マージンと動作速度を確保し得るセンスアンプ回路を提供する。

【解決手段】シングルエンド型のセンスアンプ回路は、ゲート電圧Vgに応じてビット線BLを電位Vbに駆動しビット線BLとセンスノードNsとの間の接続を制御するMOSトランジスタQ1と、ゲートがセンスノードNsに接続され、ビット線BLに伝送される信号を増幅するトランジスタQ2と、2つのプリチャージ回路(Q3、Q6)を備えている。センス動作に先立ち、ビット線BLとセンスノードNsの電位設定を行い、ゲート電圧Vgを所定期間だけVg2に設定した後にVg1(Vg1<Vg2)に設定してビット線BLを所定電位Vbに駆動する。所定電位Vbは、読み出し電圧の範囲内で電荷転送モードと電荷分配モードとが切り換わる変化点の近傍で、ハイとローに対応してセンスノードNsで得られる所要の電圧差を確保可能な値に設定される。

(もっと読む)

51 - 60 / 327

[ Back to top ]