株式会社日立超エル・エス・アイ・システムズにより出願された特許

21 - 30 / 327

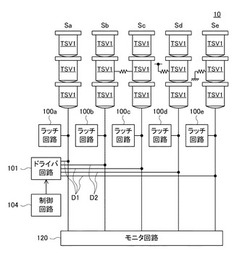

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

半導体装置

【課題】耐振性および耐衝撃性に優れたSSD装置を提供する。

【解決手段】SSD装置10は、配線基板11と、この配線基板11を収納する一対のケース(上側ケース12Aおよび下側ケース12B)とを備えている。配線基板11の下面には、NAND型フラッシュメモリチップが封止されたSOP21とコントローラチップが封止されたBGA23とが実装されている。BGA23と下側ケース12Bとの隙間に挟み込まれた、粘着性を有するゲル状シート26は、SSD装置10に加わる振動や衝撃のエネルギーを緩和、吸収し、配線基板11の撓みを抑制する。

(もっと読む)

IBISシミュレーションモデルの抽出方法

【課題】複数の半導体チップを内蔵する半導体装置について高精度なIBISシミュレーションモデルを簡易に抽出する方法を提供する。

【解決手段】共通の外部接続端子に接続される第1及び第2の半導体チップの第1及び第2の出力バッファの出力トランジスタを同時にトランジスタモデルとして扱ってトランジスタレベル回路シミュレーションを行い、IBISシミュレーションモデルにおける第1の出力バッファのAC特性モデルを抽出するステップと、第1及び第2の出力バッファのトランジスタレベル回路シミュレーションモデルにおける出力容量を加算して、IBISシミュレーションモデルにおける第1の出力バッファの出力容量モデルを算出するステップと、AC特性モデルと、出力容量モデルと、を用いて外部接続端子から見た第1の出力バッファのIBISシミュレーションモデルを合成するステップと、を備える。

(もっと読む)

ビデオエンコーダシステム

【課題】簡単な構成で使い勝手と用途の拡大に好適なビデオエンコーダシステムを提供する。

【解決手段】外部周辺機器から入力された入力信号を受けるビデオ受信部、ビデオ信部から出力される映像信号を受けて画像圧縮信号を形成するビデオエンコーダ、ビデオ信部から出力される音声信号を受けて音声圧縮信号を形成するオーディオエンコーダ、ビデオ受信部から出力される74.25MHzのビデオクロックを受けて第1STCカウンタ値を形成する第1STCカウンタ値生成部、第1STCカウンタ値を受けてPCRを生成するPCR生成部とを有する。第1STCカウンタ値生成部は、ビデオクロックの11サイクル毎に4回のインクリメントを行うカウンタ動作を行ってSTCカウンタ値を生成する。

(もっと読む)

半導体装置

【課題】テスト信号毎の専用配線を不要とし、配線領域を削減できるテスト回路を備えた半導体装置を提供する。

【解決手段】外部から供給されるテスト情報をデコーディングし、複数の信号を生成するDFTデコーダ202と、互いに従属接続した複数のDFTレジスタDFTr0〜DFTrnと、複数のDFTレジスタにそれぞれ対応する複数の制御回路(制御回路CKT0〜CKTn)と、複数のレジスタのうちの第1のレジスタ(DFTレジスタDFTr0)に複数の信号(シフトデータTSCANDATA)を供給するセレクタ(セレクタ113)と、セレクタのセレクティング回数を規定するカウンタ(9bitカウンタ112)と、複数の制御回路の数に対応するクロック周期の回数を、複数のレジスタ及びカウンタに供給するシフトクロック生成回路(シフトCK制御回路111)と、を備える。

(もっと読む)

半導体装置

【課題】少なくともメモリセルの情報をリフレッシュする際、グローバルビット線及びグローバルセンスアンプを動作させることなく再書き込み動作を行い、消費電流とチップ面積を低減可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、破壊読み出し型のメモリセルMCに接続されるローカルビット線LBLと、ローカルビット線に対応するグローバルビット線GBLと、再書き込み回路(Q7、Q8)を含むローカルセンスアンプLSAとを備え、例えば、メモリセルMCに対するリフレッシュ動作時は、ローカルビット線LBLがグローバルビット線GBLに接続されない状態になって再書き込み回路(Q7、Q8)が動作するので、グローバルビット線GBLに信号を伝送させることなく、メモリセルMCへの情報の再書き込みが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

半導体装置

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

半導体装置

【課題】センスアンプのセンスマージンを拡大する。

【解決手段】2つの素子分離領域3に隣接して各ウェル1,2にドライバトランジスタ4a,5a,4b,5bをそれぞれ配置し、各ウェル1,2にドライバトランジスタ4a,5a,4b,5bよりも素子分離領域3a,3bから離れた位置にクロスカップルされた2つの一対のセンストランジスタ6a乃至9a、6b乃至9bをそれぞれ配置する。これにより、センストランジスタ6a乃至9a、6b乃至9bと夫々対応する素子分離領域3a,3bと間に一定以上の距離が確保されることから、素子分離領域3a,3bからの距離によってトランジスタのしきい値が変化する現象の影響が低減され、その結果、夫々クロスカップルされた一対のトランジスタの特性を正確に一致させることが可能となる。

(もっと読む)

半導体装置

【課題】バンクごとに中間バッファの段数が異なっていても、高速動作を実現する。

【解決手段】半導体装置1は、それぞれリード時にカラムスイッチ12a〜12gが導通するタイミングを示す複数の第1の制御信号と、それぞれライト時にカラムスイッチ12a〜12gが導通するタイミングを示す複数の制御信号とを生成する制御回路20を備える。制御回路20は、外部からリード指示を受けてから、各メモリセルアレイ11a〜11fから読み出された該データがFIFO回路14aへ到達するタイミングがバンク間で互いに等しくなるよう、上記複数の第1の制御信号を活性化し、各カラムスイッチ12a〜12gが、外部から第1のデータ入出力端子15aに入力されるライトデータが対応する当該カラムスイッチに到達するタイミングにマッチングするよう、上記複数の第2の制御信号を活性化する。

(もっと読む)

21 - 30 / 327

[ Back to top ]