株式会社日立超エル・エス・アイ・システムズにより出願された特許

11 - 20 / 327

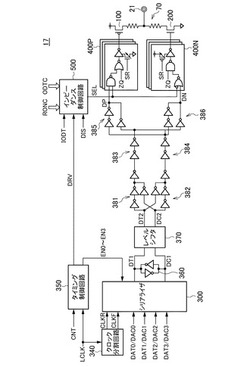

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】不良電流パスの選別に要する時間を短縮する。

【解決手段】半導体装置は、それぞれ少なくとも1つの貫通電極を含み、インターフェイスチップ内に第1のノードn1を有する複数の電流パス101Xと、互いに異なる複数の電圧値からなる比較電圧DACOUTを生成する比較電圧生成部102と、複数の電流パス101Xそれぞれの第1のノードn1の電圧TSVCXと、比較電圧DACOUTの上記複数の電圧値それぞれとを比較し、比較の結果を示す比較結果信号CMPXを電流パス101Xごとに出力する比較部103と、比較結果信号CMPXに応じて、複数の電流パス101Xのそれぞれが高抵抗化しているか否かを示す結果信号RESLTXを生成する結果信号生成部104とを備える。

(もっと読む)

半導体装置設計方法および半導体装置設計支援プログラム

【課題】EBDに近いモデリング精度を維持しつつ、モデリングの効率を高める。

【解決手段】複数のチップ(CHIP1〜4)が積層され、それぞれのチップが共通の外部端子104に接続される積層型の半導体装置100の設計に関する。まず、電磁界解析ツールにより、外部端子104とチップを接続するプリント基板配線(共通配線106、個別配線108)の電気的なパラメータを算出し、それらをEBDのパラメータとして設定する。設定されたパラメータに基づいて半導体装置100の電気的な特性をシミュレーション計算する。パラメータの計算・設定に際しては、所定の配線、たとえば、共通配線106や個別配線108などのプリント基板配線の長さを示すパラメータをゼロに設定する。

(もっと読む)

演算処置装置およびマイクロコンピュータ

【課題】システム処理とフィルタ処理の双方の負荷を軽くすることができ、消費電力の向上や性能の向上を図ることが可能な技術を提供する。

【解決手段】デジタル・シグナル・プロセッサDSPにおいて、プログラム・メモリPM、プログラム・カウンタPC、制御論理回路CLを有し、各命令のビット・フィールド内には、命令停止フラグ情報(TRIG_WAIT)とビット・フィールド情報(TRIG_WHAT)とを持つ。そして、制御論理回路CLは、TRIG_WAITがクリアされている命令はそのまま実行し、次の命令処理に進み、TRIG_WAITがセットされている命令は、TRIG_WHATに対応する実行再開トリガ条件が成立していなければその実行を行わずに停止し、TRIG_WHATに対応する実行再開トリガ条件が成立していればその実行を行い、次の命令処理に進む、ように制御する。

(もっと読む)

ネットワーク接続受信側装置および時刻同期化システム

【課題】同期パケットの周期を意図的に変動させても同期精度に影響せず、ネットワークの遅延変動を測定するしくみが不要な受信側装置、およびこの受信側装置を備えた時刻同期化システムを提供する。

【解決手段】時刻同期化システムの受信側装置において、受信側装置のローカルクロック発生器のカウント値(カウンタ22)の変化傾きが、送信側装置から受信したタイミングパケットに含まれるタイムスタンプに基づくカウント値(カウンタ12)の変化傾きに一致するように、受信側装置のローカルクロック発生器のクロック間隔を調整し、さらに、受信側装置のローカルクロック発生器のクロックの位相を、送信側装置から受信したタイミングパケットの位相に一致するように調整する。

(もっと読む)

半導体記憶装置

【課題】遅延変動量を軽減し、ビット線の遅延を良好に追跡することができる半導体記憶装置を提供する。

【解決手段】SRAMにおいて、列方向に配置された複数のレプリカ・ビット線rplbt[0]〜[p]と、レプリカ・ビット線にそれぞれ接続された複数のレプリカ・メモリセルRPLCELLと、レプリカ・ビット線にそれぞれ接続された複数のインバータINV[0]〜[p]とを有する。更に、レプリカ・ビット線同士は共通に接続され、インバータの入力端子はレプリカ・ビット線にそれぞれ接続され、インバータの出力端子同士は共通に接続されてセンスアンプイネーブル信号が生成される。そして、センスアンプイネーブル信号がセンスアンプに供給されることによって、ビット線の読み出し信号がセンスアンプにより増幅され、センスアンプの出力端子から読み出しデータが生成される。

(もっと読む)

コンピュータシステム及び揮発性メモリ装置

【課題】DRAMなどの揮発性メモリ装置に係わり、リフレッシュ時に必要な消費電力の低減を実現できる技術を提供する。

【解決手段】本コンピュータシステム1は、DRAM2とCPU4を含んで成り、例えばCPU4側にデータ反転制御回路100を備える。データ反転制御回路100は、DRAM2への書き込み時(a)のデータにおける所定幅の書込データ単位ごとに、値“1”の数が過半数かどうかを判定し、過半数である場合は、値“1”/“0”を反転処理する。またデータ反転制御回路100は、DRAM2からの読み出し時(b)のデータにおける所定幅の読出データ単位ごとに、上記反転状態の値“1”/“0”を反転処理して復元し、読み出しデータとする。上記構成により、DRAM2におけるリフレッシュ動作の対象となる値“1”が記憶されるメモリセルの数を少なくする。

(もっと読む)

半導体装置

【課題】貫通電極を用いた積層型の半導体装置において、被制御チップに供給する電源電圧を安定化させる。

【解決手段】基板電源端子91Vが設けられたインターポーザIPと、一方の表面に表面バンプFBが設けられ、他方の表面に裏面バンプBBが設けられたインターフェースチップIFと、インターフェースチップIFに接続されたコアチップCCとを備える。インターフェースチップIFに設けられ、基板電源端子91Vに接続された表面バンプFB、裏面バンプBB及びこれらを接続する貫通電極TSV1の積層方向から見た平面的な位置は互いに一致しており、その配列ピッチP1よりも信号用の裏面バンプBBの配列ピッチP2の方が小さい。本発明によれば、インターポーザIPからコアチップへストレートに電源を供給することができることから、コアチップに供給する電源電圧を安定化させることが可能となる。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

11 - 20 / 327

[ Back to top ]