株式会社SUMCOにより出願された特許

111 - 120 / 1,197

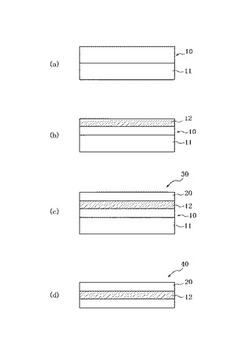

エピタキシャルウェーハおよびその製造方法

【課題】デバイス活性層へのオートドーピングやミスフィット転位が発生し難く、且つ、デバイス形成後に薄厚化されても不純物金属によるデバイス活性層の汚染を有効に抑制することができるエピタキシャルウェーハおよびその製造方法を提供する。

【解決手段】シリコン基板の表面から内部に向かってV族原子を拡散させて形成した、濃度:2×1013atoms/cm3以上1×1018atoms/cm3以下のV族原子を含有してシリコン基板の表層に位置するバリア層と、バリア層上に形成したシリコンエピタキシャル膜よりなるデバイス活性層とを備えることを特徴とするエピタキシャルウェーハである。また、バリア層形成工程と、デバイス活性層形成工程とを含むエピタキシャルウェーハの製造方法である。

(もっと読む)

シリコンウェーハの製造方法

【課題】デバイス製造工程における熱処理を経た後にも高抵抗を維持するシリコンウェーハを高い生産性を以て製造する方法を提供する。

【解決手段】設定抵抗率に応じてドーパントを添加してシリコンインゴットをチョクラルスキー法により成長させ、該シリコンインゴットをスライスして前記設定抵抗率を有するシリコンウェーハを製造するに当たり、設定抵抗率毎に、シリコンウェーハを供するデバイス作製工程における熱処理後の該シリコンウェーハの熱処理後抵抗率のウェーハ厚み方向のプロファイルを、複数のシリコンインゴット酸素濃度において予め求めておき、前記プロファイルにおいて、熱処理後抵抗率がピークとなる深さまでのウェーハ表面からの厚みが、デバイスのチップ形成領域より厚いプロファイルを有する、酸素濃度となる条件にてシリコンインゴットの成長を行うようにする。

(もっと読む)

シリコンウェーハの製造方法

【課題】デバイス製造工程における熱処理を経た後にも高抵抗を維持するとともに、ウェーハの機械的強度及びゲッタリング能力が高い高抵抗シリコンウェーハを製造する方法を提供する。

【解決手段】チョクラルスキー法により設定抵抗率に応じてドーパントを添加してシリコンインゴットを成長させ、該シリコンインゴットをスライスして設定抵抗率を有するシリコンウェーハを製造するに当たり、設定抵抗率毎に、シリコンウェーハを供するデバイス作製工程における熱処理後の当該シリコンウェーハの熱処理後抵抗率と当該シリコンウェーハが切り出されたシリコンインゴットの酸素濃度との相関を予め求めておき、シリコンインゴットの成長を、該インゴットの設定抵抗率に対する相関において、導電型が逆転する酸素濃度未満となる条件にて行う。

(もっと読む)

ウェーハの欠陥検出方法

【課題】ウェーハ上のLPDを検出して結晶欠陥と付着異物とに分類する精度を向上させる方途を提供する。

【解決手段】ウェーハの表面に対して垂直の方向に照射させる垂直照射光の該照射表面からの散乱光のうち、高角度範囲に散乱する散乱光の検出強度から照射表面における輝点欠陥の第1のサイズを求め、照射表面に対して斜めの方向に入射させる斜め照射光の該照射表面からの散乱光のうち、低角度範囲に散乱する散乱光の検出強度から輝点欠陥の第2のサイズを求め、輝点欠陥を、第2のサイズに対する第1のサイズの比および予め求めた閾値に基づいて結晶欠陥と付着異物とに分類するに際し、垂直入射光の波長と斜め入射光の波長とを異ならせるようにする。

(もっと読む)

シリコンウェーハ表層部のエッチング方法およびシリコンウェーハの金属汚染分析方法

【課題】気相エッチング法によりシリコンウェーハ表層部を短時間で均一にエッチングするための手段を提供すること。

【解決手段】弗化水素酸と硫酸との混酸Aを収容した密閉容器内に、混酸Aと接触しないようにシリコンウェーハを配置し、次いで、窒素酸化物を含む硝酸水溶液である溶液Bを前記密閉容器内に導入して混酸Aと混合し、混酸Aと溶液Bを混合した溶液から蒸発するガスによって前記密閉容器内で前記シリコンウェーハ表層部を気相分解する。

(もっと読む)

電着固定砥粒ワイヤ

【課題】被切断材料の切断溝からのチップの高い掻き出し効率を確保することができるとともに、固定砥粒の磨滅に伴う切断効率の低下を抑制することができる電着固定砥粒ワイヤを提供する。

【解決手段】ワイヤ基材の外周面に、所定の粒度を有する第1の固定砥粒が線状に電着された第1の線状電着部と、第1の固定砥粒より粒度が小さい第2の固定砥粒が線状に電着された第2の線状電着部とを離間して形成したので、被切断材料の切断溝からのチップの高い掻き出し効率を確保でき、固定砥粒の磨滅に伴う切断効率の低下を抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長によりトレンチ内を不純物層で埋め込む場合に、不純物層の不純物濃度の面内均一性が悪くなることを抑制しつつ、スループットを向上させる。

【解決手段】p型領域3を形成するためのトレンチ2aの幅を狭くしておき、このトレンチ2a内をp型層21で埋め込んだのち、それを熱拡散してトレンチ2aよりも幅広なp型領域3を形成する。このように、トレンチ2aの幅をトレンチJ2aの幅よりも狭くしていることから、トレンチ2a内をエピタキシャル成長にて埋め込むときの体積を少なくすることが可能となる。このため、エピタキシャル成長に必要とされる時間を短時間化することが可能となり、スループットを向上させることが可能となる。また、同じ条件でのエピタキシャル成長によって不純物層であるp型層21を形成できるため、p型層21の不純物濃度の面内均一性が悪くなることを抑制することもできる。

(もっと読む)

半導体基板の製造方法

【課題】トレンチをエピタキシャル膜にて埋め込んで半導体基板を製造する上においてトレンチ開口部の塞がりの抑制と成長速度の向上の両立を図ることができる半導体基板の製造方法を提供する。

【解決手段】n+シリコン基板1の上に形成したn型エピタキシャル膜2に、複数のトレンチ4を、トレンチ幅Wtよりも、隣接するトレンチ4間の間隔Ltを大きく形成する。トレンチ4内を含めたエピタキシャル膜2上に、エピタキシャル膜2の不純物濃度よりも高濃度なp型エピタキシャル膜23を、少なくともトレンチ4の埋め込みの最終工程において、p型エピタキシャル膜23の成膜のために供給するガスとして、シリコンソースガスとハロゲン化物ガスとの混合ガスを用いて成膜し、トレンチ4の内部をp型エピタキシャル膜23で埋め込む。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長によりトレンチ内を不純物層で埋め込む場合に、スループットを向上させることができる半導体装置の製造方法を提供する。

【解決手段】p型領域3を形成するためのトレンチ2aの幅を広くしておき、このトレンチ2a内をp型層で埋め込んだのち、n-型ドリフト層2からn型不純物を熱拡散してトレンチ2aよりも幅狭なp型領域3を形成する。このように、トレンチ2aの幅をトレンチJ2aの幅よりも広くしていることから、トレンチ2a内をエピタキシャル成長にて埋め込むときにより成長レートを高くできる条件でエピタキシャル成長させられる。このため、エピタキシャル成長に必要とされる時間を短時間化することが可能となり、スループットを向上させることが可能となる。

(もっと読む)

多結晶シリコンウェーハ及びその製造方法

【課題】高効率な発電パネル用の多結晶シリコンウェーハを提供する。

【解決手段】一辺が118mm以上の四角形である多結晶シリコンウェーハであって、第1乃至第4の外周領域a1〜a4と、いずれも外周領域にも属さない中央領域bとを含み、第1の外周領域a1におけるライフタイムは、中央領域bにおけるライフタイムよりも短く、第2及び第3の外周領域a2,a3におけるライフタイムは、中央領域bにおけるライフタイムと実質的に等しく、中央領域bにおけるライフタイムは、30μs以上である。本発明によれば、多結晶シリコンインゴットの断面をマトリクス状に4分割又は6分割することによって切り出すことができるとともに、ライフタイムが30μs以上である領域を全体の1/3以上とすることができる。これにより、16%以上の変換効率を確保することが可能となる。

(もっと読む)

111 - 120 / 1,197

[ Back to top ]