ルネサスエレクトロニクス株式会社により出願された特許

991 - 1,000 / 8,021

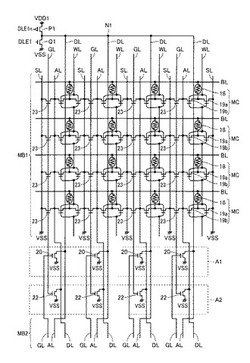

半導体記憶装置

【課題】半導体基板の表面の空き領域が少ない半導体記憶装置を提供する。

【解決手段】このMRAMの各メモリセルMCは、磁気抵抗素子18と2つのアクセストランジスタ19a,19bを含み、トランジスタ19a,19bのドレインを磁気抵抗素子18を介して対応のビット線BLに接続し、それらのゲートを対応のワード線WLに接続し、それらのソースをそれぞれソース線SLおよび補助配線ALに接続する。したがって、アクセストランジスタ19bのソースとDLドライバ14に含まれるドライバトランジスタ23のソースとを共通化することができ、シリコン基板31の表面の空き領域を減らすことができる。

(もっと読む)

ティーチングシステム

【課題】従来技術によるティーチング方法では、位置を調整して、プロセスチャンバーを真空状態にして、位置のずれを顕微鏡で確認して、プロセスチャンバーを大気状態に戻して、また位置を調整する、という繰り返しを行うので、長い時間を必要とする上、気圧の変化を伴う作業は効率が悪い。さらに、顕微鏡を用いた作業者の目視による検査は、誤差が比較的大きい。

【解決手段】顕微鏡の代わりにCCDカメラ31を用い、ヒーターの基準位置に相当する第1の画像マーカーAを用い、シャドウリング18の中心位置の代わりに相当するアダプターリング調整治具17に設けられた第2の画像マーカーBを用いる。これら2つの画像マーカーAおよびBをCCDカメラ31にて測定し、アダプターリング調整治具17の位置を調整する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】アプリケーション実行効率をよりよくすることができる半導体集積回路及びその制御方法を提供すること

【解決手段】本発明にかかる半導体集積回路は、スキャンチェーンを有するプロセッサと、プロセッサにアプリケーションを実行させるプロセッサ制御部と、プロセッサのスキャンテストを制御するスキャンテスト制御部と、を有する。そして、スキャンテスト制御部がスキャンテストを実行している際に、プロセッサ制御部からのスキャンテスト中断要求があった場合、スキャンテストを中断し、アプリケーションの実行後に、スキャンテストを再開させるものである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】樹脂封止型の半導体装置の信頼性低下を抑制する。

【解決手段】キャップ(部材)2とキャビティ部(空間形成部)5dを備えるキャップ(部材)5を重ね合わせて接合することで、密封された空間8が形成され、空間8内にセンサチップ(半導体チップ)1および複数のワイヤ4を配置する半導体装置を以下のように製造する。キャップ2とキャップ5の接合部を封止する封止工程において、キャップ5の上面5a全体と、キャップ2の下面2b全体がそれぞれ露出するように樹脂から成る封止体9を形成する。これにより、封止工程において、キャップ5を押し潰す方向に作用する圧力を低減することができる。

(もっと読む)

半導体装置

【課題】封止材の充填不良(ボイド)が抑制され、封止材の注入速度を速めることを可能な半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ10に形成された電極をなす複数の外部端子11と、パッケージ基材20に形成された複数の引出配線21とが接合され、複数の外部端子11及び複数の引出配線21が封止材により封止されたものである。半導体チップ10においては、複数の外部端子11からなる外部端子列12が、外部端子列12の延びる方向に対して交差する方向に複数配列しており、かつ、複数の外部端子列12において、複数の外部端子11のうち2以上がチップ辺10Eに対して交差する方向に同軸配列している。

(もっと読む)

半導体装置の製造方法

【課題】薄型化したチップをダイボンディングする工程において、ウエハシートからチップをピックアップする際に、ピックアップ対象のチップを正確に認識できる技術を提供する。

【解決手段】カメラCAM1は鏡筒KT1の一端と接続され、鏡筒KT1の他端には対物レンズが取り付けられ、この対物レンズを通してチップ1Cの主面の画像を撮影する構成とし、鏡筒KT1とチップ1Cとの間には、面発光照明SSL1、拡散板KB1およびハーフミラーTK1を内部に備え、カメラCAM1と同じ光軸でチップ1Cの主面に光を照射する同軸落射照明の機能を有する鏡筒KT2を配置する。

(もっと読む)

論理回路の遅延計算・タイミング検証方法および遅延検証装置

【課題】より実動作に近いタイミング判定を行う。

【解決手段】遅延計算・タイミング検証方法は、被検証回路を示すネットリストを保持するステップと、被検証回路に含まれる順序回路間のパスを抽出するステップと、順序回路の出力がメタステーブル状態になることを許容して設定されるセットアップ時間およびホールド時間を示す緩和制約時間に対する入力信号のタイミング余裕度を算出するステップと、タイミング余裕度に基づいて、順序回路の出力信号の値が確定する出力遅延時間を算出するステップと、順序回路間のパスにおける遅延時間を示す伝搬遅延時間を算出するステップと、出力遅延時間と伝搬遅延時間と緩和制約時間とに基づいてタイミング検証するステップとを具備する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

半導体集積回路

【課題】コンデンサの供給する電源電圧の低下により、誤動作を起こす虞がある。

【解決手段】通常動作より低い消費電力状態である低消費電力モードを有する半導体集積回路であって、前記低消費電力モード状態時に、電源電圧レベルを検出する検出手段と、前記検出した電源電圧レベルを記憶する記憶手段と、前記通常動作時よりも小さい電流を流すことで、前記電源電圧を低下させる擬似負荷手段と、前記擬似負荷手段により電流を流す前に前記記憶手段で記憶した第1の電圧レベルに応じて前記検出手段の検出レベルを第2の電圧レベルに切り換える切換え手段と、前記擬似負荷手段により電流を流すことにより低下した前記電源電圧が、前記第2の電圧レベルとなるかを判定し、前記低消費電力モードを解除するか否かの制御を行う制御手段と、を有する半導体集積回路。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

991 - 1,000 / 8,021

[ Back to top ]