ルネサスエレクトロニクス株式会社により出願された特許

1,051 - 1,060 / 8,021

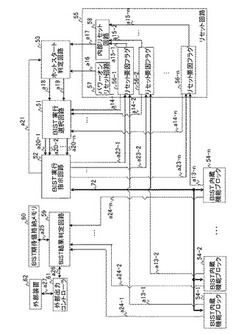

自己診断回路および自己診断方法

【課題】マイクロコンピュータの自己診断の実行時間を削減する。

【解決手段】リセット後の動作がホットスタートかコールドスタートかを判定する手段と、各機能ブロックで発生するエラーが他のどの機能ブロックへ影響があるのかの関連付け情報を保持し、通常動作時に発生したエラーがどのブロックで発生したエラーであるかを判定し、複数の機能ブロックからBISTを実行する機能ブロックを選択する手段と、選択された機能ブロックのBISTを実行する順序を関連付け情報に基づいて制御して、BISTの実行を指示する手段と、を備え、ホットスタートと判定された場合には、BISTを実行する機能ブロックを選択するとともに、選択した機能ブロックのBISTを実行する順序を関連付け情報に基づいて制御してBISTを実行し、コールドスタートと判定された場合には複数の機能ブロックのすべてのBISTを実行する。

(もっと読む)

信号配線システム及びジッタ抑制回路

【課題】従来は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することが難しかった。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

(もっと読む)

コントラスト補正回路及びコントラスト補正方法

【課題】表示動画の明暗変化に対する輝度補正動作の追従性を高めることが望まれている。

【解決手段】ブロック輝度積算部10は、入力フレームが分割されたブロックに属する輝度値の積算値に等しいブロック輝度値を生成する。ブロック輝度値格納部30は、1以上前のフレームのブロック輝度値を保持する。時間平滑化フィルタ部20は、ブロック輝度積算部10によって生成されたブロック輝度値に応じて、当該生成されたブロック輝度値に対してブロック単位で対応関係にあるブロック輝度値格納部30に保持されたブロック輝度値を更新する。平均輝度値フィルタ部40は、更新された複数のブロック輝度値の重みづけに基づいて、ブロックの構成画素単位で平均輝度値を生成する。コントラスト補正部70は、平均輝度値フィルタ部40により生成された平均輝度値に応じた条件で輝度値を補正する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

電源電圧検出回路

【課題】簡単な構成で電源投入時にも精度よく電源電圧の状態を検出する。

【解決手段】第1スイッチ(122)と第2スイッチ(124)とは直列に接続されてスイッチ部を形成し、第1スイッチ(122)は、基準信号に基づいて開閉が制御される。判定信号生成回路(110)は、第1電源電圧(VDD)と第2電源電圧(VSS)とに基づいて電源電圧判定信号(VG)を生成し、第2スイッチ(124)は、電源電圧判定信号(VG)に基づいて開閉が制御される。第1負荷素子(126)は、第1電源電圧(VDD)とスイッチ部との間に直列に挿入される。スイッチ部は、基準信号(Vref)が所定の第1電圧を超え、電源電圧判定信号(VG)が所定の第2電圧を超えたとき回路を閉成して第1負荷素子(126)に電流を供給し、第1負荷素子(126)とスイッチ部との接続ノードから第1電源電圧(VDD)の状態を示す第1出力信号(VOUT)を出力する。

(もっと読む)

半導体集積回路装置

【課題】低電圧でSRAM回路を動作させるために構成するトランジスタのしきい値電圧を下げると、トランジスタのリーク電流の増加により、データを記憶しながら動作していない状態での消費電力が増加するという問題がある。

【解決手段】SRAMメモリセルMC内の駆動MOSトランジスタのソース線sslの電位を制御することでメモリセル内のMOSトランジスタのリーク電流を低減する。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

光ディスク再生装置

【課題】ディフェクト領域が時間的に長い場合には、データを正しく取得できすデータエラーが発生する。そのため、ディフェクト領域に関わらずDCレベルの変動を抑制することでデータエラーの発生を防ぐ光ディスク再生装置が望まれる。

【解決手段】図1に示す光ディスク再生装置は、再生RF信号のオフセット調整が可能なオフセット調整回路と、オフセット調整回路の出力信号に対してAGC動作又は保持動作切り替えが可能であり、補正後RF信号を出力するAGC回路と、光ディスクの特性を示す特性信号を複数出力する特性検出回路と、ディフェクト領域に関わらず一定の値を出力する特性信号と差分基準値との差分を積分し、オフセットを調整する積分回路と、ディフェクト領域で値が変化する特性信号と特性基準値と比較することで、AGC回路におけるAGC動作と保持動作を切り替える制御回路と、を備える。

(もっと読む)

半導体装置

【課題】III族窒化物半導体を主材料として含むFETにおいて、ゲート−ドレイン間に高電圧を印加した場合でも、素子の劣化が発生し難くし、より信頼度を高くしたFETの提供。

【解決手段】基板上10に、[0001]または[000−1]結晶軸に平行な成長モードにて、格子緩和したバッファ層11、チャネル層12、電子供給層13をこの順にそれぞれIII族窒化物半導体を用いて形成された積層構造にあって、バッファ層11と電子供給層13の内、チャネル層12のIII族原子面側にある層は、チャネル層12のV族原子面側にある層よりもa軸長が大きく、電子供給層13は、チャネル層12よりもバンドギャップが大きい、電界効果トランジスタを備える。

(もっと読む)

マルチコアプロセッサシステム、共有リソース制御方法及びスレッド制御装置

【課題】安全かつプロセッサコアの並列利用性を高めたマルチコアプロセッサシステム及びその共有リソース制御方法ならびに制御装置を提供する。

【解決手段】複数のプロセッサコアと、スレッドにより共有されうる複数のリソースと、リソース毎にセマフォを付与し、リソースのシーリング値に基づいてスレッドによるリソースの操作時の排他制御を行い、セマフォの組み合せに対して優先プロセッサコアを設定する。第2のプロセッサコア上で実行される第2スレッドが要求した第1のセマフォが、第1のプロセッサコアの第1スレッドにより取得済であり、第2のプロセッサコア上の任意のスレッドが第2のセマフォを取得済である場合、プロセッサコアが優先プロセッサコアでなければ、第2のセマフォを解放させる。

(もっと読む)

1,051 - 1,060 / 8,021

[ Back to top ]