ルネサスエレクトロニクス株式会社により出願された特許

1,071 - 1,080 / 8,021

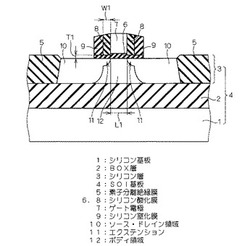

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

半導体装置

【課題】相変化メモリを低電圧動作および高温の動作又は放置させる場合に、記録保持信頼性を向上させる技術を提供する。

【解決手段】読み出し電圧をセット電圧およびリセット電圧以上として高速動作させ、読み出し後に読み出し前の状態を再書込みする、いわゆる破壊読出しを行う。または、複数個のセルを用いて1ビットの情報を記録する、いわゆるオアセルを用いて、高温時の動作又は放置のける信頼性を向上させる。破壊読出しおよびオアセルを用いた相変化メモリに必要な、回路構成および動作方法を用いる。

(もっと読む)

データ受信装置、データ受信方法及びプログラム

【課題】トレーニング中の初期化シンボルの一部が破損していた場合であっても、受信データを正常にデコードする。

【解決手段】受信装置は、初期化信号を生成する初期化信号生成部9と、初期化信号により初期化されるデスクランブラにより受信データをデスクランブルするデスクランブル回路10とを有する。受信データは、高速シリアル通信の接続を確立するための、1以上のTSnオーダーセットを含むトレーニング用データセットを有し、TSnオーダーセットは、1以上のCOMシンボルと1以上のCOMシンボル以外のデータとからなる。初期化信号生成部9は、トレーニング用データセットに含まれる最終のTSnオーダーセットを構成するCOMシンボルのうち少なくとも最終のCOMシンボルがデスクランブル回路10に入力される初期化最終タイミングでデスクランブル回路10を初期化する初期化信号を生成する。

(もっと読む)

半導体記憶装置及びその誤り訂正方法

【課題】メモリセルの保持電流が基準電流以上(データの誤りが発生しない)の場合において、消費電流の発生を削減する。

【解決手段】メモリセルが正しいデータを保持できなくなる限界を示す第1基準電流と、第1基準電流より基準値を高くした第2基準電流とを切り替えていずれか一方を基準電流として、メモリセルの保持電流と前記基準電流とを比較することによってデータを読み出すメモリセルアレイ1と、メモリセルアレイ1から読み出されたデータの誤り検出を行う誤り検出回路2と、保持電流が第2基準電流を下回るまで、所定の期間毎にデータの誤り検出を行うように誤り検出回路2を制御する制御部(ホスト機器4、誤り検出動作要求回路5)と、誤り検出回路2が誤りを検出した場合、メモリセルアレイ1より読み出されたデータに対して誤り訂正処理を施す誤り訂正回路3と、を備える。

(もっと読む)

ツェナーダイオード、半導体装置及びそれらの製造方法

【課題】生産性がより良く、より安定したツェナーダイオード及びその製造方法を提供する。

【解決手段】ツェナーダイオードは、基板11とベース拡散層12と第1ポリシリコン層14aと第2ポリシリコン層14bとを具備している。基板11は第1導電型である。ベース拡散層12は、基板11の表面近傍に設けられ、第2導電型である。第1ポリシリコン層14aは、ベース拡散層12上に設けられ、第2導電型である。第2ポリシリコン層14bは、第1ポリシリコン層14a上に設けられ、第2導電型である。第1ポリシリコン層14aの第2導電型の不純物濃度は、第2ポリシリコン層14bの第2導電型の不純物濃度よりも高い。

(もっと読む)

経路案内装置、経路案内装置の動作方法、及び制御プログラム

【課題】分岐点が連続する場合でも、曲がるべき分岐点を瞬時に判断することができる、経路案内装置、経路案内装置の動作方法、及び制御プログラムが提供する。

【解決手段】現在地から目的地までの経路を探索する経路探索部と、前記経路上に存在する分岐点群により複数の区間に分割するデータ分割部と、分割後データを生成するデータ分割部と、各分岐点における進行方向を生成する分岐点判定部と、前記分割後データに基づき、各区間ごとの長さの対応関係を示すグラフデータを生成するグラフ作成部と、前記グラフデータを表示する表示部とを具備し、前記グラフデータは、各区間に対応する複数のバーを有する棒グラフデータを含み、前記グラフ作成部は、前記進行方向データに基づいて、右左折するべき区間を示すバーを右左折バーとして特定し、特定したバーが他の区間を示すバーとは異なる色で表示されるように、前記棒グラフデータを生成する。

(もっと読む)

半導体集積回路装置

【課題】アナログ・ディジタル変換回路ブロックを備えた半導体集積回路装置において、信頼性の高い断線検出を実現する。

【解決手段】例えば、入力ポートA[k]とアナログ・ディジタル変換回路ADCの入力端子Ainの間に設けられPMOSトランジスタMP1,MP2,MPcおよびNMOSトランジスタMN1,MN2,MNcを含んだT型スイッチ回路TS[k]と、Ainを電源電圧VCCAにプリチャージするPMOSトランジスタMPuを備える。A[k]から信号入力端子Vint[k]までの断線有無を検出する際に、まず、MPuを介してAinをVCCAにプリチャージすると共に、MN2,MP2をオンに、MN1,MP1,MPc,MNcをオフに駆動する。次いで、MPuをオフに制御すると共に、MN1,MN2,MP1,MP2をオンに、MPc,MNcをオフに制御する。

(もっと読む)

半導体集積回路のタイミング解析システム、タイミング解析方法及びプログラム

【課題】統計的STAの実行時間を短縮できるタイミング解析システムを提供する。

【解決手段】本発明のタイミング解析システムは、ばらつき要素をばらつき要素マージ部に入力するばらつき要素入力部と、2種類のばらつき要素のばらつきを、1種類のばらつき要素のばらつきにマージするばらつき要素マージ部と、マージしたばらつき要素を使用して統計的STAを実行する統計的STA実行部とを備える。

(もっと読む)

半導体集積回路及び故障検出方法

【課題】電源分離回路への電源供給を制御する複数の電源スイッチから、不良スイッチを特定する。

【解決手段】電源スイッチ群21は、第1電源101と複数の電源供給端子103〜105との間の接続を制御する複数の電源スイッチ120〜122を備える。電源分離回路11は、複数の電源供給端子103〜105の各々に対応して接続される複数の内部回路140〜142を備える。スイッチング素子131、132は、通常動作モードにおいて、複数の電源供給端子103〜105のそれぞれの間を短絡し、テストモードにおいて、複数の電源供給端子103〜105のそれぞれの間を分離する。複数の電源供給端子103〜105における電圧VSDは、複数のモニタ端子161〜163に監視可能に出力される。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】LSIのレイアウト設計において、TAT(Turn Around Time)を増加させることなくタイミング収束を実現する。

【解決手段】LSIのレイアウト設計方法は、レイアウト対象の集積回路のネットリストに基づいて、前記集積回路をクロックドメインに分けることでクロックドメイン回路集合体に区分する工程と、前記クロックドメイン回路集合体の各々に対するタイミング制約を作成する工程と、所定の基準に基づいて前記クロックドメイン回路集合体間の配置順序を決定する工程と、前記クロックドメイン回路集合体を前記配置順序に従って配置し配線することにより前記集積回路のレイアウトを作成する工程とを備える。レイアウト設計後のタイミング収束のTATを短縮することが可能となる。

(もっと読む)

1,071 - 1,080 / 8,021

[ Back to top ]