ルネサスエレクトロニクス株式会社により出願された特許

1,081 - 1,090 / 8,021

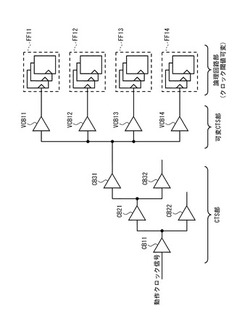

半導体装置

【課題】従来の半導体装置では、クロックツリーにおける消費電流を削減しながら、同期回路間の同期動作を行うことが難しかった。

【解決手段】本発明にかかる半導体装置は、動作クロック信号CLKに応じて第1のクロック信号を出力し、第1の応答時間で第1のクロック信号のエッジを変化させる第1のクロックバッファ(VCB11〜VCB14のうちの一つ)と、動作クロック信号CLKに応じて第2のクロック信号を出力し、第2の応答時間で第2のクロック信号のエッジを変化させる第2のクロックバッファ(VCB11〜VCB14のうちの他の一つ)と、第1のクロック信号に同期して動作し、第1の電圧レベルを閾値電圧とする第1の論理回路と、第2のクロック信号に同期して動作し、第2の電圧レベルを閾値電圧とする第2の論理回路と、を有し、第1、第2の論理回路は、動作クロック信号に応じて一のタイミングで動作する。

(もっと読む)

データ処理装置およびそのデータ処理方法

【課題】可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能なデータ処理装置を提供すること。

【解決手段】データ処理装置100は、SIMD方式の複数のPE1(5)と、複数のPE1(5)のそれぞれに対応して設けられる複数のSRAMs2と、複数のPE2(7)とを含む。複数のPE1(5)のそれぞれは、対応する1つのSRAMs2に格納されるデータに対して演算を行なう。また、複数のPE2(7)のそれぞれは、対応する複数個のSRAMs2に格納されるデータに対して演算を行なう。したがって、複数のSRAMs2を共有することができ、可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能となる。

(もっと読む)

圧電素子の駆動装置

【課題】放電時に出力電圧を制御電圧に追従させることができる圧電素子の駆動装置を提供する。

【解決手段】充電回路11は、第1のノードN2を通じてピエゾ素子50を充電する。放電回路16は、第1のノードN2を通じてピエゾ素子50に充電された電荷を放電する。制御回路83は、ピエゾ素子50に印加されている電圧の大きさと制御電圧の大きさの比較に基づいて、放電回路16に放電動作をさせるか、または充電回路11に充電動作をさせるかを切替える。

(もっと読む)

半導体集積回路

【課題】記憶装置に記憶された機密データが容易に改ざんされたり読み出されたりすることを防止することが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路10は、複数のCPU暗号キーを格納するCPU暗号キー格納部60と、複数のCPU暗号キーのうち何れかのCPU暗号キーをCPU暗号キー格納部60の中から選択して出力するCPU30と、CPU30によって選択されたCPU暗号キーと、外部から供給された外部暗号キーと、に基づいて内部暗号キーを生成する内部暗号キー生成回路40と、CPU30から出力されたアドレス信号A0〜Anを内部暗号キーに基づいて変換し、アドレス信号B0〜Bnとして出力するアドレス変換回路50と、を備える。

(もっと読む)

TAB(TapeAutomatedBonding)テープ、及び、半導体装置の製造方法

【課題】開口と、当該開口に先端が延在しているリードとを有するTAB(Tape Automated Bonding)テープにおけるリード変形を軽減する。

【解決手段】開口12を有する絶縁性フィルム6と、絶縁性フィルム6上から開口12内に延在し、半導体チップに環状に配置された複数の第1パッド各々に開口12内で接続する複数の第1リード3a、及び、第1パッドよりも外周側に環状に配置された複数の第2パット各々に開口12内で接続する複数の第2リード3bと、開口12内に位置し、複数の第1リード3aと繋がり、第2リード3bとは繋がらないリード端部保持部材13とを有するTABテープ。

(もっと読む)

データ解析装置、統合プログラム生成装置、および、データ解析システム

【課題】センサから収集したアナログデータを、センサの個数および種類に応じて効率よく解析できるようにすること。

【解決手段】データ解析装置は、接続されたセンサから受けたアナログデータを出力するとともに接続されたセンサの個数および種類を識別するセンサ接続部と、センサ接続部から出力されたアナログデータをデジタルデータに変換するAD変換部と、AD変換部から出力されたデジタルデータをシリアルデータからパラレルデータに変換するシリアル・パラレル変換部と、シリアル・パラレル変換部から出力されたパラレルデータの中からデータを選択するセレクタ部と、セレクタ部により選択されたデータを処理する演算部と、センサ接続部により識別されたセンサの個数および種類に応じて、AD変換部、シリアル・パラレル変換部、セレクタ部および演算部のうちの少なくともいずれかを制御する制御部と、を有する。

(もっと読む)

画像表示制御回路、画像表示制御方法、及び画像表示システム

【課題】3D眼鏡なしでも左右の画像のクロストークを低減した画像表示制御回路、画像表示制御方法、及び画像表示システムを提供する。

【解決手段】画像表示システム1は、フレームシーケンシャル方式に対応した3D画像用の画像制御回路17、表示装置14及び3D眼鏡15を有する。画像制御回路17は、左右の画像を保存するフレームメモリ13と、入力画像のフレームレートに同期した入力クロックの周期をN(Nは2以上の整数)倍にした出力クロックを生成するPLL18と、出力クロックを使用し、フレームメモリ13に保存された左右の画像を異なるフレーム数の比率で読み出すよう制御する制御回路11とを有する。

(もっと読む)

データパルス検証方法及びその検証システム

【課題】従来技術では、ラッチ回路間のデータパス上を伝達されるデータパルスがラッチ回路のデータ入力端子以外で消失する場合、そのデータパルスの消失を判定できなかった。

【解決手段】同一クロックドメインのラッチ回路間のデータパスのデータパルス検証方法であって、前記データパス上の出力側回路素子から入力側回路素子に伝達されるデータ信号のデータパルスから、回路の動作上問題とならないダータパルス(グリッチ)を除外し、クロックエッジをまたがるデータパルスのパルス幅を算出し、前記算出されたパルス幅と、前記入力側回路素子の最小パルス幅制約とを比較するデータパルス検証方法。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気メモリにおいて、安定的且つ容易に磁壁を導入可能な構造とする。

【解決手段】磁気メモリは、磁気記録層10と、非磁性層11を介して磁気記録層10に接続された参照層12と、磁気記録層10より下方に設置された第1、2磁化固定層19、20とを具備する。磁気記録層10及び参照層11は垂直磁気異方性を有する。磁気記録層10は、反転可能な磁化を有し参照層11と重なる磁化反転領域2と、磁化反転領域2の第1境界に接続され、磁化の向きが第1方向に固定された第1磁化固定領域1と、磁化反転領域2の第2境界に接続され、磁化の向きが第1方向と反平行な第2方向に固定された第2磁化固定領域3とを備える。第1、2磁化固定層19、20は、第1、2磁化固定領域1、3の磁化を固定する。第2磁化固定層20が、第1磁化固定層19と比較して保磁力が低い。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびプログラム

【課題】配線およびダミーパターンが配置された領域の割合を各メタル層において均一に保ちつつ、ダミーパターンの生成によって生じたタイミングエラーを解消できるようにすること。

【解決手段】レイアウト設計装置は、配線およびダミーメタルが配置されたメタル層において、エラーを生じた配線の周囲に配置された複数のダミーメタルの中から該エラーの原因となったダミーメタルを抽出し、該メタル層を分割して得られた複数の領域のそれぞれにおいて、配線およびダミーメタルを含むメタルが占める割合であるメタル密度が該メタル層に対して規定された所定のメタル密度以上となるようにしつつ、該エラーが解消されるように、抽出したダミーメタルの中から削除すべきダミーメタルを選択するダミーメタル選択部と、選択されたダミーメタルを削除するダミーメタル変更部と、を備えている。

(もっと読む)

1,081 - 1,090 / 8,021

[ Back to top ]