ルネサスエレクトロニクス株式会社により出願された特許

1,101 - 1,110 / 8,021

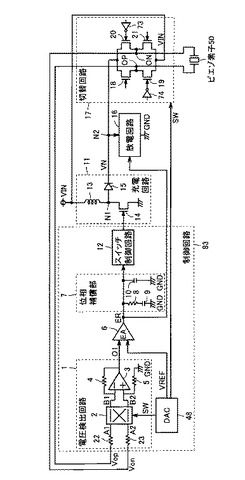

圧電素子の駆動装置

【課題】放電時に出力電圧を制御電圧に追従させることができる圧電素子の駆動装置を提供する。

【解決手段】充電回路11は、第1のノードN2を通じてピエゾ素子50を充電する。放電回路16は、第1のノードN2を通じてピエゾ素子50に充電された電荷を放電する。制御回路83は、ピエゾ素子50に印加されている電圧の大きさと制御電圧の大きさの比較に基づいて、放電回路16に放電動作をさせるか、または充電回路11に充電動作をさせるかを切替える。

(もっと読む)

半導体集積回路

【課題】記憶装置に記憶された機密データが容易に改ざんされたり読み出されたりすることを防止することが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路10は、複数のCPU暗号キーを格納するCPU暗号キー格納部60と、複数のCPU暗号キーのうち何れかのCPU暗号キーをCPU暗号キー格納部60の中から選択して出力するCPU30と、CPU30によって選択されたCPU暗号キーと、外部から供給された外部暗号キーと、に基づいて内部暗号キーを生成する内部暗号キー生成回路40と、CPU30から出力されたアドレス信号A0〜Anを内部暗号キーに基づいて変換し、アドレス信号B0〜Bnとして出力するアドレス変換回路50と、を備える。

(もっと読む)

データ解析装置、統合プログラム生成装置、および、データ解析システム

【課題】センサから収集したアナログデータを、センサの個数および種類に応じて効率よく解析できるようにすること。

【解決手段】データ解析装置は、接続されたセンサから受けたアナログデータを出力するとともに接続されたセンサの個数および種類を識別するセンサ接続部と、センサ接続部から出力されたアナログデータをデジタルデータに変換するAD変換部と、AD変換部から出力されたデジタルデータをシリアルデータからパラレルデータに変換するシリアル・パラレル変換部と、シリアル・パラレル変換部から出力されたパラレルデータの中からデータを選択するセレクタ部と、セレクタ部により選択されたデータを処理する演算部と、センサ接続部により識別されたセンサの個数および種類に応じて、AD変換部、シリアル・パラレル変換部、セレクタ部および演算部のうちの少なくともいずれかを制御する制御部と、を有する。

(もっと読む)

TAB(TapeAutomatedBonding)テープ、及び、半導体装置の製造方法

【課題】開口と、当該開口に先端が延在しているリードとを有するTAB(Tape Automated Bonding)テープにおけるリード変形を軽減する。

【解決手段】開口12を有する絶縁性フィルム6と、絶縁性フィルム6上から開口12内に延在し、半導体チップに環状に配置された複数の第1パッド各々に開口12内で接続する複数の第1リード3a、及び、第1パッドよりも外周側に環状に配置された複数の第2パット各々に開口12内で接続する複数の第2リード3bと、開口12内に位置し、複数の第1リード3aと繋がり、第2リード3bとは繋がらないリード端部保持部材13とを有するTABテープ。

(もっと読む)

半導体装置

【課題】高ダイナミックレンジかつ高精度かつ低雑音であり、さらに高線形性を有する可変利得増幅器を提供する。

【解決手段】可変利得増幅回路35は、出力ノードOUTp,OUTnと、複数の増幅器Amp1〜Amp18と、検出回路40とを備える。複数の増幅器は、出力ノードと基準ノードVSSとの間に互いに並列に接続され、制御信号GCS2に応じて選択的に動作状態になる。検出回路は、入力信号Vinの大きさに応じた検出信号Idetを各増幅器に出力する。各増幅器は、第1のトランジスタM1と、第2のトランジスタM3と、バイアス回路53とを含む。第1のトランジスタは、入力信号または入力信号に比例した信号を制御電極に受ける。第2のトランジスタは、第1の基準ノードと出力ノードとの間に第1のトランジスタと直列に接続される。バイアス回路は、検出信号に応じた大きさの直流電圧を第2のトランジスタの制御電極に印加する。

(もっと読む)

バスシステムおよびアクセス制御方法

【課題】各バスマスタからバススレーブへ複数のバスを経由してアクセスする場合であってもバスの使用効率の低下を抑制することができるバスシステムを提供することである。

【解決手段】本発明にかかるバスシステムは、複数のバスマスタ1_1〜1_4から少なくとも一つのバススレーブ5への、複数のバス2_1〜2_3を経由したアクセスを制御するバスシステムである。バス2_1〜2_3は各々、前段から入力される複数のアクセス要求16、17を調停し、当該調停により選択されたアクセス要求を次段へ出力する調停部8を備える。調停部8は、アクセス要求16、17がバスで待機した時間を差し引くことで次段へ出力されるアクセス要求29に含まれる許容待ち時間情報を更新する。

(もっと読む)

半導体装置の製造方法

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

(もっと読む)

プリアンプ回路、及びマイクロフォン

【課題】低ノイズ特性を持つプリアンプ回路を提供すること

【解決手段】プリアンプ回路は、ソースフォロアとして機能するPMOSトランジスタM1A及びM1Bを備える。さらにプリアンプ回路は、差動増幅器として対となって機能するPMOSトランジスタM2A及びM2Bを備える。M1AのゲートとM2Bのゲートとが、可変容量C2を介して接続される。M1BのゲートとM2Aのゲートとが、可変容量C1を介して接続される。M1Aのソースと、M2Aのドレインと、が接続される。M1Bのソースと、M2Bのドレインと、が接続される。M2Aのソースと、M2Bのソースと、が接続される。

(もっと読む)

半導体装置

【課題】耐タンパ性を有する、可変論理機能を実現するための記憶回路を有する半導体装置を提供する。

【解決手段】制御回路24は、記憶回路23の次の読出しアドレスを先に記憶回路23から読出した制御フィールドの情報または外部イベント入力に基づいて自律的に制御することが可能である。正規デコーダ28は、制御回路24から出力されるアドレスをデコードし、デコード結果に基づいて、データフィールドの少なくとも1つの正規メモリセルと、制御フィールドの少なくとも1つのメモリセルを選択する。冗長制御回路51は、イネーブル信号が活性化された場合に限り、制御回路24から出力されるアドレスと、所定の正規メモリセルのアドレスとが一致したときに、正規デコーダ28による選択を禁止し、データフィールドの少なくとも1つの冗長メモリセルと制御フィールドの少なくとも1つの冗長メモリセルを選択する。

(もっと読む)

1,101 - 1,110 / 8,021

[ Back to top ]