富士通セミコンダクター株式会社により出願された特許

2,021 - 2,030 / 2,507

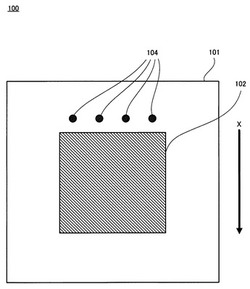

半導体装置の製造方法

【課題】回路基板と半導体素子との隙間に充填されたアンダーフィル樹脂内のボイドの発生を防止して、半田バンプの接続信頼性を高める。

【解決手段】まず、回路基板101の表面に半導体素子102が実装される。次に、回路基板101と半導体素子102との隙間に、流動性を有するアンダーフィル樹脂が充填される。次に、回路基板101と半導体素子102との隙間に充填されたアンダーフィル樹脂が硬化される。ここで、上記のアンダーフィル樹脂が回路基板101と半導体素子102との隙間に充填される際には、半導体素子102の側面に対向する複数の位置から回路基板101と半導体素子102との隙間にアンダーフィル樹脂が供給される。

(もっと読む)

試験装置及び試験方法

【課題】探針の針先の異常を発見することが可能な試験装置及び試験方法を提供すること。

【解決手段】基板載置台5と、基板載置台5に載せられたウエハWに試験信号を与える探針8が設けられたプローブカード7と、探針8の画像を得る撮像部4と、試験を行う前と後での探針8の画像の違いから、該探針8の針先が異常かどうかを判定する判定部9とを有する試験装置による。

(もっと読む)

電極の形成方法

【課題】半田バンプ等の外部接続用電極の形成に於いて、当該外部接続用電極の組成の種類・選択の自由度を高めることができると共に、当該外部接続用電極の組成を容易に制御することができ、更に洗浄処理工程数を減少させることができる電極の形成方法を提供する。

【解決手段】電極の形成方法は、表面に導体層36が露出する被処理基板31を用意する工程と、前記被処理基板31の表面に、前記導体層36が露出する第1の開口37Aaを有する第1のマスク37Aを形成する工程と、前記第1の開口37Aa内に、第1の金属から成る第1の金属層39をめっき処理により形成する工程と、前記第1の金属層39上に、第2の金属から成る第2の金属層40を前記めっき処理とは異なる方法により形成する工程と、前記第1の金属層39及び前記第2の金属層40を熱処理により合金化する工程と、を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 下部電極の耐酸化性を維持しつつ、微細化しても加工の困難性が高まらない半導体装置の製造方法を提供する。

【解決手段】 半導体基板の上に、Ti膜を成膜する。このTi膜の上に、貴金属膜を形成する。Ti膜及び貴金属膜を窒化雰囲気中で熱処理を行う。これにより、Ti膜中から貴金属膜の上面まで拡散したTiを窒化し、貴金属膜の表面の一部の領域にTiN構造物が形成される。表面の一部には貴金属膜が露出した状態が維持される。貴金属膜及びTiN構造物の上に誘電体膜を形成する。この誘電体膜の上に上部導電膜を形成する。Ti膜、貴金属膜、誘電体膜、及び上部導電膜をパターニングして、キャパシタを形成する。

(もっと読む)

露光データ作成方法及び露光方法

【課題】本発明は、露光データ作成方法及び露光方法に関し、未知のばらつきを含む様々なプロセスばらつきに対してパターン間の線幅のばらつきを低減することを目的とする。

【解決手段】パターン毎に露光量を調整しながら露光対象物を露光する荷電粒子ビーム露光用の露光データ作成方法において、パターンを目標線幅で分類し、各目標線幅のパターン群に対して、基準となる露光量とレジストパターンの出来上がり線幅の関係を示す基準特性を設定し、各目標線幅のパターンの露光量とレジストパターンの出来上がり線幅の関係を示す特性が基準特性に揃うように形状及び露光量を補正して露光データを作成するように構成する。

(もっと読む)

研磨制御システム、研磨制御プログラム及び半導体装置の製造方法

【課題】複数品種の研磨対象の研磨を簡便かつ高精度で行う。

【解決手段】研磨処理部2で複数品種の研磨対象について研磨を行い、膜厚測定部3でその研磨前後の膜厚を測定する。プロセス制御部4では、研磨レート比算出部7が、膜厚と研磨時間を用いて研磨レート算出部5で算出される実測研磨レートと、その研磨対象の品種名、研磨時間、メンテナンス後の研磨回数及びメンテナンス回数を用いた重回帰分析を行い、各品種の研磨レート比を算出する。以後は、その研磨レート比を用いて、研磨時間算出部6で算出される研磨時間が次の研磨対象の品種に応じて調整され、研磨処理部2は、その調整後の研磨時間で次の研磨を実施する。複雑なモデル式やパラメータを用いず、複数品種の研磨対象について実測したデータを用いて、複数品種の高精度な研磨プロセス制御に対応することができる。

(もっと読む)

フォトマスクの異物除去方法及び異物除去装置

【課題】フォトマスクを露光装置に装填する前のパージ作業時に、成長性の異物の発生を誘発することなくフォトマスク上の異物を除去する。

【解決手段】フォトマスク1に対して略水平方向から圧力が調整されたパージガス4を吹付けてフォトマスク1表面にパージガス4による層流を形成し(図1(A))、パージガス4の吹付け方向またはパージノズル3のフォトマスク1表面からの高さを変化させてパージガス4をフォトマスク1表面に吹付ける(図1(B)、図1(C))。また、パージガス4の吹付け時には、パージガス4またはフォトマスク1表面を熱する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極をフルシリサイド化したMISFETを有する半導体装置及びその製造方法に関し、MISFETの特性劣化を引き起こすことなくゲート電極をフルシリサイド化しうる半導体装置の製造方法、並びに、そのような製造方法を用いて形成された優れた特性のMISFETを有する半導体装置を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜18と、ゲート絶縁膜18上に形成された金属シリサイド膜56bと、金属シリサイド膜56b上に形成された金属シリサイド膜56aとを有し、金属シリサイド膜56bにおける金属元素に対するシリコンの組成が、金属シリサイド膜56aにおける金属元素に対するシリコンの組成よりも大きいゲート電極26nと、ゲート電極26nの両側の半導体基板10内に形成された不純物拡散領域対54とを含むトランジスタを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の耐久性並びに信頼性を向上させる。更に、半導体装置のクラックの検査を簡素化し、クラックの検出率を向上させる。

【解決手段】半導体装置100は、配線基板110上に設けられた半導体素子120と、半導体素子120を封止する封止樹脂とを備え、封止樹脂は、半導体素子120を封止する封止用樹脂150の部分と、封止用樹脂150の部分の側壁から外側に延在する複数の延出部151とを備える。また、延出部151の部分には、切欠き151aが形成されている。そして、外部衝撃により発生するクラックが切欠き151a付近に発生することにより、半導体装置の耐久性並びに信頼性が向上する。また、クラックの検査が簡素化し、その検出率が向上する。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路においてコストの増大を伴うことなく外部端子の異常状態(出力短絡状態および入力開放状態)を検出する技術を提供する。

【解決手段】 半導体集積回路(MCU)は、複数の入出力回路(IO1〜IO4)、監視対象指定回路(DPSEL)および異常検出回路(PCDET)を備える。複数の入出力回路(IO1〜IO4)は、複数の外部端子(P1〜P4)に対応して設けられる。監視対象指定回路(DPSEL)は、複数の外部端子(P1〜P4)の中から監視対象外部端子を可変指定する。異常検出回路(PCDET)は、監視対象外部端子に対応する入出力回路が出力回路として機能している場合に監視対象外部端子の出力短絡状態を検出し、監視対象外部端子に対応する入出力回路が入力回路として機能している場合に監視対象外部端子の入力開放状態を検出する。

(もっと読む)

2,021 - 2,030 / 2,507

[ Back to top ]