富士通セミコンダクター株式会社により出願された特許

261 - 270 / 2,507

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

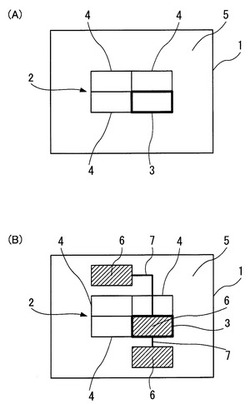

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

OFDM受信装置

【課題】複数のOFDMブランチを利用してOFDM信号を受信するOFDM受信装置の受信特性を向上させる。

【解決手段】各ブランチにおいてOFDM信号が周波数領域信号に復調される。ダイバーシティ合成部107は、各ブランチにより得られる復調信号を合成する。クロック再生部1は、OFDM信号のクロックを再生する。ガード相関部2は、OFDM信号の位相誤差を検出する。判断部7は、信頼性の高いブランチを特定する。クロック誤差補正部8は、信頼性の高いブランチの位相誤差の平均値に基づいて、補正指示を作成する。各ブランチのクロック再生部1は、それぞれ補正指示に従ってクロックの誤差を補正する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

比較回路及びアナログデジタル変換回路

【課題】動作電圧に対して入力電圧範囲を拡大し、低消費電力化を図ること。

【解決手段】比較回路10の電圧制御部12は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。入力トランジスタT11,T12のしきい値電圧と等しく設定されたトランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、比較部11に供給する制御電圧VCM(ノードN21の電圧)をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。

(もっと読む)

半導体装置及びその製造方法

【課題】セキュリティを高めるための半導体装置を提供する。

【解決手段】第1トランジスタ4a、および第1トランジスタ4aに接続される第1キャパシタ4bを有する第1メモリセル4を含む第1メモリセルアレイ2と、第1トランジスタ4aよりもオフ電流が高い第2トランジスタ5a、および第2トランジスタ5aに接続される第2キャパシタ5bを有する第2メモリセル5を含む第2メモリセルアレイ3と、を有する。

(もっと読む)

情報処理装置

【課題】 パイプライン処理の停止を低減するとともに、ループ処理が実施されている期間のアクセス効率を向上する。

【解決手段】 情報処理装置は、命令を取得するフェッチ部と、命令を解読するデコード部と、フェッチ部から出力される命令を順次記憶する書き込み動作と、ループ処理の範囲に対応する命令を繰り返し出力する読み出し動作とを切り替えて実施する命令バッファ部と、書き込み動作が実施されているとき、フェッチ部から出力される命令をデコード部に出力し、読み出し動作が実施されているとき、命令バッファ部から出力される命令をデコード部に出力する選択部とを有している。

(もっと読む)

無線通信装置及び無線通信方法

【課題】通信情報が悪意ある者によって解読されることを抑制する。

【解決手段】無線通信装置10は、互いに異なる識別情報を有し、それぞれアクセスポイントとして機能する複数の無線通信部11−1〜11−nを有し、無線通信部11−1〜11−nの少なくとも1つは、自身を送信先とした偽の通信情報の送信を繰り返すことで、正規のアクセスポイントの通信情報を隠すことができ、正規のアクセスポイントの通信情報が悪意のある者に解析され難くすることができる。

(もっと読む)

フィルタリング処理回路とそれを有するマッチング回路

【課題】簡単な回路構成で高速にフィルタリング処理を行う。

【解決手段】異なる視点での2つの画像に対する複数のずれ量に対応する差分絶対値和のうち,最小差分絶対値和を抽出するフィルタリング処理回路であって,入力回路に入力される複数のずれ量にそれぞれ対応する複数の差分絶対値和が当該入力時点までで最小の差分絶対値和の場合に最小の差分絶対値和として保持する最小差分絶対値和保持回路と,次に小さい第2最小差分絶対値和を検出して保持する第2最小差分絶対値和検出回路と,入力時点までで最小の差分絶対値和でない場合には,当該入力差分絶対値和を第2最小差分絶対値和検出回路に入力し,最小の差分絶対値和である場合には,最小差分絶対値和保持回路で最小差分絶対値が更新されることに伴って最小差分絶対値和保持回路から出力される元の最小差分絶対値和を,第2最小差分絶対値和検出回路に入力するセレクタ回路とを有する。

(もっと読む)

偏在率算出方法、半導体装置の製造方法及びプログラム

【課題】レイアウトデータからCu残が発生しやすい品種やレイヤであるか否かを判定することのできる偏在率算出方法を提供する。

【解決手段】CPUは、検証レイヤにおいて所定サイズの検証エリア毎にパターン密度を算出するステップS13と、算出されたパターン密度を複数の密度範囲に分別し、各々の密度範囲に属するパターン密度の分布を示す複数の密度マップMAP0〜MAP7を生成するステップS14とを実行する。また、CPUは、各密度マップMAP0〜MAP7に所定量のプラスシフトを加えるステップS15と、パターン密度の密度差が第1基準値以上となる組み合わせの密度マップMAP0〜MAP7を重ね合わせ、両密度マップで重複した領域を抽出するステップS16とを実行する。CPUは、その抽出した領域の総面積を算出するステップS17と、算出した総面積と第2基準値とを比較するステップS18とを実行する。

(もっと読む)

半導体回路

【課題】簡単な回路構成で故障検出のための試験を行うことができる半導体回路を提供する。

【解決手段】シフトレジスタを有しシリアル−パラレル変換を行う変換回路24の故障検出を行うための試験時に、シフトレジスタの初段のフリップフロップFF1AのD入力に、その/Q出力BS2Aを供給することで、クロック信号CLKのサイクル毎に0、1を交互に繰り返す信号を試験パターンとして生成し、この試験パターンを用いて変換回路24の試験を行うようにして、回路規模の大きな試験回路を搭載しなくとも、簡単な回路構成で故障検出のための試験を行えるようにする。

(もっと読む)

261 - 270 / 2,507

[ Back to top ]