富士通セミコンダクター株式会社により出願された特許

231 - 240 / 2,507

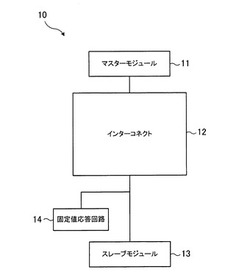

集積回路装置、検証装置及び検証方法

【課題】集積回路装置が仕様通りとなっているかの検証の容易化を図る。

【解決手段】集積回路装置10は、マスターモジュール11と、マスターモジュール11に接続されたインターコネクト12と、インターコネクト12によってマスターモジュール11の接続先とされるスレーブモジュール13を含む。集積回路装置10は更に、そのスレーブモジュール13に対してインターコネクト12から送信されてくる読み出し命令信号を受信する固定値応答回路14を含む。インターコネクト12から読み出し命令信号を受信した固定値応答回路14は、インターコネクト12によってマスターモジュール11の接続先とされたスレーブモジュール13固有の固定値を、インターコネクト12に送信する。この固定値に基づき、接続先が仕様通りか否かを検証する。

(もっと読む)

画像処理装置、画像処理方法、撮像装置

【課題】処理開始までの時間を短縮すること。

【解決手段】撮像部11は、1つのフレームの撮像データを分割した複数のフィールドの分割撮像データを出力する。センサI/F50は、撮像部11が出力する1番目のフィールドの分割撮像データをメモリ13に格納する。次いで、センサI/F50は、2番目のフィールドの分割撮像データをメモリ13に格納し、メモリアクセス部53はメモリ13から1番目のフィールドの分割撮像データを読み出す。演算部54は、2番目のフィールドの分割撮像データと、メモリアクセス部53によりメモリ13から読み出した1番目のフィールドの分割撮像データとを演算して最終フィールドに対応する分割撮像データを生成する。メモリアクセス部52は、最終フィールドに対応する分割撮像データを、メモリ13に格納する。

(もっと読む)

フォトマスク及びその製造方法

【課題】漏れ光を抑制し、高い寸法精度及び位置精度を実現しうるフォトマスク及びその製造方法を提供する。

【解決手段】透明基板の第1の領域上に形成されたデバイスパターンと、透明基板の第2の領域上に形成された周辺パターンと、周辺パターンが形成された領域の透明基板内に形成され、デバイスパターンをウェーハに露光する際に用いる露光光に対する周辺パターンの光透過部の透過率を、露光光に対するデバイスパターンの光透過部の透過率よりも低下させる改質層とを有する。

(もっと読む)

欠陥検査方法、半導体装置の製造方法及び欠陥検査装置

【課題】欠陥検出の精度を向上させることのできる欠陥検査方法を提供する。

【解決手段】ウェハ上に欠陥があるか否かを検査する第1の欠陥検査処理(ステップS11)を実行した後、その第1の欠陥検査処理にて検出された欠陥により、不良チップを判定する(ステップS12,S13)。続いて、不良チップを除いて、その不良チップに隣接するチップに欠陥があるか否かを、第1の欠陥検査処理よりも検査感度を上げて検査する(ステップS16)。

(もっと読む)

半導体装置の製造方法及半導体製造装置

【課題】 エッチングの終点を精度良く制御する。

【解決手段】エッチング装置1は、処理ユニット2と制御ユニット3とを有する。処理ユニット内のプラズマの発光強度は、OES検出器21で取得され、エッチング制御装置31が非線形回帰分析して回帰式を決定する。非線形回帰分析は、プラズマの発光強度がピークを超えた第1の時間までに取得したプラズマの発光強度を用いて行われ、回帰式を用いてエッチング終点となる第2の時間が算出される。エッチング終点は、第1の時間から発光強度が所定値だけ減少する時間として算出される。エッチング装置1は、エッチング終点に達したら、エッチングを終了する。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】入力部11は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)への書き込みを指示する複数パルスの書き込み信号を入力し、書き込み制御部12は、入力された書き込み信号のパルス数が所定数に達するまで、電気ヒューズ素子2への書き込みを無効状態にすることで、書き込み信号の信号線にノイズやグリッジのような連続性の少ないパルスがのっても、これらのパルスにより直ちに書き込みトランジスタ3がオンすることが抑制される。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成過程で、余分な酸化膜を確実に除去する。

【解決手段】貫通電極を形成するビアホール25の内面に酸化膜26を形成した後、Cu膜28を埋め込む。第1層間絶縁膜22の上に形成された余分なCu膜28をCMP法による研磨で除去するときに、酸化膜26も研磨されて膜厚が薄くなる。膜厚が薄くなった酸化膜26Bをハードマスクとして第1層間絶縁膜14に配線溝を形成する。このとき、酸化膜26Bの膜厚が薄くなる。配線溝に導電材を埋め込んだ後、余分な導電材を研磨によって除去する。このとき、残りの酸化膜26Bが全て研磨により除去される。

(もっと読む)

めっき装置及び半導体装置の製造方法

【課題】ウェハの周縁部で膜を正常に成長させることができるめっき装置を提供する。

【解決手段】めっき槽2内部に取り付けられた第1電極6と、めっき槽2の側壁5cにおいて、環状のフランジ7cを介してめっき槽2の内から外に向けて直径の小さい順に隣接する環状の第1、第2の開口部7a,7bと、第2の開口部7b内でフランジ7cの上に取り付けられるシールパッキン8と、シールパッキン8の上に、第2の開口部7bの内壁から離れて取り付けられる環状の第2の電極9と、第2の電極9に対向する位置に周縁を有するウェハ保持領域11xを有する第2の開口部7bよりも大きなウェハステージ11と、ウェハステージ11のウェハ保持領域11xの周囲の領域に形成され、シールパッキン8に一端が向けられる加圧用ホール11iと、ウェハステージ11を移動してめっき槽2の側壁5cに押し当てて前記第2の開口部7bを閉塞させる駆動部13とを有する。

(もっと読む)

出力バッファ回路及び入出力バッファ回路

【課題】流入電流の発生を抑制することができる出力バッファ回路を提供する。

【解決手段】出力バッファ回路1は、第1の高電位電源VDD1レベル又は低電位電源VSSレベルの出力信号OUT1を出力する第1出力回路10と、第1出力回路10とワイヤードオア接続され、第1の高電位電源VDD1よりも低電位である第2の高電位電源VDD2レベル又は低電位電源VSSレベルの出力信号OUT2を出力する第2出力回路20とを有している。また、出力バッファ回路1は、第1の高電位電源VDD1及び第2の高電位電源VDD2のうち第2の高電位電源VDD2のみが投入される場合に、第1出力回路10の高電位側の第1出力トランジスタT16及び第2出力回路20の高電位側の第2出力トランジスタT26の少なくとも一方のトランジスタのゲート電圧及びバックゲート電圧を第2の高電位電源VDD2レベルに設定する制御回路50を有している。

(もっと読む)

双方向スイッチおよびそれを利用した充放電保護装置

【課題】少ないトランジスタ数で双方向スイッチを構成する。

【解決手段】双方向スイッチ装置は,HEMTを有する双方向スイッチと,第1の条件時にHEMTのソースまたはドレインの一方の端子とゲートとの間に閾値電圧未満の第1の電圧を印加してソースまたはドレインの他方の端子から一方の端子への第1の電流パスをオフにし,第2の条件時に他方の端子とゲートとの間に閾値電圧未満の第2の電圧を印加して一方の端子から他方の端子への第2の電流パスをオフにし,第3の条件時にHEMTのソース及びドレインとゲートとの間に閾値電圧より高い第3の電圧を印加して第1,第2の電流パスをオンにする制御回路とを有する。

(もっと読む)

231 - 240 / 2,507

[ Back to top ]