ラムバス・インコーポレーテッドにより出願された特許

11 - 20 / 89

画像を取得し変換するための方法および装置

取得レンズにより、画像をローパスフィルタリングするステップと、画像センサを使用し、アップサンプリング係数を用いて、前述のローパスフィルタリングされた画像から、第1の解像度を有するアップサンプリングされた画像を生成するステップと、画像処理回路を用いて、前述のアップサンプリングされた画像を、前述の第1の解像度よりも低い第2の解像度を有するマルチレベル画像に変換するステップとを含む、画像を取得し、変換するための方法であって、前述の変換するステップが、前述のレンズの前述のローパスフィルタリングおよび前述のアップサンプリング係数に依拠する、方法。ギガピクセルセンサおよび慣例画像センサに適合される。  (もっと読む)

(もっと読む)

位置および動きを検出する指向性ビームステアリングシステムおよび方法

【課題】 コスト効率の高い正確な3次元追跡技術の要求を満たすこと。

【解決手段】 開示のゲーム機システムは、処理装置および送受信回路を有する本体を含んでいる。送受信回路は、処理装置と結合されており、受信回路および送信回路をそれぞれ含んでいる。第1のフェーズドアレイアンテナインタフェースが、処理装置に対する応答として、指向性信号の送信および受信を行う。本システムは、モバイルゲームコントローラを含んでおり、モバイルゲームコントローラは、指向性信号を受信し、方向を変えて第1のフェーズドアレイアンテナインタフェースに返す第2のフェーズドアレイアンテナインタフェースを含む。処理装置は、指向性信号に関連付けられたパラメータに少なくとも部分的に基づいて近接度データを生成し、近接度データは、ゲーム機本体に対するモバイルゲームコントローラの近接度を表す。

(もっと読む)

バイモーダル・データストローブを備えた集積回路

【課題】より高速で動作するシステムに対応すべくデータストローブを改良する。

【解決手段】2種の動作モードを有するメモリ素子130/440/450−1〜130/440/450−8。第一のモードにおいて、データストローブ170−1〜170−8はソース同期されていて、データの送信中である場合、メモリ素子により駆動される。第二のモードにおいて、メモリ素子はデータストローブを駆動しない。このモードでは、データストローブ信号170−1〜170−8は、書込データをサンプリングする自由継続クロックとして用いられる。コントローラ110/425による読込みデータの取得は、システム・クロックからの較正済み内部タイミング基準を用いてコントローラ110/425により計時される。

(もっと読む)

DRAMエラー訂正用のビット交換技術

【課題】 不良セルを交換セルに効率的にリマッピングすること。

【解決手段】 開示した実施形態は、ダイナミックメモリセルセットおよび交換ダイナミックメモリセルセットを含むダイナミックメモリ装置を提供する。交換ダイナミックメモリセルセットには、ダイナミックメモリセルセットにおける所定の不良セル用の交換データビットを含むデータセルと、不良セルを識別するアドレスビットを含むアドレスセルと、が含まれ、各データセルは、ダイナミックメモリセルセットにおける関連する不良セルを識別するアドレスセルのグループに関連付けられる。ダイナミックメモリ装置にはまた、リマッピング回路が含まれ、このリマッピング回路は、ダイナミックメモリセルセットにおける不良セルを、交換セルのセットにおける関連する交換セルにリマッピングする。

(もっと読む)

三次元メモリアレイ積層構造体

【課題】 改善された三次元メモリ(例えば、RRAM)アーキテクチャを提供すること。

【解決手段】 メモリデバイスが、平面基板と、平面基板の上方の複数の水平な導電性平面と、複数の水平な導電性平面と交互に配置される複数の水平な絶縁層とを備える。複数の導電性平面および絶縁層と直角である垂直な導電性列のアレイが、複数の導電性平面および絶縁層における開口部を通過する。メモリデバイスは、複数のプログラム可能なメモリ素子を備え、それぞれのメモリ素子が、水平な導電性平面の1つをそれぞれの垂直な導電性列に連結する。

(もっと読む)

インターフェースクロックマネージメント

同期インターフェースのタイミングはコントローラによってドライブ(駆動)されるクロック信号によって制御される。クロックは、インターフェースを介してメモリデバイスに対してコマンドを送信するようにトグリングされる。インターフェースを介して送信されるべきさらなるコマンドがない場合、コントローラはクロック信号をサスペンドする。メモリデバイスの準備が整っている場合、メモリデバイスは、信号をコントローラに返信する。この信号のタイミングはクロック信号に依存しない。コントローラによるこの信号の受信は、メモリデバイスの準備が整っており、コマンドのステータスがインターフェースを介して回復できるように、または別のコマンドをインターフェースを介して発行できるように、クロック信号がレジュームされるべきであることを示している。 (もっと読む)

無線カバレッジを向上させるための方法およびシステム

【課題】 様々な関連のないネットワークのための集中型の認証を促進することにより、向上した無線カバレッジを無線移動局に提供するための方法、装置、およびシステムについて説明する。その結果、移動局は改善されたカバレッジおよび帯域幅を得るために様々なネットワークを介してインターネット資源および電話資源にアクセスすることができる。

【解決手段】 一部の実施形態は、複数の仮想アクセスポイントであって、1つは企業に関連し、もう1つは複数のネットワークを介した移動体通信を促進するオーバーレイネットワークに関連する、複数の仮想アクセスポイントに区分化することができる無線アクセスポイントを使用してネットワークカバレッジの拡張をサポートする。1つの物理アクセスポイントが、1つの仮想アクセスポイントを使用して企業ネットワークをサポートし、別の仮想アクセスポイントを使用してオーバーレイネットワークをサポートすることができる。企業とつながりのないユーザは、企業ネットワークにアクセスすることなしに、その企業の物理アクセスポイントを介してオーバーレイネットワークにアクセスすることができる。

(もっと読む)

供給ノイズおよび終端ノイズの低減方法およびシステム

【課題】 SSNに関連する問題を軽減するシステムおよび方法を提供すること。

【解決手段】 シングルエンドの通信チャネルを介して第1の集積回路(IC)が第2のICと通信する通信システムを開示する。双方向基準チャネルは、第1のICおよび第2のIC間に延在し、両エンドで終端される。基準チャネルの各エンドにおける終端インピーダンスは、信号を異なる方向に通信するための異なるモードをサポートする。基準チャネルの終端インピーダンスは、それぞれの信号方向に最適化されることができる。

(もっと読む)

メモリ装置の構成可能メモリバンク

【課題】 データアクセスの粒度の制限を緩和し、柔軟なメモリシステムの設計を可能とすること。

【解決手段】 メモリ装置は、複数のアクセス可能メモリバンクおよび構成可能な1組の第1のメモリセグメントを有する、記憶アレイを有する。その複数のアクセス可能メモリバンクは、1組の第2のメモリセグメントを含む。第1の動作モード中、1組の第1のメモリセグメントが、追加のアクセス可能メモリバンクとなるように構成される。第2の動作モード中、1組の第1のメモリセグメント内の1対のメモリセグメントが、複数のアクセス可能メモリバンクのそれぞれの中の1組の追加のメモリセグメントとなるように構成される。

(もっと読む)

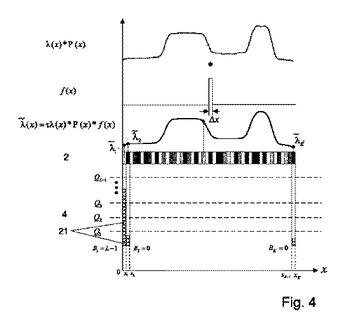

高分解能出力ドライバ

それぞれ、量子化ステップより実質的に大きい、公称インピーダンスを有し、量子化ステップより実質的に小さい、インピーダンスステップだけ、相互にインクリメント的に異なる、比較的に少数のサブドライバブランチまたはスライスを有する、高分解能出力ドライバ。一実装では、かかる「差動」または「非一様」サブドライバスライスは、n choose k等化器の個別の要素を実装し、各かかる差動サブドライバスライスは、一様要素インピーダンス較正DACによって実装される。別の実装では、一様スライス等化器の各構成要素は、差動スライスインピーダンス較正DACによって実装され、さらに別の実装では、差動スライス等化器の各構成要素は、差動スライスインピーダンス較正DACによって実装される。付加的セットの実装の実装では、等化およびインピーダンス較正機能は、階層的実装のネスト化された「DAC内のDAC」配設においてではなく、個別の並列セットのドライバブランチにおいて、双方向に実装される。かかる双方向配設を通して、等化器および較正器量子化の倍増が回避され、それによって、規定の範囲および分解能を満たすために要求されるサブドライバスライスの総数を減少させる。 (もっと読む)

11 - 20 / 89

[ Back to top ]