川崎マイクロエレクトロニクス株式会社により出願された特許

11 - 20 / 449

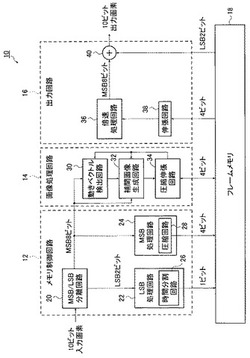

画像処理装置

【課題】メモリ容量を削減することができる画像処理装置を提供する。

【解決手段】画像処理装置は、複数のフレームの画素データを、フレームの順番に受信し、フレームメモリに記憶するメモリ制御回路と、フレームメモリに記憶された画素データの上位ビット部分を利用して処理済み画素データを生成する画像処理回路と、処理済み画素データを出力する出力回路とを備える。メモリ制御回路は、画素データを、上位ビット部分と下位ビット部分とに分離する分離回路と、下位ビット部分をフレームメモリに記憶する下位ビット処理回路とを含む。下位ビット処理回路は、それぞれのフレームの画素をn組(nは2以上の整数)に分割し、連続するnフレームの画素データを受信する期間に、分割したn組の画素のうちの対応する1つの組の画素の画素データのみの分離した下位ビット部分をフレームメモリに記憶する。

(もっと読む)

差動出力バッファ

【課題】本発明は、差動データ信号の変化を強調した強調済み差動データ信号を出力する差動出力バッファに関し、負荷容量や回路構成を大きく増やすことなく複数段にわたる高精度な強調を可能にする。

【解決手段】差動データ信号VIN,VIN_Bと、差動データ信号を所定の時間だけ遅延し、反転した、反転遅延差動データ信号EVIN_B,EVINとを、所定の比率で混合した、混合差動データ信号VB1,VB2を生成する混合回路12を有する混合段10Aと、複数の差動増幅等の組合せからなる出力段20Aとを備え、混合段10Aが、所要の強調量に応じて、混合回路12での差動データ信号と反転遅延差動データ信号との混合比を1:0、1:1、0:1のいずれかに設定する混合比設定回路を含む。

(もっと読む)

半導体装置および半導体集積回路の設計方法

【課題】本発明は、半導体集積回路を備えた半導体装置および半導体集積回路の設計方法に関し、IO領域を有効に利用しつつパッケージの高さ寸法の増大を有効に抑えた接続を可能とする。

【解決手段】半導体基板の表面の第1の辺に沿って、第1のIOセルと、第2のIOセルとを交互に配置したIO領域を有し、第1のIOセルは、第1の辺から所定の距離の位置に配置されたボンディングパッドを有し、第2のIOセルは、第1のIOセルのボンディングパッドより第1の辺から遠い位置にボンディングパッドを有し、かつ、第1のIOセルの少なくとも1つは、第1の辺から所定の距離の位置に配置された第1のボンディングパッドに加えて、第2のIOセルのボンディングパッドより第1の辺から遠い位置に、第2のボンディングパッドを有する第3のIOセルに置きかえられている。

(もっと読む)

半導体集積回路の設計方法

【課題】設計フローの負荷を増大させることなく、それぞれの回路モジュールに必要十分な容量セルを、それぞれの回路モジュールに近接配置することができる半導体集積回路の設計方法を提供する。

【解決手段】本発明は、それぞれが複数の論理セルを含む複数の回路モジュールからなる半導体集積回路の設計方法であって、複数の回路モジュールのそれぞれの、複数の論理セルおよび複数の論理セルの端子間の接続の情報を記述するネットリストに、複数の論理セルに電源を供給する電源配線間に接続されるセルであり、複数の論理セルのいずれとも独立で、かつ、複数の論理セルの端子と接続される端子を持たない容量セルの記述を追加し、複数の論理セルおよび複数の容量セルのレイアウトデータが格納されたセルライブラリを備えた設計支援システムを利用して、回路モジュールのそれぞれに対応する、複数の論理セルおよび容量セルを配置する配置領域を設定し、複数の論理セルおよび容量セルを対応する配置領域内に配置する工程を含む。

(もっと読む)

カレントミラー回路

【課題】ゲートリーク電流による影響を軽減させることができ、なおかつ、高周波ノイズに対する耐性を向上させることができるカレントミラー回路を提供する。

【解決手段】カレントミラー回路は、ミラー元となる第1のMOSトランジスタと、ミラー先となる第2のMOSトランジスタのゲートと、第1のMOSトランジスタのゲートと第2のMOSトランジスタのゲートとの間に、この順序で直列に接続された第4、第2、第1および第3の抵抗と、第1の抵抗および第3の抵抗の間のノード、ならびに、第2の抵抗および第4の抵抗の間のノードを入力とし、第1および第2の抵抗の間のノードを出力とする差動増幅回路とを備える。第3の抵抗は第1の抵抗よりも大きい抵抗値に設定され、第4の抵抗は第2の抵抗よりも大きい抵抗値に設定され、第3の抵抗は第4の抵抗よりも大きい抵抗値に設定されている。

(もっと読む)

電圧電流変換回路

【課題】0VからVDDの範囲でダイナミックに変化する差動入力電圧の全ての入力電圧範囲において出力電流を変化させることができる電圧電流変換回路を提供する。

【解決手段】電圧電流変換回路は、第1および第2の負荷抵抗と第1の電流源との間に接続された第1および第2のMOSトランジスタと、第1および第2の負荷抵抗と第2の電流源との間に接続された第3および第4のMOSトランジスタとを備える。第1および第4のMOSトランジスタのゲートには差動入力電圧の一方および他方が入力され、第2および第3のMOSトランジスタのゲートにはバイアス電圧が入力される。バイアス電圧は、差動入力電圧のいずれかが電源電圧のときを除いて第2および第3のMOSトランジスタの両方がオンする電圧に設定されている。

(もっと読む)

半導体集積回路および半導体集積回路装置

【課題】 電源電圧の安定した供給が可能な半導体集積回路および半導体集積回路装置を提供する。

【解決手段】 半導体集積回路40において、半導体基板の表面の、コア領域に、第1の電源が供給されて動作するコア回路が形成されるとともに、前記半導体基板の表面の前記コア領域の外側のI/O領域に、第2の電源が供給されて動作するI/O回路が形成された半導体集積回路40であって、前記半導体基板内に、該半導体基板を貫通して、前記第1の電源を供給する貫通ビア51が設けられ、前記半導体基板の表面のI/O領域に、前記第2の電源を供給するパッド46が設けられたことを特徴とする。

(もっと読む)

半導体集積回路およびそのテスト方法

【課題】サンプリングクロックの位相ノイズがDACおよびADCの変換特性に与える影響を検出することができ、ループバックテストのテスト品質を向上させることができる半導体集積回路およびそのテスト方法を提供する。

【解決手段】半導体集積回路は、サンプリングクロックに同期して動作し、デジタル信号をアナログ信号に変換するDACと、サンプリングクロックに同期して動作し、アナログ信号をデジタル信号に変換するADCと、基準クロックに基づいて、位相ノイズ特性の異なる第1および第2のサンプリングクロックを発生するサンプリングクロック発生回路と、DACから出力されるアナログ信号をADCに入力、あるいはADCから出力されるデジタル信号をDACに入力するループバックテスト時に、DACおよびADCの一方に第1のサンプリングクロックを供給し、他方に第2のサンプリングクロックを供給するサンプリングクロック切替回路とを備える。

(もっと読む)

演算処理装置

【課題】

条件分岐命令による実行効率の低下が抑えられた演算処理装置を提供する。

【解決手段】

それぞれが、命令を順次読み出す読出部と、命令に応じた演算を実行する演算実行部と、演算結果を記録する記録部とを有する2つのパイプライン処理部、2つのパイプライン処理部の一方を演算結果が有効な有効パイプラインとして指定し、他方を無効パイプラインとして指定するパイプライン指定部、および、条件分岐命令が読み出されたこと検知して、有効パイプラインの読出部には分岐命令に続く命令の読出しを継続させるとともに、無効パイプラインの読出部には条件分岐命令による分岐先の命令の読出しを行わせる条件分岐命令検知部を備え、パイプライン指定部は、有効パイプラインの演算実行部による演算の実行結果が条件分岐命令における分岐を意味する場合に、有効パイプラインと無効パイプラインの指定を切り替える。

(もっと読む)

画像信号生成装置

【課題】期待した精度のピクセルクロック以外で動作し続けることを防止する画像信号生成装置を提供する。

【解決手段】ソース側から画像情報とクロック情報と画素のデータと区切り信号とを受信する受信部と、クロック情報に基づいてピクセルクロックを生成するピクセルクロック生成部と、区切り信号のタイミングで初期値に初期化されるとともに、ピクセルクロックをカウントするカウンタと、カウンタのカウント値に基づいて、単位区間の画像信号を生成する画像信号生成部とを備えるとともに、初期値から最終値までの範囲内の複数の地点を、カウンタのカウント値が通過したときにトグルするフラグを記憶する複数のフラグ記憶器と、フラグの値に基づいて、ピクセルクロックの正常性を判定する判定回路とからなるピクセルクロック判定部とを備えることにより、上記課題を解決する。

(もっと読む)

11 - 20 / 449

[ Back to top ]