Fターム[2G132AD07]の内容

Fターム[2G132AD07]の下位に属するFターム

リングオシレータを用いるもの (13)

Fターム[2G132AD07]に分類される特許

161 - 180 / 393

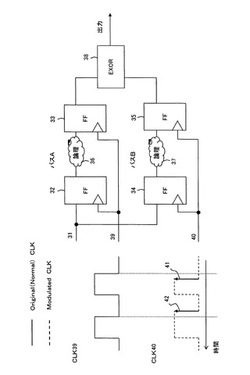

モニタ回路及び電力低減システム

【課題】LSIテスト時においても選別用のモニタリングを行うことができると共に、小さな面積で簡便な構成によりモニタ可能なモニタ回路を提供すること。

【解決手段】モニタ回路は、クロック信号39に同期して入力信号を取り込むフリップフロップ回路32と、クロック信号40に同期して入力信号を取り込むフリップフロップ回路34と、フリップフロップ回路34の出力信号を受ける論理回路37と、クロック信号40に同期して論理回路37の出力信号を取り込むフリップフロップ回路35とを含み、クロック信号40の立ち上がりエッジ位置を調整し、フリップフロップ回路32の出力信号とフリップフロップ回路35の出力信号とが所定の組合せとなったときの、調整したクロック信号40の立ち上がりエッジ位置とクロック信号39の立ち上がりエッジ位置とに基づいてチップの性能を判別する。

(もっと読む)

半導体装置

【課題】例えば数百MHzで高速動作する多行並列配置多段のシフトレジスタ回路を備えた半導体装置において、そのシフトレジスタ回路の規模(面積)が増大して配線遅延が顕在化する場合であっても、それ等のシフトレジスタ回路を実速度でエラー検査する。

【解決手段】N行並列配置M段のシフトレジスタ回路101のN行のうち例えば2行のシフトレジスタ回路を1組として、各組において、1組の2行のシフトレジスタ回路に対して入力回路102が共通の同一テストパターンを入力する。この1組の各行のシフトレジスタ回路からの出力同士を比較回路103で比較し、この比較結果のみを出力する。前記N行並列配置M段のシフトレジスタ回路101と前記比較回路103とは、数百MHzのクロック信号CKによって動作する。

(もっと読む)

半導体集積回路の高速テスト

【課題】本発明の課題は、半導体集積回路において全てのフリップフロップ間の高速テストを実施し、テスト漏れを防ぐことにより高品質の半導体集積回路を提供することにある。

【解決手段】半導体集積回路の高速テストにおいて、テスト開始後各フリップフロップのデータ出力端子が1回以上“0”から“1”または“1”から“0”に反転した場合に“1”を出力し続け、テスト開始後データ出力端子に全く変化がない場合は“0”を出力し続ける、もう一つの出力端子(判定端子と呼ぶ)を各フリップフロップが備えることを特徴とする。

(もっと読む)

半導体試験装置

【課題】3信号以上の同時測定を可能にするとともに同時試験可能なDUTの数を大幅に向上させることで試験に要する時間を大幅に短縮することができ、更にはDUTのピンの割り付けの自由度を大幅に向上させることができる半導体試験装置を提供する。

【解決手段】半導体試験装置1は、DUT20から得られる信号と所定の比較電圧とを比較した比較結果を出力するハイ側コンパレータ16及びロー側コンパレータ17を備える複数のピンエレクトロニクス回路11a〜11nと、ピンエレクトロニクス回路11a〜11nに対応して設けられ、トリガ信号Tr1が入力されてから対応するピンエレクトロニクス回路からの比較結果が入力されるまでの時間を測定する時間測定回路12a〜12nと、時間測定回路12a〜12nの測定結果に基づいて、DUT20から得られる複数の信号間の時間差を求める時間差演算部14とを備える。

(もっと読む)

試験装置、スキュー測定装置、デバイスおよびボード

【課題】スキュー測定時間を短くする。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスに対して信号を出力する複数のドライバと、複数のドライバのそれぞれから複数の信号のそれぞれを出力させる出力制御部と、複数の信号を合成した合成信号に基づいて、複数のドライバのそれぞれから出力された複数の信号のスキューを算出する算出部と、スキューに応じて、複数のドライバのそれぞれから出力される信号の出力タイミングを調整する調整部と、を備える試験装置を提供する。

(もっと読む)

測定装置、及び測定方法

【課題】DUTのジッタ伝達関数、ビット誤り率、及びジッタ耐力を効率よく算出する。

【解決手段】DUTに入力される入力信号に応じて、DUTが出力する出力信号に基づいて、出力信号の出力タイミングジッタを示す出力タイミングジッタ系列を算出するタイミングジッタ推定部と、出力タイミングジッタ系列に基づいて、DUTにおけるジッタ伝達関数を算出するジッタ伝達関数推定部とを備え、ジッタ伝達関数推定部は、出力信号に基づいて、出力信号の瞬時位相雑音を算出する瞬時位相雑音推定部と、瞬時位相雑音を、所定のタイミングでリサンプリングした出力タイミングジッタ系列を生成するリサンプリング部とを有する測定装置を提供する。

(もっと読む)

半導体集積回路および電子機器

【課題】内部信号を逐次信号に変換して出力するLSIにおいて、LSI外部信号と同期をとって観測することを可能にすること。

【解決手段】内部信号線群から1以上の内部信号線を選択する内部信号選択部1004と、内部信号線群から所定の方法により基準信号線を選択する基準信号選択部1005と、内部信号と基準信号をサンプリングするクロックを選択する基準クロック選択部1006と、出力クロックを選択する出力クロック選択部1008と、内部信号と基準信号とを基準クロックによりサンプリングするサンプリング部1007と、サンプリングした各信号値を前記出力クロックの各サイクルで逐次出力する逐次信号出力部1009とを備え、外部基準信号と内部基準信号の位相差を比較することで、逐次変換処理による遅延時間を考慮することが可能となるので、内部信号と外部信号の同期をとる事ができる。

(もっと読む)

信号品質測定装置、半導体集積回路、データ保持回路、信号品質測定方法およびプログラム

【課題】高速インタフェースの受信部における信号品質を高い精度で評価する。

【解決手段】シフトレジスタ群101は、m段のレジスタを直列に接続したシフトレジスタのデータ入力端子を互いに接続したn個のシフトレジスタから構成される。多相クロック生成回路300は、1周期の位相がn相に分割されたクロック信号を生成してシフトレジスタ毎に互いに異なる位相のクロック信号を供給する。データ入力端子611は、テスタ700から測定対象データを入力する。測定制御回路630は、多相クロック生成回路300から供給されたクロック信号に従ってシフトレジスタ群101に保持された測定対象データを取得し、シフトレジスタ群101を構成するn個のシフトレジスタの各段における測定対象データのトグル位置を検出し、この検出された各段におけるトグル位置に基づいてデータ位相品質を測定する。

(もっと読む)

半導体集積回路

【課題】ランダムパターンを用いてスキャンチェーン上の故障を検出すること。

【解決手段】半導体集積回路1は、論理回路10、パターン生成回路30、段数調整回路40、及び比較回路60を備えている。論理回路10は、N本のスキャンチェーン(11,12)を有する。パターン生成回路30は、N本のスキャンチェーン(11,12)のそれぞれの入力端子(P1,P2)にランダムパターンRPATを入力する。段数調整回路40は、N個の出力端子(Y1,Y2)を有し、また、N本のスキャンチェーン(11,12)のそれぞれの出力端子(Q1,Q2)とN個の出力端子(Y1,Y2)のそれぞれとの間に追加フリップフロップを挿入する。比較回路60は、N個の出力端子(Y1,Y2)のそれぞれから出力されるパターン(COUT1,COUT2)同士の比較を行う。段数調整回路40は、追加フリップフロップの段数を0以上に、且つ、可変に設定する。

(もっと読む)

スキャンテスト回路

【課題】複数の回路に分割して動的故障テストを実施する場合に、分割回路間の組み合わせ回路に対するテストが抜け落ち、動的故障の検出率が下がる。

【解決手段】半導体装置に内蔵される論理回路が分割された複数の分割回路を有する半導体装置のスキャンテスト回路であって、クロック制御回路と、少なくとも2以上の分割回路の各々に備えられた第1、第2のスキャンパスとを有し、第1のスキャンパスは分割回路の各々が有するスキャンFFのうち他方の前記分割回路と信号の送受を行うスキャンFFからなる周辺スキャンFFにより構成され、第2のスキャンパスは分割回路の各々が有するスキャンFFのうち前記周辺スキャンFFを除いたスキャンFFからなる内部スキャンFFにより構成され、クロック制御回路は分割回路の各々の周辺スキャンFFおよび内部スキャンFFに対応するクロック信号の伝播と遮断を制御する

(もっと読む)

半導体集積回路装置およびその試験方法

【課題】モード切替え時にロックアップタイムを不要として試験の高速化を図る。

【解決手段】PLLユニット1を搭載し、該PLLユニットの出力クロックを試験用クロックに使用してスキャンシフトモードおよびキャプチャモードにより試験を行う半導体集積回路装置であって、前記PLLユニット1は、外部からの入力クロックCLKを第1の分周数Kで分周して前記スキャンシフトモードに使用するための第1のクロックCLK1を生成する第1の分周器11と、前記入力クロックCLKを第2の分周数Mで分周して第2のクロックCLK2を生成する第2の分周器12と、該第2のクロックを受け取って前記キャプチャモードに使用するための第3のクロックCLK3を生成するPLL14と、を備えるように構成する。

(もっと読む)

半導体装置

【課題】パッケージ内に高速メモリインターフェースを有するSIP構成の半導体装置において、動作特性に不良が生ずる原因となる個々の遅延時間要因の評価が可能な半導体装置を提供する。

【解決手段】システムLSIチップ(100a)内にデータ信号(Sdw、Sdr)およびストローブ信号(Ssw、Ssr)の送信経路を変更するスイッチ(113〜116)と、各経路を転送される信号の遅延時間を調整する遅延調整回路(110〜112)が設けられている。スイッチ(113〜116)を切り換えて異なる4つの経路についてそれぞれ評価試験を行い、データの読み出しや書き込みが正常に行われるACタイミング範囲を明確にする。それぞれの経路について得られたACタイミング範囲から遅延時間の最適値を求める。この遅延時間の最適値を含む4元の連立方程式を解くことにより、遅延時間要因(106〜109)の遅延時間量が算出できる。

(もっと読む)

プリント基板の不良解析システム

【課題】簡易な試験装置を用いた場合においても、アナログ入出力機能およびデジタル入出力機能を有するプリント基板の不良解析精度を向上できるようにする。

【解決手段】不良プリント基板2のAI端子6をAI/Oケーブル14を介して良品プリント基板3のAO端子9に接続し、不良プリント基板2のAO端子7をAI/Oケーブル15を介して良品プリント基板3のAI端子8に接続し、不良プリント基板2のDI端子10をDI/Oケーブル17を介して良品プリント基板3のDO端子13に接続し、不良プリント基板2のDO端子11をDI/Oケーブル16を介して良品プリント基板3のDI端子12に接続し、故障解析制御部1は、不良プリント基板2および良品プリント基板3に伝送データを送出し、その伝送データに対する不良プリント基板2および良品プリント基板3からの応答に基づいて、不良プリント基板2の故障解析を行う。

(もっと読む)

半導体集積回路および半導体集積回路の電源電圧降下量測定方法

【課題】レイアウト工程における負担を軽減するとともに、IR−DROPの観測およびIR−DROP量の算出ができる半導体集積回路を提供する。

【解決手段】半導体集積回路1において、電源VCC1が供給される機能ブロック部2と、機能ブロック部2とは独立した電源VCC2が供給されるとともに互いに異なるクロック信号が入力されるフリップフロップFF1、FF2から構成される測定部3と、フリップフロップFF1の出力とフリップフロップFF2の入力の間に接続され、機能ブロック部2のIR−DROPを測定したい位置に配置されたバッファbufとを有する。そして、バッファbufの遅延値を、機能ブロック部2が動作状態時と非動作状態時に電源VCC1を変化させて測定し、動作状態時の電源VCC1の設定値と動作状態時の遅延時間に最も近い非動作状態時の遅延時間に対応する電源VCC1の設定値との差がIR−DROP量となる。

(もっと読む)

パネル表示装置、およびパネル異常検知方法

【課題】表示不良が発生した場合、パネル側において不良原因があることを検知できるパネル表示装置を実現する。

【解決手段】コントローラ部10から表示パネル20のゲートドライバ22およびソースドライバ23に入力される垂直駆動信号および水平駆動信号と、ゲートドライバ22およびソースドライバ23に含まれるシフトレジスタの最終段から出力される垂直出力信号および水平出力信号とのタイミング比較を、検知用信号発生回路12およびチェック回路13にて行なう。比較されたこれら信号の同期が取れていない場合には、表示パネルの異常を検知する。

(もっと読む)

半導体試験装置及びその調整方法

【課題】スキュー調整に要する時間を短縮することができる半導体試験装置及びその調整方法を提供する。

【解決手段】半導体試験装置1は、ドライバピンブロック11、調整用判定部12、及び可変遅延量データ発生部14等を備える。ドライバピンブロック11は、ドライバ信号発生回路11aから出力されるドライバ信号A1を所定の時間範囲内における所定時間だけ遅延させる可変遅延回路11bと、可変遅延回路11bを介したドライバ信号から試験信号を生成する駆動回路11cとを備える。調整用判定部12は、ドライバピンブロック11から出力される試験信号を受信して所定の基準タイミングでパス/フェイルを判定する。可変遅延量データ発生部14は、調整用判定部12の判定結果に基づいて、可変遅延回路11bの遅延時間を二分探索により決定する。

(もっと読む)

半導体装置

【課題】ストレス試験が実際に実行されたかどうかを、外部から判定する技術を提供する。

【解決手段】ストレス試験回路(11)と、ストレス試験判定回路(12)とを具備する半導体装置(1)を構成する。ここにおいて、ストレス試験回路(11)は、ストレス試験を実行するための制御信号(TM1〜TM3)を試験対象(2)とストレス試験判定回路(12)とに出力する。そして、ストレス試験判定回路(12)は、制御信号(TM1〜TM3)に基づいて、ストレス試験が実行されたか否かを示す判定結果を出力する。

(もっと読む)

半導体集積回路及び半導体集積回路の試験方法

【課題】歩留まりを向上させることが可能な半導体集積回路を提供する。

【解決手段】テスト回路14は、予め決定されたヒューズ回路18の切断位置情報を入力して、ヒューズ切断前の試験工程において、内部状態を生成する内部状態生成部(タイミング制御回路13や電源回路15)に切断位置情報を設定し、内部状態生成部は、切断位置情報をもとに内部状態(内部タイミングや内部電位)を自己生成させることにより、ヒューズ切断前の内部状態と、ヒューズ切断後の内部状態とが等しくなり、ヒューズ切断前後の内部状態の差異に起因した歩留まり悪化が防止される。

(もっと読む)

スキュー調整回路

【課題】リセット動作時に大きな雑音を発生する可変遅延回路を用いたスキュー調整回路において、他の可変遅延回路のリセット動作時の雑音干渉による遅延時間の変動を防ぎ、高集積、低消費電力、高分解能、高精度なスキュー調整回路を実現すること。

【解決手段】リセット動作時に大きな雑音を発生する可変遅延回路を用いたスキュー調整回路において、全ての可変遅延回路の遅延発生動作が終了してから全ての可変遅延回路のリセット動作を行うことを特徴とするもの。

(もっと読む)

回路動作検証装置、回路動作検証方法、半導体集積回路の製造方法、制御プログラム、およびコンピュータ読み取り可能な可読記憶媒体

【課題】配線の自己発熱による温度上昇を考慮した抵抗計算を行い、回路動作の遅延変動を正確に検証することができる回路動作検証装置を提供する。

【解決手段】半導体集積回路の回路動作を検証する回路動作検証装置100において、あらかじめ熱解析シミュレーションにより得られた熱分布情報から、該半導体集積回路における温度分布を示す温度分布テーブルを作成する温度分布テーブル作成部112と、ネットリスト情報から該半導体集積回路における配線の各部分(配線抵抗素子)の抵抗値をその位置とともに抽出する配線抵抗抽出部121と、上記温度分布テーブルを用いて、該各配線抵抗素子の抵抗値からその温度に依存した温度依存抵抗値を計算する温度依存配線抵抗計算部131とを備え、該各配線抵抗素子の温度依存抵抗値を用いて上記回路動作の遅延変動を検証するようにした。

(もっと読む)

161 - 180 / 393

[ Back to top ]