Fターム[2G132AD07]の内容

Fターム[2G132AD07]の下位に属するFターム

リングオシレータを用いるもの (13)

Fターム[2G132AD07]に分類される特許

1 - 20 / 393

半導体特性測定装置

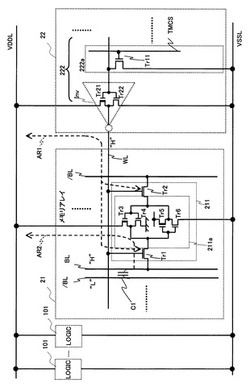

半導体集積回路,および,半導体集積回路の試験方法

【課題】チップ面積,製造コストが増大することなく,試験時における電源電圧降下を抑制する半導体集積回路を提供する。

【解決手段】半導体集積回路は,複数のワード線WLと,複数のワード線と交差する複数のビット線対BL,/BLと,複数のワード線と複数のビット線対との交差部に設けられた複数のメモリセル211とを有するメモリと,電源供給線VDDLからの電源電圧を電源として所定の論理演算を行うLOGIC101と,論理回論の試験制御を行う試験制御回路と,電源供給線VDDLに接続され,電源供給線VDDLからの電源電圧を複数のワード線WLに供給するドライバ部222と,試験制御回路の試験制御実行時に,電源電圧を複数のワード線WLに供給して複数のメモリセル211に電源電圧を供給するチャージ回路222aとを有する。

(もっと読む)

ICテスタ用信号遅延測定プログラムおよびその測定方法

【課題】 TDR測定によって、DUTボードの配線長に依存した信号遅延時間を正確に求めることが可能なICテスタ用信号遅延測定プログラムを提供する。

【解決手段】 本発明にかかるICテスタ用信号遅延測定プログラム106の構成は、コンピュータを、テストヘッド110側からステップ波形148を印加してその入射波と反射波との第1到達時間差Td1、第2到達時間差Td2を測定するTDR測定手段、第1スルーレートS2、第2スルーレートS2を演算するスルーレート演算手段、第1スルーレートS2と第2スルーレートS2とを用いて第2到達時間差Td2を補正し、第1到達時間差Td1を差し引くことで信号遅延時間を演算する信号遅延演算手段、として機能させることを特徴とする。

(もっと読む)

半導体装置

【課題】複数箇所のタイミング違反検出を、小規模な回路構成で実現する。

【解決手段】選択信号に基づいて、複数の信号からいずれか1つを選択する第1のセレクタと、上記選択信号に基づいて、ラッチされた複数の信号からいずれか1つを選択する第2のセレクタと、クロック信号CLKを所定時間遅延する遅延回路と、遅延回路により遅延したクロック信号に同期して、第1のセレクタの出力をラッチするタイミング違反検出用フリップフロップ回路と、タイミング違反検出用フリップフロップ回路の出力と第2のセレクタの出力とを比較する比較回路とを、備える。複数の信号に対し、個別に回路を設けることなく、1つのタイミング違反検出回路で構成することができる。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

半導体設計方法及び半導体設計装置

【課題】フリップフロップ追加による利益と、スキャンFFの段数増加による不利益と、を考慮に入れ、スキャンテスト回路の設計を行う半導体設計方法が、望まれる。

【解決手段】複数のスキャンFFから構成されるスキャンテスト回路の設計方法は、複数のスキャンFF間の遅延値を抽出することで、スキャンテスト回路の動作レート候補値を複数算出する第1の工程と、中継用フリップフロップの追加を仮定し、複数の動作レート候補値をそれぞれ使用して、スキャンテストの実施に必要な時間をスキャンシフト時間として算出し、スキャンシフト時間に基づき、中継用フリップフロップを追加することの効果が最も高い動作レート候補値を、中継用フリップフロップの追加後のスキャンテスト回路に適用する動作レートとして選択する第2の工程と、動作レートを満たすように、複数のスキャンFF間に中継用フリップフロップを追加する第3の工程と、を含んでいる。

(もっと読む)

集積回路および集積回路の制御方法

【課題】タイミングエラーの種類を判別することができる集積回路を提供する。

【解決手段】エラー測定部は、同期動作回路に入力されているデータ信号が第1の期間内に変化した場合には同期動作回路における第1のタイミングエラーを検出する。また、エラー測定部は、第1の期間の前または後に所定の長さのエラー警告期間を加えた第2の期間内に前記データ信号が変化した場合には同期動作回路における第2のタイミングエラーを検出する。エラー補償制御部は、第1および第2のタイミングエラーがともに検出された場合には第1および第2のタイミングエラーの検出結果の履歴に基づいてタイミングの前後のいずれにおいて前記データ信号が変化したかを判断する。

(もっと読む)

電子機器の保守装置、方法、及びプログラム

【課題】電子機器の通常動作を妨げることなく、CPUの経時劣化を保障し、電子機器の性能を維持することができるようにする。

【解決手段】保守装置1は、CPU11に内蔵されるセンサ回路12からCPU11の劣化に応じて変化する劣化情報をCPU11の通常動作時に取得する劣化情報取得部2と、劣化情報に基づいてCPU11の劣化の進行度を示す劣化レベルを判定する劣化レベル判定部3と、劣化レベルの増大に伴いCPU11に印加される電源電圧を増加させるように電源13を制御する電源制御部4とを備える。

(もっと読む)

遅延スキャンテスト方法、半導体装置及び半導体装置の設計方法

【課題】従来のスキャンテスト方法では、電源電圧変動を抑制しながら動作クロックの周波数の高い半導体装置をテストできない問題があった。

【解決手段】本発明のスキャンテスト方法は、クロック信号SCLKをスキャンフリップフロップ21〜2nに入力して第1のテストパターンをスキャンフリップフロップ21〜2nに設定し、クロック信号SCLKよりも周波数の高いクロック信号RCLKをスキャンフリップフロップ21〜2nに入力すると共に、スキャンフリップフロップ21〜2nをクロック信号RCLKによらず保持する値を維持するホールドモードに制御し、ホールドモードを解除すると共にスキャンフリップフロップ21〜2nをテスト対象回路の出力に応じて保持する値を更新するテスト結果取得モードに制御し、テスト結果取得モードにおいてクロック信号RCLKを2パルス用いてスキャンフリップフロップ21〜2nに保持されている値を更新する。

(もっと読む)

半導体装置の検査方法、検査プログラム及び半導体装置の検査装置

【課題】短時間で半導体装置の検査を行うことができる半導体装置の検査方法、検査プログラム及び半導体装置の検査装置を提供すること。

【解決手段】本発明は、記憶部2から半導体装置SD1の特性データDAT1を読み込む。次いで、ストローブ演算式212にNMOSトランジスタの閾値Vt1を代入することにより、半導体装置SD1に対するストローブ値STB1する。次いで、半導体装置SD1にテスト入力信号Dinを出力する。そして、ストローブ値STB1で指定されるタイミングで、半導体装置SD1から出力されるテスト出力信号Doutのパターンが期待値パターンEPと一致するかを判定する。

(もっと読む)

半導体試験装置における電気長測定方法

【課題】ウェハを対象とした半導体試験装置において、簡易にプローブ先端を接地状態として電気長測定を行なえるようにする。

【解決手段】試験対象のウェハと接触するプローブを複数備えた半導体試験装置における、プローブを一端とする信号経路の電気長測定方法であって、電気伝導性領域を有するキャリブレーションウェハの電気伝導性領域を全プローブに接触させ、信号経路の他端から測定信号を入力し、電気伝導性領域との接触部で反射した信号波形を他端側で測定することにより電気長を算出する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】精度の高いディレイテストを行うことが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路1は、クロック信号CLKに同期して動作する複数のレジスタを有する内部回路11と、クロック信号CLKに同期して動作し第1ノードから第2ノードまでの信号伝搬時間を測定する遅延測定回路12と、遅延測定モードの場合に、遅延測定回路12に対してのみクロック信号CLKを供給し、電圧検出モードの場合に、内部回路11及び遅延測定回路12に対してクロック信号CLKを供給するクロック供給回路13と、を備える。

(もっと読む)

解析プログラム,解析装置および解析方法

【課題】スピードパス解析の解析精度を向上させる技術を提供する。

【解決手段】第1の解析部15は,パス遅延情報記憶部120から,テスト対象回路に対するディレイテストの結果から得られるパス遅延の実測値を取得する。第1の解析部15は,予測値記憶部130から,テスト対象回路に対するタイミング解析により得られるパス遅延の予測値を取得する。第1の解析部15は,特徴値記憶部140から,遅延に影響する要因ごとの特徴値を取得する。第1の解析部15は,取得したパス遅延の実測値と,パス遅延の予測値と,要因ごとの特徴値とを用いて,要因ごとの特徴値からパス遅延の実測値と予測値とのずれを算出するずれ算出モデルを求める。このとき,第1の解析部15は,パス遅延の実測値が得られない活性化パスについて,パス遅延の実測値の代わりにディレイテストで測定した最大周波数に対応する遅延の値を用いて,解析を行う。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

半導体装置の不良解析方法、チップ状半導体装置の不良解析方法及び半導体装置の動的不良解析装置

【課題】半導体装置の動的解析を短時間で行う技術を提供する。

【解決手段】SDL/LADA解析に用いるスポット光12の径を変更可能なようにする。大径のスポット光による検査対象の半導体装置の照射中、テスタは該当する照射範囲の電気的動作の検証を行う。この照射中、不良箇所を見つけた場合には、小径のスポット光に切り替えて、検査対象の半導体装置に照射し、テスタによるより小範囲の電気的動作の検証を行う。これを反復することで、不良箇所の特定を行う。

(もっと読む)

スキャンフリップフロップ回路、スキャンテスト回路及びその制御方法

【課題】ホールドフリーの小規模なテスト回路であり、且つ実動作周波数でのテスト可能なスキャンフリップフロップを提供する。

【解決手段】PosタイプF/F100は、クロックの立ち上りエッジ同期し、データ又はスキャンテストデータが選択的に入力されるマスタラッチ(Lowレベルラッチ)110と、マスタラッチ110からのデータが入力されるスレーブラッチ(Hiレベルラッチ)111とを有する。そして、スキャンシフト時には、マスタラッチ110は、スキャンシフトデータ入力SINをスキャンシフトクロックSCLK1のLow期間で取り込むと共にスレーブラッチ111へ出力する。スレーブラッチ111はSCLK1とはエッジ位置が異なるスキャンシフトクロックSCLK2のHi期間でマスターラッチ110の出力を取り込むと共にQに出力する。

(もっと読む)

半導体装置及び半導体装置の制御方法

【課題】tRP期間の性能限界試験を実行可能な半導体装置及びその制御方法を提供する。

【解決手段】コマンドデコーダ16は、デバイスのアクティブ動作を認識し保持する第1の取り込み部、第1の取り込み部が出力する第1の出力信号を後段の回路(制御回路18)に出力する第1の出力部、デバイスのインアクティブ動作を認識し保持する第2の取り込み部、第2の取り込み部が出力する第2の出力信号を後段の回路に出力する第2の出力部を含む。第1及び第2の取り込み部は、同期信号(クロック信号CLK)の第1の遷移エッジに対応してCommandを取り込み且つ保持し第1の出力部は、第1の遷移エッジに対応して第1の出力信号(inACT)を出力する。第2の出力部は、テストモード信号が第2の論理であるテストモード動作時に、第1の遷移エッジと逆の遷移エッジである同期信号の第2の遷移エッジに対応して第2の出力信号(inPRE)を出力する。

(もっと読む)

ICチップ、半導体部品、検査用プローブ、ハンディマルチテスター、及び通信装置

【課題】TDR検査を安価な構成で実現できるICチップを得ること。

【解決手段】ICチップは、TDR(Time Domain Reflectometry)検査のためのICチップであって、クロック信号を生成するクロック生成部と、前記クロック信号をトリガとしてパルスを発生して検査対象へ出力するパルス発生部と、前記クロック信号を逓倍して逓倍クロック信号を生成する逓倍部と、前記逓倍クロック信号に同期して、前記検査対象からの反射信号をA/D変換して反射データとしてサンプリングするA/Dコンバータと、前記サンプリングされた反射データを記憶するメモリと、外部から読み出しコマンドを受け、前記読み出しコマンドに応じて前記メモリに記憶された反射データを外部に出力する通信制御部とを備えている。

(もっと読む)

半導体集積回路及び半導体集積回路のテスト方法

【課題】内部に備えられた順序回路の動作検証にかかる時間を短縮できる半導体集積回路を提供すること

【解決手段】半導体集積回路1は、入力信号3が論理回路4を通過した信号である通過信号が供給されるD型F/F10を備える。遅延量測定回路6は、論理回路4により生じる入力信号3の遅延量を、D型F/F10の動作検証前に測定する。遅延制御回路5は、D型F/F10の動作検証の際に、入力信号3を遅延量測定回路6が測定した遅延量だけ遅延させた遅延信号を生成する。比較回路11は、D型F/F10の動作検証の際に、遅延制御回路5が生成した遅延信号をD型F/F10の入力とした場合のD型F/F10からの出力と、期待値と、を比較してD型F/F10の動作検証を行う。

(もっと読む)

半導体試験装置

【課題】複数のドライバのタイミングを校正するときに、高い精度のタイミング校正を行うことを目的とする。

【解決手段】本発明の半導体試験装置は、DUT1に信号を出力するドライバ10およびドライバ10に接続されるコンパレータ11とドライバ10のタイミングを校正するために設けた基準コンパレータ6との間の校正経路Lに信号を反射する複数の半導体スイッチ15が設けられる半導体試験装置2であって、コンパレータ11がドライバ10から出力されて基準コンパレータ6で反射した校正信号を検出するときに、半導体スイッチ15で多重反射した反射信号が校正信号の検出に干渉しないように、校正経路Lを基準コンパレータ6が分割した各分割経路L1〜L3の電気長Tpd1〜Tpd3を設定している。

(もっと読む)

1 - 20 / 393

[ Back to top ]