Fターム[2G132AD07]の内容

Fターム[2G132AD07]の下位に属するFターム

リングオシレータを用いるもの (13)

Fターム[2G132AD07]に分類される特許

21 - 40 / 393

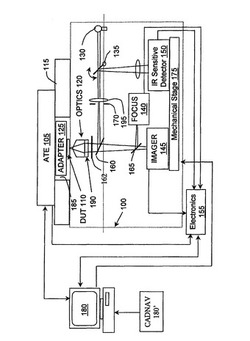

時間分解非侵入性判断システム

【課題】トランジスタの切り替え(論理遷移)に直接関係する回路タイミング情報を、トランジスタ・レベルで測定するシステムを提供する。

【解決手段】集積回路デバイスからの電気信号のプローブレス・非侵入性検出用システムである。システムは、照明源130、集光光学部材120、結像光学系、及びフォトン・センサ145を含む。ナビゲーション・モードでは、光源130を作動させ、結像光学系を用いてチップ上のターゲット領域を確認するとともに集光光学部材を適切に位置付ける。いったん集光光学部材が適切に位置付けられたら、光源の動作を停止し、チップから放出されるフォトンをフォトン・センサを用いて検出する。

(もっと読む)

半導体試験装置および半導体試験装置のタイミング校正方法

【課題】複数のドライバのタイミングを校正するときに、高い精度のタイミング校正を行うことを目的とする。

【解決手段】本発明の半導体試験装置は、DUT1に信号を出力する複数のドライバ10を備える半導体試験装置2であって、ドライバ10のタイミングを校正するための基準コンパレータ6にドライバ10からの信号を入力したときの波形が変化する間の第1の時間T1とドライバ10の出力端での信号の波形が変化する間の第2の時間T2とに基づいてドライバ10のタイミングを校正する校正値を補正する補正部25を備えている。これにより、伝送損失による波形なまりの影響を除去でき、校正値を補正して、ドライバのタイミング校正を高い精度で行うことができる。

(もっと読む)

故障解析プログラム,故障解析装置および故障解析方法

【課題】適切な故障候補の組合せを選択できるようにして、故障要因を高い精度で推定する。

【解決手段】生成部11で生成された故障候補組合せのうち、コスト算出部13で得られるコストを最小にする故障候補組合せが選択され、その故障候補組合せに応じた関数(一以上の故障要因と各故障要素の誤差または故障率との相関関係を与える関数)が出力され、この関数に基づき、故障の要因が推定される。

(もっと読む)

指標算出プログラム及び方法並びに設計支援装置

【課題】半導体装置の故障を減らすために実施すべき設計変更等に対する指標を与える。

【解決手段】本方法は、半導体装置上に実装された回路のグループ毎に当該グループにおいて発生した実故障数と故障要因となる各特徴についての特徴量とを格納する第1データ格納部に格納されているデータを用いて、互いに独立な特徴を抽出するステップと、実故障数の総和を半導体装置の数で除することによって得られる故障発生確率を、抽出された特徴の各々の特徴量と対応する係数との積の和を含む関係で表す故障発生確率モデル式を、第1データ格納部に格納されているデータを用いて回帰計算を実施することで生成するステップと、生成された故障発生確率モデル式から、半導体装置の設計変更のための指標値を算出し、第2データ格納部に格納する指標算出ステップとを含む。

(もっと読む)

半導体集積回路、スキャンテスト回路設計方法

【課題】スキャンテスト時間を短縮する半導体集積回路のスキャンテスト回路、スキャンテスト回路設計方法を提供する。

【解決手段】スキャンフリップフロップを示すセル間を接続するシフトパスを生成するステップと、信号伝達の制約条件を満たすようにリピータセルをシフトパスに挿入するステップと、スキャンフリップフロップを示すセル及びリピータセルの間のセル間遅延時間を求めるステップと、リピータセルをフリップフロップを示すセルに置換してシフトパスを分割したときのシフトパスの遅延時間を示すシフトパス遅延時間を算出するステップと、シフトパスを分割したときの、スキャンチェーンにテストデータをシフトさせて供給するスキャンシフト時間を算出するステップと、スキャンシフト時間が最短になるシフトパスの分割位置を求めるステップと、シフトパスの分割位置のリピータセルをフリップフロップを示すセルに置換した回路データを生成するステップとを具備する。

(もっと読む)

光信号出力装置、電気信号出力装置、および試験装置

【課題】光信号に効率的で簡単な構成でジッタを印加する。

【解決手段】ジッタを有する光パルスパターン信号を出力する光信号出力装置であって、周波数制御信号に応じた光周波数の光信号を出力する光源部と、光源部が出力した光信号を、指定されたパルスパターンに応じて変調する光変調部と、光変調部を通過した光信号を光周波数に応じて遅延させて、光信号にジッタを印加する光ジッタ発生部と、を備える光信号出力装置を提供する。

(もっと読む)

活性化パス抽出プログラム,活性化パス抽出装置および活性化パス抽出方法

【課題】実チップの遅延試験の際に信号が伝播した活性化パスを高速に抽出する。

【解決手段】遅延試験の際のテストパターンと実チップのネットリストとに基づき遅延試験のシミュレーションを行なうことにより遅延試験の際に信号値が変化した信号値変化ピンを特定するシミュレーション部11と、このシミュレーション部11によって特定された信号値変化ピンと実チップのネットリストとに基づき信号値変化ピンを辿ることにより活性化パスのトレースを行なうパストレース部12とがそなえられる。

(もっと読む)

遅延時間測定装置および遅延時間測定方法

【課題】フリップフロップ間のパスの数が増えると、遅延時間を測定するために必要なフリップフロップ数が大きく増加する。

【解決手段】遅延時間測定装置は、第1のクロックと第2のクロックとを出力するクロック生成部と、第1のクロックのエッジに同期して第1の信号を出力する第1のフリップフロップと、第1の信号を入力とし、第2のクロックのエッジに同期して第2の信号を出力する第2のフリップフロップと、第2の信号を入力とし、第1のクロックのエッジに同期して第3の信号を出力する第3のフリップフロップと、第1のクロックの第1のエッジが生成された時から第2のクロックの第1のエッジが発生されるまでの第1の設定時間と、記第2のクロックの第2のエッジが生成された時から第1のクロックの第2のエッジが生成されるまでの第2の設定時間とを制御する制御部と、を有する。

(もっと読む)

半導体試験装置

【課題】DUT周辺の測定条件にも配慮して、自動で所定の立ち上がり時間(または立ち下がり時間)を確保できる半導体試験装置を実現することにある。

【解決手段】 2以上の電圧発生部が被試験デバイスに電圧信号を出力し、これら電圧信号の出力タイミングを調整する半導体試験装置において、所定の時点から、前記電圧発生部が出力した電圧信号により所定の電圧レベルに達したと検出された時点までの時間を測定する立ち上がり時間測定部と、前記立ち上がり時間測定部が測定した測定時間が予め定められた基準時間よりも長い場合には、当該電圧発生部による出力以降に出力が予定されている他の電圧発生部による電圧信号の出力タイミングを予め定められたタイミングよりも遅らせるコントローラと、を具備することを特徴とする半導体試験装置。

(もっと読む)

TDC装置とTDCのキャリブレーション方法

【課題】遅延素子の遅延時間のばらつきに対してTDCの変換特性を一定とし線形性を実現可能なTDCの提供。

【解決手段】第1の信号DATAを順次遅延させる複数段の遅延素子111〜11Nを有するディレイライン10と、第2の信号CLKに応答して複数段の遅延素子の出力をサンプルする複数のフリップフロップ121〜12Nと、相隣るフリップフロップの出力結果が切り替わるエッジ位置を、第1の信号の第2の信号に対する位相差として検出するエッジ検出器13と、を備え、エッジ位置の検出結果に基づき、バイアス制御用の制御コードICNTを生成するキャリブレーション制御回路15と、制御コードに対応する複数段の遅延素子に対して供給するバイアス発生回路14を備え、第1の信号の周波数範囲に対応した段数の遅延素子に、第1の信号のエッジが位置するように遅延素子111〜11Nの遅延時間の校正を行う。

(もっと読む)

タイミング検証装置、及びタイミング検証方法

【課題】アドレスのセットアップ(Setup)違反とホールド(Hold)違反が同じクロックのイベントに対して発生した場合に、アドレスのタイミング違反が発生しても、仮想イベントを発生させることなく、対象の違反アドレスを正しく判定する。

【解決手段】イベントドリブン方式を用いた論理シミュレーションに適用される半導体装置内蔵ランダムアクセスメモリのタイミング検証装置において、クロック信号にイベントが発生した場合、当該ランダムアクセスメモリのアドレス違反処理用レジスタに現状のアドレス情報を格納する。また、アドレスのタイミング違反を確認する。また、タイミング違反を確認した結果に基づき、タイミング違反時にアドレス違反処理用レジスタの値を不定値にする。また、タイミング違反レジスタの値に基づき、違反アドレスをチェックする。

(もっと読む)

スキャンテスト回路、テスト回路生成方法およびテストパタン生成方法

【課題】異なるクロックドメインに属する回路間でデータの授受がある回路において、半導体集積回路のスキャンパスを用いてクロストークの影響を考慮した遅延試験を行うことができる。

【解決手段】第1回路群は、第1のクロックドメインに属する複数のスキャンフリップフロップ(F12、F14)を備え、信号の伝達遅延を測定する第1データパス(102)を含む。第2回路群は、第2のクロックドメインに属する複数のスキャンフリップフロップ(F11、F13、F15)を備え、第1データパス(102)に対してクロストークにより影響を与える第2データパス(101)を含む。第3データパスは、第1回路群・第2回路群間でデータを授受する。クロック切り換え回路(M10)は、制御信号に応答して、第2回路群に供給される第2クロック信号(CK2)を、第1回路群に供給される第1クロック信号(CK1)に替えて第2回路群に供給する。

(もっと読む)

テストパターン生成器、テストパターン生成器の制御方法、および、故障検出装置

【課題】記憶素子を備える回路の遅延故障を確実に検出する。

【解決手段】現在値選択保持部440は、所定の規則に従って順方向または逆方向へ遷移する値である遷移値の中のいずれかの時点の遷移値を選択して現在値として保持する。順演算部430は、現在値から順方向へ遷移した時点の遷移値を規則に基づいて演算する。逆演算部420は、現在値から逆方向へ遷移した時点の遷移値を規則に基づいて演算する。演算制御部410は、現在値選択保持部440に保持された現在値を順演算部430により演算された遷移値によって更新するとともに第1のテストパターンとして現在値選択保持部440に出力させた後、現在値選択保持部440に保持された現在値を逆演算部420により演算された遷移値によって更新するとともに第2のテストパターンとして現在値選択保持部440に出力させる。

(もっと読む)

故障診断装置、故障診断方法、及び故障診断プログラム

【課題】実測とシミュレーション結果に不一致が生じた場合に、不一致を生じている経路数だけでなく、不一致の時間的な大小を評価する。

【解決手段】本発明では、回路の後方追跡により抽出した故障候補から、候補の出力側に存在するスキャン回路(SFF)までの故障伝搬経路を、デジタル信号が伝搬する際に費やす遅延時間を求め、実測のテスト結果が不合格である経路の遅延が、合格である経路よりも大きい故障候補を、真の故障であると判定し、その大小関係に逆転(不一致)が生じた場合は、その時間的な逆転が統計的に小さい故障候補を、真の故障であると判定する。遅延が大きい経路は、それが小さい経路に比べて回路動作における時間的なマージンが小さく、遅延故障が発生した場合にテスト結果が不合格になりやすい。そのため、実測のテスト結果の合格/不合格と遅延時間の大小が上記に従う故障候補は、真の故障である可能性が高い。

(もっと読む)

オンチップジッタデータ取得回路、ジッタ測定装置、及びその方法

【課題】本発明は、高周波プローブを要さずにジッタ測定が可能なオンチップジッタデータ取得回路を提供することを目的とする。

【解決手段】本発明に係るオンチップジッタデータ取得回路1は、クロック信号を、遅延量選択信号で選択可能な複数の遅延量のいずれか1つの遅延量で遅延する可変遅延部10と、クロック信号の位相と、可変遅延部で遅延されたクロック信号の位相とを比較して、位相比較信号を生成する位相比較信号生成部20と、位相比較信号を所定の期間に亘り取得する位相比較信号取得部30と、を有することを特徴とする。

(もっと読む)

半導体集積回路及びノイズ耐性検査方法

【課題】半導体集積回路のノイズ除去機能の特性を正確に測定することができる半導体集積回路及びノイズ耐性検査方法を提供する。

【解決手段】半導体集積回路1Aは、入力信号IN中のノイズ成分の振幅を減衰させてノイズ除去信号OUTを出力する入力バッファ11と、ノイズ除去信号OUTの論理レベルが変化したときに、この論理レベルの変化に応じて論理信号をラッチする論理回路12,13とを備える。

(もっと読む)

プローブ装置

【課題】パワーデバイスの静特性及び動特性(スイッチング特性)をウエハレベルで確実に測定することができるプローブ装置を提供する。

【解決手段】本発明のプローブ装置10は、ダイオードを含むパワーデバイスが複数形成された半導体ウエハWを載置する移動可能な載置台12と、載置台12の上方に配置されたプローブカード13と、少なくとも載置台12の上面に形成された導体膜と半導体ウエハWの裏面に形成された導体層とが導通する状態で半導体ウエハWにプローブ13Aを電気的に接触させてパワーデバイスの電気的特性をウエハレベルで測定するテスタ15と、を備え、プローブカード13の外周縁部に導通ピン14を設け、パワーデバイスの電気的特性をウエハレベルで測定時に、導通ピン14を介して載置台12の導体膜電極(コレクタ電極)とテスタ15とを電気的に接続する。

(もっと読む)

タイミング解析方法、プログラム、及びシステム

【課題】IRドロップの影響を考慮して半導体集積回路のタイミング解析を行うこと。

【解決手段】タイミング解析方法は、(A)遅延変動率と電圧変動との関係を示す遅延電圧関数を算出するステップと、(B)IRドロップによる電圧変動と距離との関係を示す電圧距離関数を算出するステップと、(C)遅延電圧関数と電圧距離関数を組み合わせることによって、IRドロップによる遅延変動率と距離との関係を示す遅延距離関数を算出するステップと、(D)距離に依存するOCV係数を、遅延距離関数を用いることによって補正するステップと、(E)補正後のOCV係数を用いて、対象回路のタイミング解析を実行するステップと、を含む。

(もっと読む)

コンパレータ回路およびそれを用いた試験装置

【課題】コンパレータの遅延時間分散を低減する。

【解決手段】コンパレータ100は、入力電圧VINと基準電圧VREFを比較する。入力段10は、差動増幅器を含む。遅延回路20は、入力段10の出力信号S1を調節可能に遅延させる。遅延補償回路30は、入力段10におけるオーバードライブ電圧VODに応じて、遅延回路20の遅延量を制御する。遅延補償回路30は、差動増幅器の出力電圧をオーバードライブ電圧VODを示す信号として利用し、遅延回路20の遅延量τを制御する。

(もっと読む)

半導体試験装置およびリレーのオフ容量異常検出方法

【課題】半導体試験装置に設けられるリレーのオフ容量に異常を生じているか否かを検出することを目的とする。

【解決手段】本発明の半導体試験装置は、DUT2の試験を行うためのドライバ回路10、コンパレータ回路11を設けた試験部1を備える半導体試験装置であって、試験部1に設けられる複数のリレーのうち検査対象のリレーをオフにして電圧または電流を出力してリレーからの電圧を検出し、検出した電圧の時間的な変化に基づいて、リレーのオフ容量に異常を生じているか否かを検出する異常検出部36を備えている。これにより、ドライバ回路10やコンパレータ回路11の動作タイミングを校正する前に、リレーのオフ容量に異常を生じているか否かの検出を行うことができるようになる。

(もっと読む)

21 - 40 / 393

[ Back to top ]