Fターム[2G132AK13]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | 試験動作制御のためのCPU、論理演算回路 (455)

Fターム[2G132AK13]の下位に属するFターム

スキャン用 (150)

Fターム[2G132AK13]に分類される特許

1 - 20 / 305

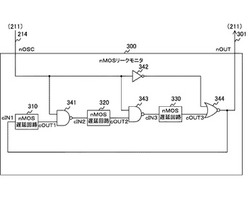

発振回路およびテスト回路

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

電池監視装置

【課題】信頼性の向上を図ることができる電池監視装置の提供。

【解決手段】電池監視装置は、直列接続された複数の電池セル(BC1〜BC4)の各セル電圧値を測定する電圧測定部を有する集積回路IC1と、複数の電池セルの正負両極と集積回路とを接続する複数の電圧計測ラインL1〜L5と、測定された各セル電圧値に基づいて電池セルの状態を監視する制御回路30と、を備え、集積回路は、互いに異なる擬似電圧を生成する擬似電圧生成部402〜405を有し、電圧測定部は、計測対象となる電池セルの正負両極に接続された一対の電圧計測ラインを選択する選択回路HVMUX1,HVMUX2と、選択回路により選択された一対の電圧計測ラインからの電圧を検出する検出回路262,122Aと、を有し、制御回路は、擬似電圧を選択回路に入力し、検出回路により検出された電圧値に基づいて選択回路による選択状態を診断する。

(もっと読む)

最適化されたJTAGインターフェイス

【課題】

集積回路内のJTAGタップドメインにアクセスするのに最適化されたJTAGインターフェイスが使用される。限定はしないが、シリアル通信関連集積回路テスト、エミュレーション、デバッグ、および/またはトレース操作等の多様なシリアル通信操作に対してインターフェイスを使用することができる。

【解決手段】

TDI入力端子、TCK入力端子、TMS入力端子、およびTDO出力端子を有し、TDO出力端子は集積回路の外部アクセス可能なデータ入出力ピンに接続されているIEEE 1149.1タップドメインと、集積回路の外部アクセス可能なデータ入出力ピンに接続されたシリアル入力端子、TDI入力端子に接続された第1のパラレル出力端子、およびTMS入力端子に接続された第2のパラレル出力端子を有するシリアル入力パラレル出力回路とを含む、集積回路。

(もっと読む)

半導体装置、電子機器、および半導体装置の検査方法

【課題】電源端子または接地端子の接続不良を容易に検出する。

【解決手段】半導体装置の電源端子TCと第1の入出力端子T1との間には、電源端子TCがカソード側となり、第1の入出力端子T1がアノード側となるようにダイオードD11が設けられる。判定部10Aは、電源電圧Vccに等しいハイレベルの信号が第1の入出力端子T1に入力されたとき、電源端子TCの電圧が第1の入出力端子T1の電圧よりも低いか否かを判定する。

(もっと読む)

半導体回路

【課題】簡単な回路構成で故障検出のための試験を行うことができる半導体回路を提供する。

【解決手段】シフトレジスタを有しシリアル−パラレル変換を行う変換回路24の故障検出を行うための試験時に、シフトレジスタの初段のフリップフロップFF1AのD入力に、その/Q出力BS2Aを供給することで、クロック信号CLKのサイクル毎に0、1を交互に繰り返す信号を試験パターンとして生成し、この試験パターンを用いて変換回路24の試験を行うようにして、回路規模の大きな試験回路を搭載しなくとも、簡単な回路構成で故障検出のための試験を行えるようにする。

(もっと読む)

モニタリング装置及びモニタリングシステム

【課題】LSI等の不具合発生時の原因追求を容易化する。

【解決手段】LSI内又はLSIの近傍にモニタリング装置100を配置し、モニタリング装置100内で、周波数カウンタ20が、一定時間でのリングオシレータ10の発振周波数を計測し、計測した発振周波数を示す発振周波数情報を生成し、時刻カウンタ30が、周波数カウンタ20により発振周波数が計測された時刻を示す時刻情報を生成し、出力制御部80が、発振周波数情報と時刻情報とを対応付けて記憶装置90に出力し、記憶装置90が、発振周波数情報と時刻情報をログとして記憶する。これにより、LSIが起動してから不具合発生までの間の発振周波数の推移を観測することで遅延の相対的な変化を確認することができ、LSIの個体差を気にする必要がなく、不具合発生時の原因追求を容易化できる。

(もっと読む)

半導体集積回路およびその検査方法

【課題】半導体集積回路に内蔵されたアナログ/デジタル変換器をテストするためのテスト信号発生器として半導体集積回路に内蔵されたデジタル/アナログ変換器を使用する際に、デジタル/アナログ変換器が正常なデジタル/アナログ変換動作を実行可能であるか否か動作検証することを可能とすること。

【解決手段】半導体集積回路1は、アナログ/デジタル変換器(ADC)5とデジタル/アナログ変換器(DAC)6とを内蔵する。DAC6は、ADC5をテストするためのテスト信号生成器として使用可能とされる。半導体集積回路1は、DAC6の出力端子とADC5の入力端子の間に入力端子と出力端子とが接続されたバッファ増幅器7を更に具備する。バッファ増幅器7の出力端子とADC5の入力端子のいずれか一方は、半導体集積回路1の外部端子(T1、T2)として外部に導出される。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

半導体装置

【課題】テスト信号毎の専用配線を不要とし、配線領域を削減できるテスト回路を備えた半導体装置を提供する。

【解決手段】外部から供給されるテスト情報をデコーディングし、複数の信号を生成するDFTデコーダ202と、互いに従属接続した複数のDFTレジスタDFTr0〜DFTrnと、複数のDFTレジスタにそれぞれ対応する複数の制御回路(制御回路CKT0〜CKTn)と、複数のレジスタのうちの第1のレジスタ(DFTレジスタDFTr0)に複数の信号(シフトデータTSCANDATA)を供給するセレクタ(セレクタ113)と、セレクタのセレクティング回数を規定するカウンタ(9bitカウンタ112)と、複数の制御回路の数に対応するクロック周期の回数を、複数のレジスタ及びカウンタに供給するシフトクロック生成回路(シフトCK制御回路111)と、を備える。

(もっと読む)

トレースデータ取得装置、トレースデータ取得装置のトレースデータ取得方法およびデバッグシステム

【課題】LSIの実行を停止させることなく、被試験プログラムを分割せずに、必要なトレースデータを効率良く取得できるようにすることを目的とする。

【解決手段】トレースデータ入出力状況分析部140は、トレースデータバッファ120の空き容量102に基づいて、トレースデータ101の種類を優先度の高い順に選択する。トレースデータ取捨選択部110は、LSIのトレース信号発生源からトレースデータ101を入力し、入力したトレースデータ101が選択種類のトレースデータ101であるか否かを判定する。トレースデータ101が選択種類のトレースデータ101である場合、トレースデータ取捨選択部110はトレースデータ101をトレースデータバッファ120に記憶する。トレースデータ101が選択種類のトレースデータ101でない場合、トレースデータ取捨選択部110はトレースデータ101を破棄する。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、各前記回路ブロック毎に電源電圧を供給し、前記電源電圧を電圧調整回路により切り替える電圧供給回路を有し、前記電圧調整回路を切り替える電圧制御信号を記憶する電源電圧制御メモリを有する電圧設定回路を有し、前記半導体装置の回路の複数箇所に回路の電圧を検出する電圧検出スイッチを有し、前記電圧検出スイッチを指定することで電圧を検出する回路の位置を切り替え、且つ、前記電源電圧制御メモリにアドレスを指定して値を書き込む制御を行う回路スイッチ制御回路を有する半導体装置を用いる。

(もっと読む)

検査装置及び方法

【課題】検査対象回路が正常に機能しているか否かを電源電圧の立ち上がり期間に拘らず高精度に検査することができる半導体集積回路、検査装置及び方法を提供する。

【解決手段】検査装置10を、POR回路102の出力端子102Cから第1入力端子14Aにリセット信号が入力されたときに出力端子14Cからリセット信号と同レベルのリセット実行信号の出力を開始し、制御装置18の出力端子から第2入力端子14Bにトリガ信号が入力されたときにリセット実行信号の出力を終了して出力端子14Cからリセット解除信号と同レベルの解除実行信号の出力を開始するリセット制御回路14と、リセット制御回路14から出力された信号が予め定められたレベルであるか否かを判定することによりPOR回路102が正常に機能しているか否かを判定するテスタ124と、を含んで構成した。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、前記回路ブロックがそれぞれ正常に動作し得る最小限度の電圧を供給する複数の電圧供給回路を備え、各前記回路ブロックへの最小限度の電圧を供給する制御内容を記憶する電源電圧制御メモリを有し、前記電源電圧制御メモリの記憶する制御内容に従って前記電圧供給回路が各前記回路ブロックに供給する電圧を切り替える電源切り替え手段を備えた半導体装置を用いる。

(もっと読む)

半導体装置

【課題】RFチップ本来の回路特性を抽出できるようにする。

【解決手段】半導体試験装置より出力された変調信号を増幅して出力する低雑音増幅器より出力される信号が供給されるとともに、低雑音増幅器により増幅された後に直交復調処理された変調信号を半導体試験装置用基板の伝送路に対して出力する増幅器に入力される信号が供給される試験回路をRFチップに備える。試験回路は、半導体試験装置より出力する変調信号の波形データが予め記憶され、低雑音増幅器より出力される信号及び増幅器に入力される信号をスペクトラム解析した解析結果と記憶されている変調信号の波形データとの比較によりRFチップにおけるチップ内ノイズ及びRFチップ本来の回路特性を抽出する。

(もっと読む)

半導体集積回路装置およびテストモード設定方法

【課題】簡易な回路で、よりセキュリティ性を向上させる。

【解決手段】半導体集積回路装置(100)は、複数の機能ブロック(125−127)と、取り込み部(131)と、検出部(132)と、判定部(150)とを具備し、動作パターンが所定の規則に従って変化したときにテストモードに移行する。複数の機能ブロック(125−127)は、制御装置(200)からの指示に応答して動作する。取り込み部(131)は、複数の機能ブロック(125−127)のそれぞれの動作状態を示す信号を取り込む。検出部(132)は、複数の機能ブロック(125−127)のうちの少なくとも1つの機能ブロックの動作状態の変化を検出する。判定部(150)は、取り込まれた動作状態を示す信号によって示される動作パターンが所定の規則に従って変化するか否かを判定する。

(もっと読む)

半導体装置、半導体装置の試験方法、及びデータ処理システム。

【課題】内部信号線の寄生抵抗値を測定できるようにする。

【解決手段】インターフェースチップとコアチップとを電気的に接続する1又は複数の内部信号線101を備え、インターフェースチップは、内部配線に電流を出力する第1の回路111を有し、コアチップは、第1の内部信号線101に電流を出力する第2の回路121を有し、インターフェースチップは、第1の回路111が出力する電流が流れる上記内部配線に接続される第1の入力端子151aと、第1の内部信号線101のインターフェースチップ内の端部101aに接続される第2の入力端子151bとを有し、第1の入力端子151aの電圧と第2の入力端子151bの電圧との電位差に応じた電圧を出力する判定回路150を有する。

(もっと読む)

オンチップジッタデータ取得回路、ジッタ測定装置、及びその方法

【課題】本発明は、高周波プローブを要さずにジッタ測定が可能なオンチップジッタデータ取得回路を提供することを目的とする。

【解決手段】本発明に係るオンチップジッタデータ取得回路1は、クロック信号を、遅延量選択信号で選択可能な複数の遅延量のいずれか1つの遅延量で遅延する可変遅延部10と、クロック信号の位相と、可変遅延部で遅延されたクロック信号の位相とを比較して、位相比較信号を生成する位相比較信号生成部20と、位相比較信号を所定の期間に亘り取得する位相比較信号取得部30と、を有することを特徴とする。

(もっと読む)

半導体集積回路及びノイズ耐性検査方法

【課題】半導体集積回路のノイズ除去機能の特性を正確に測定することができる半導体集積回路及びノイズ耐性検査方法を提供する。

【解決手段】半導体集積回路1Aは、入力信号IN中のノイズ成分の振幅を減衰させてノイズ除去信号OUTを出力する入力バッファ11と、ノイズ除去信号OUTの論理レベルが変化したときに、この論理レベルの変化に応じて論理信号をラッチする論理回路12,13とを備える。

(もっと読む)

試験方法

【課題】簡易なテスタにより被試験デバイスの試験を行うことができる試験方法を提供することを課題とする。

【解決手段】各々が記憶回路を有する複数の被試験デバイス(211〜214)の試験方法であって、試験パタンが前記複数の被試験デバイスの記憶回路に分割されて記憶されており、前記複数の被試験デバイスの記憶回路から試験パタン(DT0〜DT3)を読み出して、前記読み出した複数の被試験デバイスの試験パタンを併合して前記複数の被試験デバイスに同じ試験パタン(PTN0〜PTN3)を供給する試験パタン読み出しステップと、前記供給された同じ試験パタンを用いて前記複数の被試験デバイスを同時に試験する試験ステップとを有する試験方法が提供される。

(もっと読む)

半導体集積回路の試験システムおよびその試験方法

【課題】半導体集積回路の不良選別を効果的に行う。

【解決手段】互いに非同期のクロックで動作する複数の回路ブロックを有し、複数の回路ブロックの一の回路ブロックによってセルフテストを実行する半導体集積回路の試験システムであって、複数の回路ブロックに対応するクロック信号を生成し半導体集積回路に供給するクロック発生装置と、半導体集積回路からの要求に応じてセルフテストの実行を代行するプロセッサを有する。これにより、各モジュールが非同期のクロックで動作する半導体集積回路の動作テストを行うことができる。

(もっと読む)

1 - 20 / 305

[ Back to top ]