Fターム[2G132AK14]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | 試験動作制御のためのCPU、論理演算回路 (455) | スキャン用 (150)

Fターム[2G132AK14]に分類される特許

1 - 20 / 150

半導体装置

【課題】 多様な方式でスキャンテスト経路を形成することができる半導体装置を提供する。

【解決手段】第1チップおよび第2チップを電気的に連結する第1貫通ビアおよび第2貫通ビアと、前記第1チップに配置され、テストデータを受信するとともに前記第1貫通ビアと接続される第1回路部と、前記第1チップに配置され、前記第2貫通ビアおよび前記第1回路部と接続される第2回路部と、前記第2チップに配置され、前記第1貫通ビアと接続される第3回路部と、を含み、前記第1回路部は第1制御信号に応答して前記第1貫通ビアおよび前記第2回路部のうちいずれか一つに前記第1回路の出力信号を出力する。

(もっと読む)

スキャンチェーン検査装置及び検査方法

【課題】 スキャンチェーンの検査を好適に行うことが可能なスキャンチェーン検査装置及び検査方法を提供する。

【解決手段】 半導体装置10のスキャンチェーンに検査信号を供給する検査信号供給部18と、スキャンチェーンの各レジスタでの検査信号の信号レベルの時間変化を測定するレジスタ測定部20と、測定部20による測定結果に基づいて各レジスタにレジスタ番号を付与するレジスタ番号解析部51を有する検査解析装置50とによってスキャンチェーン検査装置1Aを構成する。供給部18は、信号長nが異なるm種類の検査信号列を供給する。解析部51は、信号長nの検査信号列を用いた測定結果からスキャンチェーンの複数のレジスタをn個のグループに分けるグループ分けをm種類の検査信号列のそれぞれについて行い、その結果に基づいて各レジスタにレジスタ番号を付与する。

(もっと読む)

半導体回路及びテスト方法

【課題】スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する半導体回路及びテスト方法を提供する。

【解決手段】複数の被試験回路と、試験回路に対応して設けられた複数の第1のラッチ回路と、第2のラッチ回路と、パターンアドレスに対応して入力信号が規定されたテストパターンのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する総合判定回路と、複数の第1のラッチ回路と第2のラッチ回路とを、第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

(もっと読む)

半導体装置

【課題】スキャンテストを可能にしながら内部データの漏洩及び改竄を防止する半導体装置を提供する。

【解決手段】複数のフリップフロップを有するユーザー回路と、テストモード時に、前記複数のフリップフロップを接続してスキャンチェーンを構成する接続経路とを有し、前記接続経路は、前記複数のフリップフロップのうちいずれかの前記フリップフロップの非反転出力値を論理演算して出力する論理演算回路、または、前記複数のフリップフロップのうちいずれかの前記フリップフロップの反転出力値を後段のフリップフロップに出力する反転値接続経路を有する。

(もっと読む)

プリント回路基板上に取り付けられた電子回路装置の電気接続を自動的に測定する方法及び装置

【課題】プリント回路基板(PCB)上に取り付けられた電子回路装置の構成要素及び装置の回路端子又はピン間の電気接続を測定するための単純なツールが必要。

【解決手段】電子処理ユニットは、各バウンダリスキャン対応装置32,33,34,35のバウンダリスキャン特性と、ドライバ及び/又はセンサとして動作可能なバウンダリスキャン・セルを含むリストを取得する。このリストに基づいて、回路端子に接続されたバウンダリスキャン・セルがドライバ、センサとし作動し、バウンダリスキャン・レジスタにラッチする。ドライバ・データとセンサ・データを含むバウンダリスキャン・レジスタからのデータが、記憶装置45に記憶される。記憶されたデータは、プリント回路基板31における回路端子37,38間と40,41間の電気接続を判定するために分析され、分析の結果が提示される。

(もっと読む)

テストパタン生成システム、テストパタン生成方法、およびテストパタン生成プログラム

【課題】ATPGにおけるテストパタンの生成時間を短縮するための技術を提供する。

【解決手段】EDAツール(11〜16)と、EDAツール(11〜16)が参照する情報を保持するファイル格納部(9)とを具備するテストパタン生成システムを構成する。そのファイル格納部(9)は、テストパタンの生成の対象となる回路の接続情報を示すネットリスト(21)と、ネットリストに示される回路のうち、故障検出の対象となる故障検出対象領域の起点となる端子を示す始終点リスト(22)とを備えるものとする。そのロジックコーン抽出部(11)は、始終点リスト(22)に示される起点を頂点とするロジックコーン(34)(35)を特定する。また、故障リスト生成部(12)は、組み合わせ回路(32)(33)に含まれる全てのノードから、ロジックコーンに含致しないノードを除外して故障リスト(24)を生成する。

(もっと読む)

集積回路テスト用の低電力で面積効率の良いスキャンセル

【課題】電力消費および面積要件の低減がもたらされる、スキャンテスト回路を有する集積回路を提供すること。

【解決手段】集積回路は、スキャンテスト回路と、スキャンテスト回路を使用してテストを受ける追加回路とを備える。スキャンテスト回路は、複数のスキャンセルを有する少なくとも1つのスキャンチェーンを備え、スキャンチェーンは、スキャンシフト動作モードではシリアル・シフトレジスタとして動作し、機能動作モードでは追加回路の少なくとも一部分からの機能データを捕捉するように構成される。スキャンチェーンのスキャンセルの少なくとも所与の1つは、スキャンシフト動作モードではスキャンセルの機能データ出力をディスエーブルし、機能動作モードではスキャンセルのスキャン出力をディスエーブルするように構成された出力制御回路を備える。

(もっと読む)

半導体集積回路及びその制御方法

【課題】アプリケーション実行効率をよりよくすることができる半導体集積回路及びその制御方法を提供すること

【解決手段】本発明にかかる半導体集積回路は、スキャンチェーンを有するプロセッサと、プロセッサにアプリケーションを実行させるプロセッサ制御部と、プロセッサのスキャンテストを制御するスキャンテスト制御部と、を有する。そして、スキャンテスト制御部がスキャンテストを実行している際に、プロセッサ制御部からのスキャンテスト中断要求があった場合、スキャンテストを中断し、アプリケーションの実行後に、スキャンテストを再開させるものである。

(もっと読む)

マルチステージ・テスト応答コンパクタ

【課題】より高い圧縮比を提供し得る圧縮スキームを提供する。

【解決手段】いわゆる「Xプレス」テスト応答コンパクタ110、152は、オーバードライブ・セクションとスキャンチェーン選択ロジックとを含む。実施形態は約1000倍の圧縮比を提供する。例示的な実施形態は、従来のスキャンベースのテストシナリオとほぼ同じカバレッジおよびほぼ同じ診断分解能を維持できる。スキャンチェーン選択スキームのいくつかの実施形態は、テスト応答で発生してコンパクタに入る未知状態を有意に減らすことができ、または完全に排除できる。また、オンチップ・コンパクタ回路の実施形態および選択回路をマスクする制御回路網を生成する方法も開示する。

(もっと読む)

半導体集積回路及び電源電圧適応制御システム

【課題】フリップフロップを備える半導体集積回路において、エラーフリップフロップを効率的に検出する。

【解決手段】半導体集積回路は、冗長フリップフロップを含む複数のフリップフロップと、セレクタ部と、エラー検出部とを備える。セレクタ部は、再構成情報に応じて選択フリップフロップを選択し、入力端子に入力されたデータが選択フリップフロップのそれぞれによって出力端子に出力されるようにデータの流れを切り替える。テストモード時、フリップフロップはスキャンチェーンを構成し、そのスキャンチェーンにはスキャンデータが入力される。そして、エラー検出部は、それぞれのフリップフロップの入出力に基づいてエラーフリップフロップを検出し、当該エラーフリップフロップが選択フリップフロップから除外されるように再構成情報を作成する。

(もっと読む)

試験アクセス・ポート・スイッチ

【課題】選択されていないTAPの電源がオンまたはオフされているかに関わらず、選択されたTAPへ情報を転送することができる電子システムを提供する。

【解決手段】電子システム10は、それぞれTAPスイッチ12に接続されたTAP20,22,24を有している。TAPスイッチ12は、例えば、命令に追加または事前追加されたコードのように、シリアル命令に含まれる選択コードに応答して、TAPのうちの選択された1つへクロック信号を提供するように構成された第1の回路40を備える。このTAPスイッチは更に、TAPスイッチによって受け取られたシリアル命令を、選択されたTAPへ渡すように構成された命令レジスタ(IR)を備える第2の回路38と、選択コードに応答して、選択されたTAPから受け取ったシリアル命令を、TAPスイッチの出力へと転送するように構成された第3の回路42とを備える。

(もっと読む)

MUX−Dスキャン機能を有するパルスダイナミックロジックゲート

スキャン可能なパルスダイナミックロジックゲートは、評価パルスのアサーションに応答してダイナミック入力を評価する評価ネットワークを備えている。評価パルスは、クロック信号より幅が短くなるようにクロック信号から発生される。通常の動作モード中に、評価パルスがアサートされたとき、評価ネットワークは、ダイナミック入力の状態に基づいてダイナミックノードをディスチャージする。それにより生じるダイナミックノードの状態は、出力記憶素子内にラッチされる。評価パルスがデアサートされると、ダイナミックノードがプリチャージされる。スキャン動作モード中に、ダイナミックノードは、プリチャージされたままとなる。スキャンデータは、スキャン関連コントロール信号のコントロールのもとで出力記憶素子へ転送される。 (もっと読む)

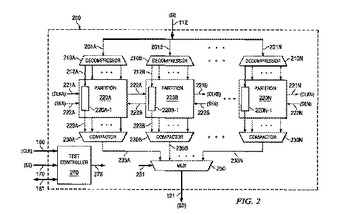

パーティションを設けたスキャン・チェーンを備えた集積回路のスキャンテストにおける向上した制御

パーティションを設けたスキャン・チェーンを備えた集積回路(IC)に実装されたテスト・コントローラが、スキャンテストを実行する際に向上した制御を提供する。一つの側面に従って、テスト・コントローラは、独立しているべき、ICの異なるスキャン・チェーンに対するスキャンテストのスキャンイン、スキャンアウト、及びキャプチャ位相を選択的に制御できる。外部テスターとインタフェースするためにテスト・コントローラに必要なピンの数は、そのテスト・コントローラがサポートし得るパーティションの数より少ない。別の側面に従って、ICは、遷移故障(又はLOS)テストをサポートするため各パーティションに対応するレジスタを含む。別の側面に従って、パーティションを設けたスキャン・チェーンを備えたICが、シリアル−パラレル及びパラレル−シリアル変換器を含み、それにより、スキャンテストをサポートするために必要とされる外部ピンを最小限にする。  (もっと読む)

(もっと読む)

積層ダイ構造の試験のための装置および方法

集積回路装置は、積層ダイ(102)とベースダイ(101)とを含み、ベースダイは、集積回路装置の試験のためのスキャンチェーンを実現するために、ベースダイのテストロジック(305,104)に直接的に結合するプローブパッド(306,111−116)を有する。ベースダイは、さらに、ベースダイの背面に配置されるコンタクト(107)と、コンタクトに結合されるとともにベースダイのプログラマブルロジック(550,314,105)に結合されるダイ貫通ビア(310,121−128)を含む。ベースダイは、また、テスト入力に結合されるように構成された第1のプローブパッド(111)と、テスト出力に結合するように構成された第2のプローブパッド(112)と、制御信号に結合するように構成された第3のプローブパッド(113)とを含む。ベースダイのテストロジック(305)は、スキャンチェーンを実現するために、積層ダイのさらなるテストロジック(405)に結合するように構成されて。スキャンチェーンを実現するために、プログラマブルロジック(550,314,105)の構成を必要としないように、プローブパッド(306,111−116)は直接的にテストロジック(305,104)に結合される。  (もっと読む)

(もっと読む)

半導体装置のテスト回路、半導体装置及びその製造方法

【課題】半導体装置のバーンインテストまたはリークテストの際に、F/Fだけではストレスを印加できない組み合わせ回路のノードにストレスを与えるとともに、半導体装置の回路オーバーヘッドを抑えることができるテスト回路、半導体装置及びその製造方法を提供すること。

【解決手段】本発明によるテスト回路は、組み合わせ回路31、32と結合して半導体装置内に配置される。ノードN1とノードN2の間にはトランスファーゲートスイッチTGが接続される。ノードN2と電源VDDの間には第一のトランジスタT1が接続される。ノードN2とグランドGNDの間には第二のトランジスタT2が接続される。トランスファーゲートスイッチTG、第一のトランジスタT1、第二のトランジスタT2は、半導体装置の外部から供給される少なくとも1つの制御信号に応じて動作する。

(もっと読む)

半導体集積回路及びスキャンテスト方法

【課題】故障検出率を向上することができる半導体集積回路及びスキャンテスト方法を提供すること

【解決手段】本発明にかかる半導体集積回路は、入力されたトリガ信号に応じて、出力値を出力する第1の回路と、入力されたトリガ信号に応じて、出力値を出力する第2の回路とを備える。また、通常動作モードでは、第1の回路から出力された出力値に基づいた値をトリガ信号として第2の回路に供給し、かつ第1の回路の入力値とは独立した値を入力値として第2の回路に供給し、スキャンテストモードでは、第1の回路に入力されたトリガ信号と共通の信号をトリガ信号として第2の回路に供給し、かつ第1の回路の出力値に基づいた値を入力値として第2の回路に供給する制御回路とを備える。

(もっと読む)

テスト回路

【課題】従来のテスト回路では、被テスト回路のテスト範囲を自由に設定することができない問題があった。

【解決手段】本発明のテスト回路の一態様は、IEEE1149に規定される標準仕様に準拠した複数のTAPコントローラを有するテスト回路であって、制御コード及びテスト制御信号を受けて、被テスト回路に対するテストの実行と、シフトモード信号SFTの出力と、を行うマスタTAPコントローラ10と、制御コード及びテスト制御信号を受けて、被テスト回路に対するテストを実行する第1のスレーブTAPコントローラ20と、第1のスレーブTAPコントローラ20対応して設けられ、第1のスレーブTAPコントローラ20に入力する制御コードを外部から入力するか、マスタTAPコントローラ10を介して入力するかを、シフトモード信号SFTに基づき切り替える第1の端子制御回路30と、を有するものである。

(もっと読む)

EDAツール、半導体装置およびスキャンチェイン構成方法

【課題】スキャンチェイン上の隣接するFFの異なる論理値を持つ頻度が大きくなることでテスト時のIRドロップを回避する技術を提供する。

【解決手段】期待値導出処理モジュールM1が各FFの論理値を確率伝播の計算または論理シミュレーションの実施によって導出する。グルーピングモジュールM2は求めた論理値を参照して検査対象のFFをいくつかのグループにグルーピングする。スキャンチェイン構成モジュールM3は論理値「1」を取り込む頻度が背反する2つのグループをペアにして、一方を論理反転させて1つのスキャンチェインを構成する。

(もっと読む)

半導体集積回路、半導体集積回路の内部状態退避回復方法

【課題】内部状態の退避および回復時の時間を短縮し、消費電力を削減する。

【解決手段】スキャンチェーンは、スキャンパステストのときに、第1回路に含まれる複数の第1フリップフロップと、第2回路に含まれる複数の第2フリップフロップとを鎖状に接続してシフトレジスタとして動作する。バックアップ制御回路は、第1フリップフロップに保持される内部状態を示すデータを、第2フリップフロップをバイパスしたスキャンチェーンを介してメモリ回路に格納する退避動作と、メモリ回路から内部状態を示すデータを読み出して第2フリップフロップをバイパスしたスキャンチェーンを介して第1フリップフロップに再設定する回復動作とを制御する。入力選択回路は、スキャンパステストのテストデータと、メモリ回路から読み出した内部状態を示すデータとのうちの一方を選択してスキャンチェーンに供給する。

(もっと読む)

半導体集積回路およびその半導体集積回路のテスト方法

【課題】スキャンテストにおけるキャプチャ期間のサイクル数を削減する。

【解決手段】スキャンパスフリップフロップを有する論理回路(65)と、スキャンパステストを実行するテスト回路(70)とを具備する半導体集積回路を構成する。テスト回路(70)は、クロック制御回路(80)と、スキャンイネーブル制御信号生成回路(13)とを備える。スキャンイネーブル制御信号生成回路(13)は、クロック制御回路(80)(80a)から出力されるクロックオン情報信号を受けて、他のクロック制御回路(80)(80b)にスキャンイネーブル制御信号を供給する。他のクロック制御回路(80)(80b)は、スキャンイネーブル制御信号に基づいて、スキャンイネーブル信号の値を特定する。このとき、スキャンパスフリップフロップは、スキャンイネーブル信号の値に従って、データ出力端子(64)から固定値を出力する。

(もっと読む)

1 - 20 / 150

[ Back to top ]