Fターム[2G132AK29]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | 自己診断(BIST等) (359)

Fターム[2G132AK29]に分類される特許

1 - 20 / 359

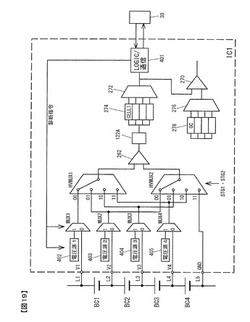

電池監視装置

【課題】信頼性の向上を図ることができる電池監視装置の提供。

【解決手段】電池監視装置は、直列接続された複数の電池セル(BC1〜BC4)の各セル電圧値を測定する電圧測定部を有する集積回路IC1と、複数の電池セルの正負両極と集積回路とを接続する複数の電圧計測ラインL1〜L5と、測定された各セル電圧値に基づいて電池セルの状態を監視する制御回路30と、を備え、集積回路は、互いに異なる擬似電圧を生成する擬似電圧生成部402〜405を有し、電圧測定部は、計測対象となる電池セルの正負両極に接続された一対の電圧計測ラインを選択する選択回路HVMUX1,HVMUX2と、選択回路により選択された一対の電圧計測ラインからの電圧を検出する検出回路262,122Aと、を有し、制御回路は、擬似電圧を選択回路に入力し、検出回路により検出された電圧値に基づいて選択回路による選択状態を診断する。

(もっと読む)

半導体装置

【課題】半導体チップの面積を縮小することが可能な半導体装置を提供する。

【解決手段】半導体チップを有する半導体装置では、半導体チップに設けられた内部回路のテストを行うテスト回路と、そのテストが行われている間は内部回路を駆動せず、テストが行われた後に内部回路を駆動する駆動回路とを有し、内部回路に接続された信号線が、テスト回路と駆動回路とで共用される。

(もっと読む)

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

不揮発性半導体記憶装置及びその試験方法

【課題】電源投入により自走的にメモリセルアレイの動作テストを実行する。

【解決手段】一つの実施形態によれば、不揮発性半導体記憶装置は、不揮発性半導体記憶装置は、ロムヒューズブロックを有するメモリセルアレイ、自走テスト部を有するコントローラ、及びコマンドレジスタを有する。不揮発性半導体記憶装置は、電源投入によりメモリセルアレイの自走テストを実行する。

(もっと読む)

集積回路,集積回路の試験装置および集積回路の試験方法

【課題】集積回路上の冗長メモリの試験に際し、冗長メモリにおける不良発生位置を取得する。

【解決手段】スペアのメモリセルをもつ冗長メモリ30と、冗長メモリ30に与えるテストパターンと当該テストパターンを冗長メモリ30に与えた際に冗長メモリ30から出力されるべきデータの期待値とを生成する生成部41と、生成部41によって生成された期待値と、第1生成部41によって生成されたテストパターンを冗長メモリ30に与えた際に冗長メモリ30から出力されるデータとを比較する比較部42と、比較部42の比較結果を記憶する記憶部10と、比較部42の比較結果が不一致である場合、当該比較結果を、当該比較結果を得た冗長メモリ30の位置情報に対応付けて記憶部10に書き込む一方、比較部42の比較結果が一致である場合、当該比較結果の記憶部10への書込を抑止する書込制御部50Aと、を有する。

(もっと読む)

半導体回路及びテスト方法

【課題】スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する半導体回路及びテスト方法を提供する。

【解決手段】複数の被試験回路と、試験回路に対応して設けられた複数の第1のラッチ回路と、第2のラッチ回路と、パターンアドレスに対応して入力信号が規定されたテストパターンのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する総合判定回路と、複数の第1のラッチ回路と第2のラッチ回路とを、第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

(もっと読む)

半導体集積回路検査装置,および,半導体集積回路の検査方法

【課題】テスト時間をより短縮するテストパターンを作成する半導体集積回路検査装置,および,半導体集積回路の検査方法を提供する。

【解決手段】半導体集積回路検査装置20は,テストパターンを複数の区間に分割した分割テストパターン毎に,分割テストパターンに対する論理演算を異なる周期のクロック信号に基づき半導体集積回路に実行させることにより得られた半導体集積回路31の故障判定結果に基づき,分割テストパターン毎の最適クロック周期を算出する最適周期算出部213と,テストパターンと,テストパターンに係る分割テストパターン毎の最適クロック周期を有するテストパターンファイルを生成する新テストパターンファイル生成部214を有する。

(もっと読む)

書込回路、半導体集積回路、及び書込方法

【課題】アンチヒューズ型のOTPメモリへの書き込み時間を短縮化すること。

【解決手段】書込回路は、OTPマクロに対して書き込むデータを記憶する記憶部と、前記書き込むデータの書き込みを前記OTPマクロに実行させる第一の信号を印加し、前記OTPマクロが記憶しているデータの読み出しを前記OTPマクロに実行させる第二の信号を印加する制御部と、前記第二の信号に応じて前記OTPマクロから読み出されたデータと、前記記憶部が記憶するデータとを比較し、比較結果を出力する比較部とを有し、前記制御部は、前記比較結果が一致を示す場合、前記書き込むデータに関する処理を終了し、前記比較結果が不一致を示す場合、前記第一の信号及び前記第二の信号の印加を再度行う。

(もっと読む)

半導体記憶装置

【課題】メモリセルのサブスレッショルド・リーク電流の影響によって不良となるデバイスを選別検査で確実にリジェクトする。

【解決手段】行列状に配置された複数のメモリセルMEMと、メモリセルの行に対応して設けられた複数のワード線WL0〜WL4と、メモリセルの列に対応して設けられた複数のビット線対BT0、BB0及びBT1、BB1と、前記複数のワード線のうち、検査対象の注目メモリセル以外の非注目メモリセルが接続された非注目ワード線をフローティングとするスイッチMN1と、前記非注目ワード線がフローティングのときに、当該非注目ワード線を昇圧するポンピング回路POC0とを備える。

(もっと読む)

アナログデジタル変換回路、アナログデジタル変換回路の検査方法、撮像装置、撮像装置を有する撮像システム、撮像装置の検査方法

【課題】複数のメモリ間でのショート故障の有無を検査できる構成を有するADCおよびその検査方法、ADCを有する撮像装置、撮像装置を有する撮像システムを提供する。

【解決手段】複数のメモリと複数の比較器とを含んで構成される回路部を複数有し、アナログ信号をデジタル信号に変換するアナログデジタル変換回路であって、複数の回路部の一部に含まれるメモリと複数の回路部の別の一部に含まれるメモリとで異なるデジタル信号を保持するようにテスト信号を供給するテスト信号供給部と、出力比較部と、転送部を有することを特徴とするアナログデジタル変換回路である。

(もっと読む)

スイッチ装置、伝送路切替装置、および試験装置

【課題】長寿命化した圧電式アクチュエータを備えるスイッチ装置。

【解決手段】第1接点が設けられた基体と、第2接点を移動させて第1接点と接触または離間させるアクチュエータと、を備え、アクチュエータは、支持層と、支持層の上面に形成される第1圧電膜と、支持層を介して第1圧電膜に対向して、支持層の第1圧電膜が形成される面とは反対側の面に設けられ、駆動電圧に応じて伸縮してアクチュエータのそり量を変化させる第2圧電膜と、第1圧電膜および第2圧電膜のそれぞれの上面と下面とに、それぞれの駆動電圧を印加する電極層と、第2圧電膜と第2圧電膜の支持層側とは反対側の電極層との間に形成された導電性酸化物を含む第2導電性酸化物膜と、を有するスイッチ装置を提供する。

(もっと読む)

集積回路および集積回路の接続不良検出方法

【課題】製品組立後の経年劣化による接続不良を含め、簡単な構成で被実装基板との接続不良を検出する。

【解決手段】集積回路に、同一の電位が与えられる2以上の比較電圧用パッドと、比較電圧用パッドにかかる電圧を比較して、その比較結果に基づいて被実装基板との接続不良の有無を示す信号を出力する比較判別回路とを設け、比較判別回路において、少なくとも2つの比較電圧用パッドにかかる電圧の電位差が所定の値を超えた場合に、接続不良を示す信号を出力させる。

(もっと読む)

故障箇所推定装置と方法並びにプログラム

【課題】スキャンテスト設計が施された機能ブロックと付加回路とを含む論理回路全体を故障診断を可能とし、診断処理時間を大幅に短縮可能とする装置、方法の提供。

【解決手段】論理回路内のスキャンフリップフロップで構成されるスキャンチェーンの構成情報、論理回路の設計情報を入力データ1として入力し、論理回路においてパラレル領域以外の回路部をシリアル領域として抽出することで、前記論理回路を前記パラレル領域とシリアル領域に分割する回路分割手段2と、正常回路における論理値を期待値として求める期待値計算手段3と、テストパタンに対する論理回路のテスト出力を入力データ1として入力し、テスト出力および、シリアル領域とパラレル領域の期待値を用いて、パラレル領域およびシリアル領域を故障診断し、出力部に出力する故障診断手段4とを備える。

(もっと読む)

半導体集積回路および半導体集積回路のテスト方法

【課題】小さな回路規模で複数のパラレルシリアル変換回路を確実にテストすることが可能な半導体集積回路等を提供する。

【解決手段】第1および第2のパラレルシリアル変換回路と、第1および第2のテスト用パラレルデータ列を生成するテスト用パラレルデータ列生成回路と、第1および第2のパラレルシリアル変換回路が変換した第1および第2のシリアルデータビットの一致/不一致を検出する検出回路とを備えた半導体集積回路において、テスト用のパラレルデータ列生成回路が共通のテスト用パラレルデータ列を構成するそれぞれのパラレルデータのビットを第1のビット数だけシフトして第2のテスト用パラレルデータ列を生成するパラレルビットシフト回路を含み、検出回路が第1のシリアルデータと第2のシリアルデータとの一方のビットをシフトして比較回路に入力されるタイミングをそろえるシリアルビットシフト回路とを含む。

(もっと読む)

自己診断装置、自己診断方法、及びプログラム

【課題】効率的に自己診断を行うこと。

【解決手段】自己診断装置は、複数の機能ブロックと、複数の機能ブロックに対して自己診断を夫々行う複数の自己診断手段と、各機能ブロックの動作頻度を夫々検出する動作頻度検出手段と、動作頻度検出手段により検出された各機能ブロックの動作頻度に基づいて、各自己診断手段が各機能ブロックの自己診断を行う優先順位を設定する優先順位設定手段と、所定の時間制限を行う時間制限値に基づいて、各機能ブロックの自己診断の実行が可能な実行可能回数を算出する実行可能回数算出手段と、を備える。各自己診断手段は、優先順位設定手段により設定された優先順位と、実行可能回数算出手段により算出された実行可能回数と、に基づいて、各機能ブロックの自己診断を行う。

(もっと読む)

検査システム及びそれを用いた半導体装置並びに検査方法

【課題】 回路面積の増大が少なくコスト増を抑えることが可能な検査システムの提供。

【解決手段】 検査回路3は、第1の回路1と第2の回路2の間に介在する。また、検査回路3は、信号伝達制御機能4と検査出力機能5とを含んでいる。信号伝達制御機能4は、第1の回路1と第2の回路2の間の信号伝達を制御する。また、検査出力機能5は、検査回路3を介し、第1の回路1の出力を検査用に出力する。本発明では、信号伝達制御機能4と検査出力機能5は、互いの機能を実現する回路の一部を共有している。また、第1の回路1と第2の回路2と検査回路3は、同一の基板上に設けられている。検査回路3は信号伝達制御機能4と検査出力機能5とを切り替えて使用する。

(もっと読む)

半導体試験装置及びそのテスト方法

【課題】メモリのテスト時の消費電流を抑え、メモリテスト時の周波数を高速化する。

【解決手段】制御回路103は、第1及び第2のテストパタンジェネレータ104、105によるテストがともにライトの場合、一方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータに対してテストシーケンスの実行を不許可とし、一方のテストパタンジェネレータからメモリグループ101、102の対応する一方のグループに対してライトのテストパタンを出力し、他方のグループに対するライトの実行を、一方のグループのライトのテストサイクル単位で時間的にずらし、一方のテストパタンジェネレータによる一方のグループのライトの終了後、他方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータから対応する他方のグループに対するライトのテストパタンを出力する。

(もっと読む)

完全に不定値許容性であって非常に高スキャン圧縮なスキャンテストシステム及び技術

【課題】完全に不定値許容性の非常に高スキャン圧縮なスキャンテストシステム及び技術を提供する。

【解決手段】スキャンテスト及びスキャン圧縮は、コストの低減及び高い出荷品品質を実現するうえで重要である。従来以上に複雑な設計における新しいタイプの故障には、高い圧縮が必要とされる。しかしながら、不定値(X)の密度が増加し効果的な圧縮を妨げる。スキャン圧縮の方法では、任意の密度の不定値について非常に高い圧縮及び完全な検出率が達成される。記載された技術は、テスト容易化設計(DFT)及び自動テストパターン生成(ATPG)のフローに完全に組込むことができる。産業的な設計にこれらの技術を用いた結果、他の方法と比べて一定かつ予測可能な有利な点があることが分かった。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

半導体装置のテスト方法

【課題】テストコストの低減を実現可能な半導体装置のテスト方法を提供する。

【解決手段】例えば、ループバック配線LNp1,LNn1,LNp2,LNn2を持つテスト用基板TBD上に被テストデバイスDUTを搭載し、DUTの差動送信端子TXp,TXnからの信号をループバック配線を介して差動受信端子RXp,RXnに戻すことでテストを行う。ループバック配線上には振幅制御回路ブロックVACTLBK1が設けられ、VACTLBK1は、可変利得アンプ回路AMP1等を用いてLNp1,LNn1から入力された信号の電圧振幅レベルを振幅設定信号VASETに基づくレベルに変換してLNp2,LNn2に出力する。これによって、例えば受信電圧振幅レベルのテスト仕様が異なるDUTでTBDを共通に使用すること等が可能になる。

(もっと読む)

1 - 20 / 359

[ Back to top ]