Fターム[2H092JA30]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 半導体層 (1,729) | 大きさ (545)

Fターム[2H092JA30]の下位に属するFターム

Fターム[2H092JA30]に分類される特許

1 - 20 / 43

アクティブマトリックス型表示素子およびその製造方法

【課題】少ない工程数でアクティブマトリクス表示素子を形成する。

【解決手段】実施形態にかかるアクティブマトリックス型表示素子の製造方法は、絶縁基板上にゲート電極層、第1の絶縁膜、酸化物半導体層、第2の絶縁膜、酸化物半導体層と電気的に接続したソース・ドレイン電極を順に形成する工程を含む。酸化物半導体層は、ソース・ドレイン電極が形成される領域から画素領域にわたって形成され、第2の絶縁膜を形成する前に、酸化物半導体の画素領域に相当する部分を低抵抗処理して第1の画素電極を形成する。

(もっと読む)

表示装置及び液晶表示装置

【課題】酸化物半導体を用いたトランジスタを具備する画素において、開口率の向上を図る。

【解決手段】第1のトランジスタと、第1の画素電極とを有する第1の画素を有し、第2のトランジスタと、第2の画素電極とを有する第2の画素を有し、走査線として機能することができる配線を有し、第1のトランジスタは、酸化物半導体層を有し、酸化物半導体層はゲート絶縁膜を介して、配線と重なり、酸化物半導体層は、配線より幅の広い領域を有する表示装置又は液晶表示装置である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】絶縁層に凸状部またはトレンチ(溝部)を形成し、該凸状部またはトレンチに接して半導体層のチャネル形成領域を設けることで、チャネル形成領域を基板垂直方向に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、半導体層成膜前に、半導体層が接する凸状部またはトレンチの上端コーナー部に、R加工処理を行うことで、薄膜の半導体層を被覆性良く成膜する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

アレイ基板及び液晶表示装置

【課題】製造歩留まりの高いアレイ基板及び液晶表示装置を提供する。

【解決手段】アレイ基板は、複数の補助容量電極と、複数の半導体層15と、複数のゲート電極20を含んだ複数の走査線19と、複数の補助容量線と、複数のコンタクトホールを有した層間絶縁膜と、複数のコンタクトホールを通って複数の半導体層のソース領域に電気的に接続された複数の信号線と、複数の画素電極と、を備えている。走査線19が延在した方向に互いに隣合う一方の画素電極が接続された補助容量電極と、他方の画素電極が接続された補助容量電極とは、走査線を挟んで位置している。薄膜トランジスタのチャネル面積CSは、24μm2以上である。

(もっと読む)

表示装置

【課題】画素部の薄膜トランジスタにおけるゲート・ソース間容量のばらつきを抑制することが可能な技術を提供する。

【解決手段】画素の領域毎に形成される画素電極PXと、画素電極を駆動する薄膜トランジスタとを備える表示装置において、薄膜トランジスタは、対角位置に形成される第1の角部B及び第2の角部Cと、前記第1の角部Bが形成される第1の辺と前記第2の角部Cが形成される第2の辺とを共有する第3の角部とを有し、ゲート絶縁膜を介して前記ゲート線GLに接続されるゲート電極と重畳して形成される半導体層ASと、前記ドレイン線DLからその一部が延在して形成され、前記第3の角部と重畳されるドレイン電極DTと、一端が前記第1の角部Bに重畳して形成され、他端が前記画素電極と接続される第1のソース電極ST1と、一端が前記第2の角部Cと重畳して形成され、他端が前記画素電極PXと接続される第2のソース電極ST2と、を有する。

(もっと読む)

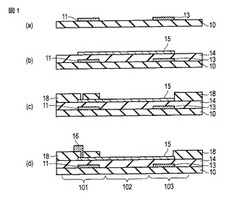

液晶表示装置及び当該液晶表示装置を具備する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上を図ることのできる液晶表示装置を提供する。

【解決手段】薄膜トランジスタ106、及び画素電極105を有する複数の画素を有し、画素は、走査線として機能する第1の配線101に電気的に接続されており、薄膜トランジスタは、第1の配線101上にゲート絶縁膜113を介して設けられた酸化物半導体層103を有し、酸化物半導体層103は、第1の配線が設けられた領域をはみ出て設けられており、画素電極105と、酸化物半導体層103とが重畳して設けられる。

(もっと読む)

半導体装置

【課題】半導体装置の表示領域と駆動回路に設けられたTFTの構造を機能に応じて適切なものとするとき、pチャネル型TFTにおいて、チャネル形成領域と、不純物領域との接合に欠陥が形成され、オフ電流が増加することを防止する。

【解決手段】表示領域に第1のnチャネル型TFTが配置され、駆動回路に第2のnチャネル型TFT及びpチャネル型TFTが配置された半導体装置であって、pチャネル型TFTはチャネル形成領域と、これに隣接した不純物領域を有し、不純物領域にはnチャネル型TFTのために添加された不純物元素を含ませない。そのために、pチャネル型TFTのチャネル長はnチャネル型TFTのチャネル長より短くなる。

(もっと読む)

表示装置

【課題】極めて簡単な構成にも拘わらず、半導体層への光照射を低減し、オフ電流の発生の抑制を図った薄膜トランジスタを具備する表示装置の提供。

【解決手段】画像表示部が形成された基板に薄膜トランジスタが形成された表示装置であって、

前記薄膜トランジスタは、

ゲート電極と、

前記ゲート電極を被って形成されたゲート絶縁膜と、

前記ゲート絶縁膜上であって前記ゲート電極に重畳して形成される半導体層と、

前記半導体層上に形成され互いに対向して配置された一対の電極と、

を備え、

前記半導体層は、平面的に観た場合、前記ゲート電極の形成領域内に配置され、前記ゲート電極側から、結晶性半導体層および非晶質半導体層の順次積層体から構成され、

前記ゲート電極は、少なくとも前記半導体層と対向する領域において、光透過率が0.3%以下となる膜厚で形成されている。

(もっと読む)

電気光学装置及び電子機器

【課題】例えば、液晶装置の画素領域における開口率を高めると共に、画素スイッチング用素子に発生する光リーク電流を低減し、プロジェクタによって表示される画像の表示品位を低下させない。

【解決手段】活性層(1a)の一部であるチャネル領域(1a)が延びる方向であるチャネル長方向が、走査線(3a)が延びるX方向に沿っている。加えて、液晶装置(1)によれば、ゲート電極(13)は、X方向に沿って、データ線(6a1)及びデータ線(6a2)の夫々から距離(W)だけ離れた位置、即ちX方向に沿ってデータ線(6a1)及び(6a2)間の中心位置(Pc)からデータ線(6a1)の側にチャネル領域(1c)のチャネル長(Lc)の長さだけずれた第1の位置(P1)と、中心位置(Pc)からデータ線(6a2)の側にチャネル長(Lc)の長さだけずれた第2の位置(P2)との間の領域(R)に設けられている。

(もっと読む)

半導体装置の製造方法、半導体装置、および電気光学装置

【課題】、ポリシリコン膜に含まれる結晶欠陥を電気的に略不活性化させた場合でも、その後の工程での処理温度が限定されることがなく、かつ、能動層とゲート絶縁層との間に良好な界面を形成することができる半導体装置の製造方法、半導体装置および電気光学装置を提供すること。

【解決手段】半導体装置10tの製造工程では、電界効果型トランジスタ30nの能動層となるシリコン膜1sを結晶化させた後、シリコン膜1sに酸素プラズマ照射OPを行う酸素プラズマ照射工程と、酸素プラズマ照射工程によりシリコン膜1sに形成された表面酸化物1rを除去する表面酸化物除去工程とを行う。その後、シリコン膜1sをパターニングする。

(もっと読む)

半導体薄膜、半導体薄膜の形成方法及びこれを用いた薄膜トランジスタと薄膜トランジスタの製造方法

【課題】本発明の目的は、半導体膜と電極との電気的なコンタクトが良好で、性能のバラツキがない半導体薄膜の製造方法、またこれを用いて、既成容量が少なく、高性能で動作が安定した薄膜トランジスタを製造することにある。

【解決手段】半導体前駆体を含有する液体材料を液滴にして基板上に塗設し、乾燥させて島状のパターンをもつ半導体前駆体薄膜を形成し、該半導体前駆体に変換処理を施して半導体を形成する半導体薄膜の形成方法において、島状のパターンを有する変換処理後の半導体薄膜が、

半導体薄膜の膜厚をチャネル方向に非接触3次元表面形状測定装置にて測定した膜厚プロファイルにおいて、半導体薄膜の中央から端部までの距離の50%のところから端部までの平均膜厚と、半導体薄膜の中央から端部までの距離の50%のところから中央までの平均膜厚とが、異なっていることを特徴とする半導体薄膜の形成方法。

(もっと読む)

表示装置およびその製造方法

【課題】低リークで特性のばらつきの少ない薄膜トランジスタを備える表示装置の提供。

【解決手段】表示部を備える基板に薄膜トランジスタが形成された表示装置であって、

前記薄膜トランジスタは、ゲート電極と、前記ゲート電極を被って形成されたゲート絶縁膜と、

前記ゲート絶縁膜の上面に前記ゲート電極を跨って形成された、少なくとも、多結晶半導体膜、非晶質半導体膜、および高濃度ドープト非晶質半導体層の順次積層体からなる半導体膜積層体と、

前記半導体膜積層体の上面に前記ゲート電極に重なる領域を間にして互いに対向して配置される第1電極と第2電極を備え、

前記第1電極と第2電極の間の前記高濃度ドープト非晶質半導体層はその下層の非晶質半導体膜が露出する程度に除去され、

前記第1電極から延在される配線の直下および前記第2電極から延在される配線の直下のそれぞれに前記半導体膜積層体が形成された構成からなる。

(もっと読む)

表示装置

【課題】光源側にゲート電極膜を有するTFTを複数個直列に設ける場合、光リーク電流の発生を抑えつつ、容量増加をも抑制することができる表示装置を提供することにある。

【解決手段】複数個あるTFTの少なくとも一部について、半導体膜とゲート電極膜が対向する面積のチャネル領域に対する相対的な面積が異なることにより、光リーク電流の発生を抑えつつ、容量増加を抑制する構造の平面ディスプレイを提供する。

(もっと読む)

薄膜トランジスタ、および薄膜トランジスタアレイ

【課題】 薄膜トランジスタの特性を良好にすると同時に、蓄積容量部に形成される金属−絶縁体−半導体構造(MIS構造)を解消しキャパシタの値を安定化させることで、フォトマスク工程数を削減しても高い性能を維持できる薄膜トランジスタ及びそれを用いた表示装置を提供する。

【解決手段】 4回以下のフォトマスク工程数で作製される薄膜トランジスタ部216と、蓄積容量部217とを有する薄膜トランジスタアレイ基板において、チャンネルの形成に寄与しない活性半導体層をシリサイド化する。

(もっと読む)

半導体装置、TFT基板、表示装置、携帯機器

【課題】同一絶縁基板上に形成された2つのトランジスタの拡散層の抵抗値を同じにすることのできる新構造のトランジスタを搭載した半導体装置を提供する。

【解決手段】第1のトランジスタ(図中左側のトランジスタ)は、第1のゲート電極304a下部に形成された第1の絶縁膜303aと、拡散層領域302a2,302a3上に形成された第2の絶縁膜303bとを備え、これら第1の絶縁膜303a及び第2の絶縁膜303bより上層に第1のゲート電極304aが配置されており、かつ、第1の絶縁膜303aが第2の絶縁膜303bよりも薄く形成され、第1のトランジスタの第2の絶縁膜303bは、第1のゲート電極304aの下面縁部から内側まで入り込んで形成され、拡散層領域302a2,302a3は、第1の絶縁膜303aの下までオーバーラップして形成された構造となっている。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】サイズの大型化を抑制しつつ必要な電流を得ることの可能な薄膜トランジスタおよびこれを用いた表示装置を提供する。

【解決手段】薄膜トランジスタ1は、基板10上にゲート電極11およびゲート絶縁膜12を介してシリコン膜13を有している。シリコン膜13のゲート電極11に対応する領域には絶縁保護膜14が形成され、絶縁保護膜14の上面両端からシリコン膜13上にかけて、非晶質シリコン膜(ソース領域)15Aおよび非晶質シリコン膜(ドレイン領域)15Bが形成され、それぞれソース電極16Aおよびドレイン電極16Bにより覆われている。シリコン膜13はチャネル領域13Cを有し、このチャネル領域13Cにおいて長さ方向に沿って結晶化領域13Bおよび非結晶領域13Aが形成されている。結晶化領域13Bの幅d1が調整されることにより、必要電流が得られる。

(もっと読む)

半導体装置の製造方法、電気光学装置の製造方法

【課題】CVD装置を用いて基板上に半導体膜を成膜する際、各結晶粒のグレインサイズが略均一となるとともに、面内において略均一な膜厚の半導体膜を形成することができることにより、信頼性の高いトランジスタを製造できる半導体装置の製造方法を提供する。

【解決手段】基板を、CVD装置内に導入して、ヒータ上に載置し、ヒータを加熱することによって基板を設定された成膜温度まで加熱するステップS1と、CVD装置内にモノシランガスを導入して、基板上に、非晶質の第1の半導体膜を第1の膜厚に成膜するステップS2と、CVD装置内にジシランガスを導入して、第1の半導体膜上に、非晶質の第2の半導体膜を第1の膜厚よりも厚い第2の膜厚に成膜して、第1の半導体膜及び第2の半導体膜により、半導体膜を設定厚さに形成するステップS3と、を具備することを特徴とする。

(もっと読む)

有機トランジスタ、有機トランジスタアレイ及び表示装置

【課題】本発明は、有機半導体層のパターンを制御すると共に、ゲート電極とソース・ドレイン電極とのオーバーラップを低減することが可能な有機トランジスタ、該有機トランジスタを複数有する有機トランジスタアレイ及び該有機トランジスタアレイを有する表示装置を提供することを目的とする。

【解決手段】有機トランジスタ10は、基板1上に、ゲート電極2及びゲート絶縁膜3が順次形成され、少なくともゲート絶縁膜3上に、ソース電極4及びドレイン電極5並びに有機半導体層6が順次形成されており、ドレイン電極5は、ゲート電極2上に形成されている第一の領域5aと、第二の領域5bと、第一の領域5aと第二の領域5bを第一の領域5aの幅よりも短い幅で連結する連結領域とを有し、有機半導体層6は、印刷法により形成されている。

(もっと読む)

半導体装置、およびその作製方法

【課題】ばらつきを抑え、かつ、製造歩留まりの高い半導体装置を作製することを課題とする。

【解決手段】

絶縁表面を有する基板上に、チャネル形成領域が非単結晶半導体層で形成される薄膜トランジスタを有し、前記非単結晶半導体層は、厚さが5nm以上50nm以下であり、一方向に略平行に延びる結晶粒界を含み、該結晶粒界の間隔は10nm以上、500nm以下であることを特徴とする、半導体装置及びその作製方法を提供する。

(もっと読む)

1 - 20 / 43

[ Back to top ]