Fターム[2H092NA21]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | 素子性能の向上 (1,705)

Fターム[2H092NA21]の下位に属するFターム

ON/OFF比の向上 (571)

寄生容量の低減 (220)

素子性能の均一化 (379)

Fターム[2H092NA21]に分類される特許

201 - 220 / 535

薄膜トランジスタ、その製造方法及び薄膜トランジスタを備える平板表示装置

【課題】活性層の界面特性が向上できる薄膜トランジスタ、その製造方法及び薄膜トランジスタを備える平板表示装置を提供する。

【解決手段】本発明の薄膜トランジスタは、基板と、前記基板上に形成されたゲート電極と、ゲート絶縁層によって前記ゲート電極と絶縁され、酸化物半導体からなる活性層と、前記活性層と連結されるソース電極及びドレイン電極と、前記活性層の上部面及び下部面のうちの少なくとも一面に形成された界面安定化層とを有し、前記界面安定化層は3.0〜8.0eVのバンドギャップを有する酸化物からなる。

(もっと読む)

表示装置

【課題】ソース電極およびドレイン電極とゲート電極との間の寄生容量の変化に起因するフリッカを抑制するとともに、薄膜トランジスタの動作速度の向上を図ることが可能な表示装置を提供する。

【解決手段】この表示装置100では、薄膜トランジスタ4のゲート電極1Aは、平面的に見てゲート線1から突出するとともに所定の方向に延びるように形成され、ソース電極8およびドレイン電極9は、平面的に見て互いに並行配置され、ゲート電極1Aおよび半導体層7が平面的に見て重なる領域上で、旋回しながら屈曲して形成されている。

(もっと読む)

半導体装置の作製方法

【課題】動作性能及び信頼性を向上させた半導体装置の作製方法を提供する。

【解決手段】単結晶シリコン基板の一部からなる単結晶シリコン薄膜を、単結晶シリコン基板を熱酸化して得られた第1の酸化シリコン膜上に有し、第1の酸化シリコン膜が、シリコン基板上に設けられた第2の酸化シリコン膜に貼り合わされたシリコン基板を用いる半導体装置の作製方法であって、単結晶シリコン薄膜から複数の島状シリコン層を形成し、複数の島状シリコン層の熱酸化工程後に、複数の島状シリコン層上にポリシリコンでなるゲート電極を形成し、ゲート電極の側面にサイドウォールを形成し、複数の島状シリコン層にソース領域及びドレイン領域を形成し、ゲート電極、ソース領域、ドレイン領域に金属膜を形成し、加熱してゲート電極、ソース領域、ドレイン領域にシリサイドを形成し、複数の島状シリコン層を覆って、層間絶縁膜を形成する半導体装置の作製方法を提供する。

(もっと読む)

薄膜トランジスタ及び該薄膜トランジスタを有する表示装置

【課題】電気的特性が良好な薄膜トランジスタを作製することを課題とする。

【解決手段】ゲート電極層と、ゲート電極層を覆って設けられた第1の絶縁層と、ゲート電極層と少なくとも一部が重畳し、離間して設けられた、ソース領域及びドレイン領域を形成する一対の不純物半導体層と、第1の絶縁層上に、ゲート電極層と少なくとも一部が重畳し、且つ一対の不純物半導体層の少なくとも一方と重畳せずしてチャネル形成領域の一部に設けられた微結晶半導体層と、第1の絶縁層と微結晶半導体層との間に接して設けられた第2の絶縁層と、第1の絶縁層上に第2の絶縁層及び微結晶半導体層を覆って設けられた非晶質半導体層と、を有し、第1の絶縁層は窒化シリコン層であり、第2の絶縁層は酸化窒化シリコン層である薄膜トランジスタとする。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】TFTに代表される半導体素子の動作特性が改善されるように、微結晶シリコン膜若しくは結晶粒を含む膜の膜質を制御する。また、微結晶シリコン膜若しくは結晶粒を含む膜の堆積過程を制御して、TFTに代表される半導体素子の特性向上を図る。また、薄膜トランジスタのオン電流を向上させ、オフ電流を低減する。

【解決手段】非晶質構造の中に複数の結晶領域を含む半導体層において、該結晶領域が生成する起点となる結晶核の生成位置と生成密度を制御することで、該半導体層の膜質を制御する。また、半導体層の結晶領域が生成する起点となる結晶核を生成した後、ドナーとなる不純物元素を半導体層に添加して、半導体層の結晶性を高めると共に、半導体層の抵抗率を低減する。

(もっと読む)

半導体装置

【課題】動作性能及び信頼性を大幅に向上することができる半導体装置を提供することを課題とする。

【解決手段】シリコン基板上に設けられた酸化シリコン膜と、単結晶シリコン基板の一部よりなりTFTの活性層となる島状シリコン層を熱酸化して得られ、酸化シリコン膜に貼り合わせ界面にて貼り合わせて設けられた酸化シリコン膜と、活性層を熱酸化して設けられた他の面の酸化シリコン膜とにより取り囲まれた活性層と、活性層上に設けられたゲート電極と、を有する半導体装置を提供する。

(もっと読む)

電子素子及びその製造方法

【課題】導体膜の分子に対する十分な配向規制力を実現した電子素子を提供する。

【解決手段】電子素子は、基板1上に配された導体膜2と、導体膜2に電流を流すための電極3,4と、導体膜2と基板1との間に配され、導体膜2に含まれる分子を所定の方向に配向する配向層5とを備えている。配向層5は、複数本の溝Mが平行に形成された主面を有する基層6と、溝Mの形成された主面を被覆する被膜7とからなる。被膜7は、主面に対して導体膜2の分子を平行に配向する水平配向能を有し、各溝Mは所定の方向(図では紙面に垂直な方向)に沿って伸びており且つ所定の方向と直交する直交方向(図では紙面に平行で且つ水平な方向)に沿って与えられたピッチで繰り返し配列されており、導体膜2の分子は、溝Mの直交方向に配向する部位を有する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】 簡便に形成可能であり、リーク電流の発生を抑制できる薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】 薄膜トランジスタ22は、ソース領域及びドレイン領域の一方である第1領域と、他方である第2領域と、を有した半導体層25と、ゲート絶縁層27と、ゲート絶縁層上に形成され、第1領域から外れて位置し、第2領域に重ねられた開口部30aを有した環状のゲート電極30と、層間絶縁膜31と、半導体層の第1領域に接続された第1電極と、半導体層の第2領域に接続された第2電極と、を備えている。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】電気的ストレスによる閾値電圧変化の小さいコプラナー構造の薄膜トランジスタ及びその製造方法を提供する。

【解決手段】基板の上に、ゲート電極と、ゲート絶縁層と、ソース電極とドレイン電極とチャネル領域とからなる酸化物半導体層と、チャネル保護層と、層間絶縁層と、を少なくとも有する薄膜トランジスタであって、前記チャネル保護層は1層以上で形成され、そのうち前記酸化物半導体層と接する層は酸素を含む絶縁体からなり、該チャネル保護層の端部の膜厚が該チャネル保護層の中央部の膜厚と比べ薄く、かつ、前記層間絶縁層は水素を含有しており、該層間絶縁層と直接接している該酸化物半導体層の領域がソース及びドレイン電極をなしていることを特徴とする。

(もっと読む)

半導体装置の製造方法および電気光学装置

【課題】非晶質シリコン層を改質して得られたポリシリコン層には突起部分が発生する。ゲート絶縁層中に突起があると、この突起部分に電界が集中し、絶縁破壊が生じる。電解還元水は、酸化シリコン層をエッチングせず、ポリシリコン層をエッチングする性質がある。そこで酸化シリコン層を除去した後、電解還元水をスラリーとして用いてCMP法を用いる技術があるが、この場合、ポリシリコン層全面がCMP法により薄層化されてしまうという課題がある。

【解決手段】自然酸化シリコン層304を残した状態で電解還元水をスラリー107として用いてCMP工程を行う。機械的効果によりポリシリコン層303の突起上にある自然酸化シリコン層304は除去され、突起領域のみ電解還元水でエッチングが進みポリシリコン層303は平坦化される。そして、平坦部は自然酸化シリコン層304により保護され、薄層化は抑制される。

(もっと読む)

半導体基板、半導体基板の製造方法、トランジスタ、並びに電気光学装置

【課題】多結晶シリコンを(111)配向を選択的に形成する場合、結晶粒界の位置はランダムに形成されるため、トランジスタのチャネル部分に結晶粒が配置された場合、結晶粒界に存在するトラップ準位の影響により、電気的特性が低下する。また、チャネル部分に発生したホットキャリアを吸収する領域がなく、キンク特性が発生するという課題がある。

【解決手段】(111)配向を含む不純物がドーピングされた第1シリコン層204上に貫通孔206を含む絶縁層205を形成した後、第2シリコン層前駆体207aを積層し、XeClエキシマレーザを用いて第1シリコン層204を種結晶として再結晶工程を行い、面方位が(111)に揃えられた第2シリコン層207を形成する。そして不純物がドーピングされた第1シリコン層204からホットキャリアを引き抜くことで、キンクの発生が抑えられ、且つ電気的特性に優れたトランジスタを提供できる。

(もっと読む)

表示装置及び電子機器

【課題】薄膜トランジスタを使用したメモリ回路において、トランジスタのバラツキによって、メモリ回路の歩留まりの低下や、応答速度の低下などの問題が発生していた。

【解決方法】本発明は、メモリセルの論理振幅と異なる電圧でワード線を駆動することによって、メモリセルの歩留まり向上、応答速度の向上を図るものである。本発明はSRAM、DRAM、マスクROMなどに適応が可能であり、本発明のメモリ回路を表示装置と一体形成することで、より多機能な表示装置を構成することが可能になる。

(もっと読む)

半導体装置の作製方法

【課題】動作性能および信頼性の高い半導体装置の作製方法の提供を課題とする。

【解決手段】単結晶シリコン薄膜を熱酸化膜からなる第1の酸化シリコン上に有し、第1の酸化シリコンを第2の酸化シリコン上に有し、第2の酸化シリコンを表面上に有する単結晶シリコン基板を用いる半導体装置の作製方法であって、単結晶シリコン薄膜から複数の島状シリコン層を形成し、複数の島状シリコン層の側面に熱酸化により第3の酸化シリコン膜を形成し、複数の島状シリコン層上にポリシリコンでなるゲート電極を形成し、ゲート電極の側面にサイドウォールを形成し、複数の島状シリコン層にソース領域及びドレイン領域を形成し、ゲート電極、ソース領域、ドレイン領域に金属膜を形成し、加熱してゲート電極、ソース領域、ドレイン領域にシリサイドを形成し、複数の島状シリコン層を覆って、層間絶縁膜を形成する半導体装置の作製方法を提供する。

(もっと読む)

SOI基板の作製方法及び該SOI基板を用いた半導体装置

【課題】結晶欠陥が存在する単結晶半導体基板を用いる場合においても優れた特性のSOI基板を提供することを目的の一とする。また、このようなSOI基板を用いた半導体装置を提供することを目的の一とする。

【解決手段】単結晶半導体基板の一表面に、エピタキシャル成長法による単結晶半導体層を形成し、単結晶半導体層に第1の熱酸化処理を施して第1の酸化膜を形成し、第1の酸化膜の表面に対してイオンを照射することにより、単結晶半導体層にイオンを導入し、第1の酸化膜を介して、単結晶半導体層とベース基板を貼り合わせ、熱処理を施すことにより、イオンが導入された領域において単結晶半導体層を分離して、ベース基板上に単結晶半導体層の一部を残存させ、ベース基板上に残存した単結晶半導体層に対してレーザ光を照射し、ベース基板上に残存した単結晶半導体層に第2の熱酸化処理を施して第2の酸化膜を形成した後、該第2の酸化膜を除去する。

(もっと読む)

薄膜トランジスタおよびアクティブマトリクスディスプレイ

薄膜トランジスタが、絶縁基板上の半導体アイランド内に形成される。このトランジスタは、第1の伝導型のソース(1502)およびドレイン(1504)と、逆の第2の伝導型のチャネル(1508)とを備えている。チャネルは、1つまたは複数の絶縁ゲート(1510)と重なっており、分離ダイオードを備えている。各分離ダイオードは、低濃度にドープされた第1の領域(1506)と、高濃度にドープされ、第2の伝導型である第2の領域(1512)とを備えている。ダイオードは、絶縁ゲート(1510)とは重なっていない。第1の領域(1506)および第2の領域(1512)は、隣接するソースまたはドレインの長さよりも短い距離だけ、チャネル(1508)から延びている。低濃度にドープされた領域(1506)は、ソースまたはドレインから延びており、高濃度にドープされた領域(1512)は、低濃度にドープされた領域から延びているため、第1の領域(1506)および第2の領域(1512)は、トランジスタの主要伝導経路に直角の方向においては、隣接するソースまたはドレインとpn接合を形成するが、主要伝導経路に平行な方向においては形成しない。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

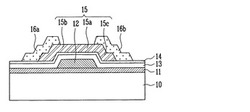

薄膜半導体装置およびその製造方法

【課題】コンタクトおよび配線形成時の合わせマージンがゼロであり、集積度を大幅に向上し、パターンレイアウトの自由度の拡大を可能とする薄膜半導体素子及びその製造方法を提供する。

【解決手段】透明絶縁性基板10上に形成され、第1導電型の不純物を含むソース領域及びドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極18、前記ソース領域又はドレイン領域の表面に形成された高融点金属と半導体との化合物からなる層、前記島状半導体層及びゲート電極を覆う層間絶縁膜29、及び前記ソース領域又はドレイン領域に接続された局所配線28を具備し、前記局所配線28は、前記ソース領域又はドレイン領域の表面に形成された前記化合物層と高融点金属層との2層構造、及び前記ソース領域又はドレイン領域の外側に形成された前記高融点金属層の延長からなることを特徴とする。

(もっと読む)

半導体装置

【課題】SOI技術で形成された単結晶シリコン薄膜から応力に起因する準位や欠陥を除去するための方法を提供する。

【解決手段】まずSmart−CutやELTRANといった代表的な貼り合わせSOI技術を用いて単結晶シリコン薄膜106を形成する。次に単結晶シリコン薄膜106をパターニングして島状シリコン層108とした後、ハロゲン元素を含む酸化性雰囲気中で熱酸化処理を行うことで、トラップ準位や欠陥の除去された島状シリコン層109を得る。

(もっと読む)

薄膜トランジスタ及び表示装置

【課題】薄膜トランジスタのオン電流及びオフ電流に係る問題点を解決する。また、高速動作が可能な薄膜トランジスタを提供する。

【解決手段】ゲート絶縁層を介して、少なくとも一部がゲート電極と重畳するように離間して設けられた、ソース領域及びドレイン領域を形成する一導電型を付与する不純物元素が添加された一対の不純物半導体層と、ゲート絶縁層上で、ゲート電極及び一導電型を付与する不純物元素が添加された一対の不純物半導体層と少なくとも一部が重畳し、チャネル長方向に離間して配設された一対の導電層と、ゲート絶縁層と一対の導電層に接し、該一対の導電層間に延在する非晶質半導体層と、を有する薄膜トランジスタである。

(もっと読む)

薄膜トランジスタ及び表示装置

【課題】薄膜トランジスタのオン電流及びオフ電流に係る問題点を解決する。また、高速動作が可能な薄膜トランジスタを提供する。

【解決手段】ゲート絶縁層を介してゲート電極と重畳するドナーとなる不純物元素を添加した半導体層と、ドナーとなる不純物元素を添加した半導体層上に重ねて設けられたバッファ層と、バッファ層の上面と、バッファ層及びドナーとなる不純物元素を添加した半導体層の側面を被覆する非晶質半導体層と、一端部がバッファ層と重なり、非晶質半導体層上に設けられ、ソース領域及びドレイン領域を形成する一導電型を付与する不純物元素を添加した一対の不純物半導体層とを有し、バッファ層の膜厚が、非晶質半導体層の膜厚よりも厚い薄膜トランジスタである。

(もっと読む)

201 - 220 / 535

[ Back to top ]