Fターム[4G077FE11]の内容

結晶、結晶のための後処理 (61,211) | 後処理−加熱、冷却処理 (955) | 加熱、冷却条件 (410)

Fターム[4G077FE11]の下位に属するFターム

Fターム[4G077FE11]に分類される特許

1 - 20 / 266

圧電基板の製造方法

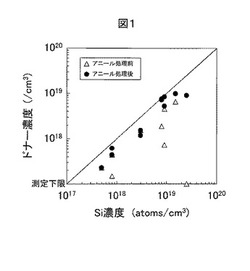

β−Ga2O3系基板の製造方法、及び結晶積層構造体の製造方法

【課題】還元雰囲気や不活性ガス雰囲気下におけるドナー濃度の変化が抑えられたβ−Ga2O3系基板の製造方法、及び還元雰囲気や不活性ガス雰囲気下において品質のばらつきの小さい高品質な結晶膜をエピタキシャル成長させることのできる結晶積層構造体の製造方法を提供する。

【解決手段】IV族元素を含むβ−Ga2O3系結晶からβ−Ga2O3系基板を切り出す工程を含み、還元雰囲気及び不活性ガス雰囲気の少なくともいずれか一方を含む雰囲気下でのアニール処理が、前記β−Ga2O3系基板を切り出す前の前記β−Ga2O3系結晶、又は切り出された前記β−Ga2O3系基板に施される、β−Ga2O3系基板の製造方法を提供する。

(もっと読む)

窒化物単結晶のアニール処理方法

【課題】アモノサーマル法で結晶成長した場合であっても、低抵抗で移動度が高い窒化物単結晶を簡便な方法で製造できるようにすること。

【解決手段】超臨界状態及び/又は亜臨界状態の窒素を含有する溶媒の存在下で結晶成長した窒化物単結晶を750℃以上で5.5時間以上アニール処理する。

(もっと読む)

処理板及び処理方法

【課題】二酸化炭素を効率よく還元することができる処理板及び処理方法を提供する。

【解決手段】二酸化炭素の処理板1は、基板2と、基板2上に形成され(111)面を表面とする酸化マグネシウムからなる処理膜3とを備える。処理膜3は二酸化炭素を吸着し、加熱により還元する属性を有している。基板2は、(111)面を主面とするチタン酸ストロンチウム、(0001)面を主面とするサファイア、又は(111)面を主面とするイットリア安定化ジルコニアのいずれか一つにより構成される。

(もっと読む)

グラフェンリボンを備える単結晶絶縁性基板の製造方法及びグラフェンリボンを備える単結晶絶縁性基板

【課題】グラフェンリボンの幅を揃えることを可能にすると共に、幅の揃ったグラフェンリボンを基板全面に備えることが出来る、グラフェンリボンを備える単結晶絶縁性基板の製造方法、及び、グラフェンリボンを備える単結晶絶縁性基板を提供する。

【解決手段】単結晶絶縁性基板を用意し、基板表面にグラフェンを固定し、コア粒子を内包するタンパク質の外径をピッチとして、コア粒子を内包するタンパク質を等間隔にグラフェン上に配置し、タンパク質を除去してコア粒子をグラフェン上に配置し、コア粒子によりグラフェンを切断して、グラフェンリボンを形成する。

(もっと読む)

窒化物系化合物半導体結晶及びその製造方法並びにIII族窒化物半導体デバイス用基板

【課題】GaN結晶インゴットを含む窒化物系化合物半導体結晶から自立基板を切り出す際のクラックの発生を抑制した窒化物系化合物半導体結晶及びその製造方法並びにIII族窒化物半導体デバイス用基板を提供する。

【解決手段】窒化物系化合物半導体結晶としてのGaN結晶インゴット100は、厚さ方向に沿って外周領域100aとその内側の中心領域100bとを有し、外周領域100aの厚さ方向に垂直な面(Ga極性のc面101)の転位密度の最大値が、中心領域100bの厚さ方向に垂直な面(Ga極性のc面101)の転位密度の最小値の2.0倍以上20倍以下となる転位密度分布を有する。

(もっと読む)

シリコンウェーハの製造方法

【課題】シリコン単結晶インゴットの育成効率を低下させることなく、熱処理装置の大型化、煩雑化を防止し、かつ、熱処理時におけるスリップ転位の発生や不純物汚染を抑制することができ、ウェーハの表層部及びバルク部においてもCOPやBMD等の欠陥を低減させることができるシリコンウェーハの製造方法を提供する。

【解決手段】CZ法によりV−リッチ領域からなる酸素濃度が0.8×1018atoms/cm3(old−ASTM)以下であるシリコン単結晶インゴットを育成する工程と、インゴットを切断してV−リッチ領域からなるスライスウェーハを得る工程と、スライスウェーハの表裏面を平坦化処理し、更にエッチング処理する工程と、エッチング後のウェーハを、熱処理用部材を用いて枚葉で単数又は複数保持して酸化性ガス雰囲気中、1150℃以上1200℃以下の最高到達温度で5分以上10時間以下熱処理する工程と、酸化膜を除去する工程と、少なくとも半導体デバイス形成面となる表面を鏡面研磨する工程と、を備える

(もっと読む)

シリコン基板の製造方法およびシリコン基板

【課題】酸素濃度を低減させたシリコン基板を製造するシリコン基板の製造方法を提供する。

【解決手段】チョクラルスキー法により製造されたシリコン単結晶体から切り出されたシリコン基板のデバイス形成予定領域部分を厚さ50〜200μmに加工し、温度T(℃)、時間t(秒)、初期酸素濃度Oi(原子個/cm3)としたとき、t=f(Oi)2(Tsi/200)2/{[0.52exp[−2.94×104/(273+T)]} (ただし式中、f(Oi)=1.43×10−69Oi4−3.35×10−51Oi3+2.51×10−33Oi2−3.99×10−16Oi−83.43である)で与えられる温度T(℃)以上の温度で、時間t(秒)以上の時間アニールする。

(もっと読む)

シリコンウェーハ及びその製造方法

【課題】 本発明は、LPDが極限まで低減され、検査工程及び出荷段階で不良品発生率が低いシリコンウェーハを、歩留まり良く製造できる方法を提供することを目的とする。

【解決手段】 本発明では、CZ法により育成された無欠陥シリコン単結晶からシリコンウェーハを製造する方法であって、

前記無欠陥シリコン単結晶からスライスされ、鏡面研磨されたシリコンウェーハを準備した後に、

前記鏡面研磨されたシリコンウェーハを、500℃以上600℃以下の温度で、4時間以上6時間以下の時間で熱処理する熱処理工程と、

前記熱処理工程後のシリコンウェーハを、研磨量が1.5μm以上となるように再研磨する再研磨工程とを行うことを特徴とするシリコンウェーハの製造方法を提供する。

(もっと読む)

半導体発光素子の製造方法

【課題】本発明は、半導体発光素子の製造方法に関する。

【解決手段】本発明の実施例による半導体発光素子の製造方法は、半導体成長用基板上に第1導電性半導体層、活性層及び第2導電性半導体層を順に成長させて発光部を形成する段階と、上記第2導電性半導体層上に上記発光部と結合されるように支持部を形成する段階と、上記発光部から上記半導体成長用基板を分離する段階と、上記分離された半導体成長用基板の表面に残存する半導体層が除去されるように上記半導体成長用基板にエッチングガスを適用する段階とを含む。

(もっと読む)

常磁性ガーネット単結晶及びその製造方法

【課題】高品質で大型のTGG結晶を、安価に且つ容易に製造できるようにする。

【解決手段】GGG結晶又はSGGG結晶からなる基板上に、LPE法で育成したTGG結晶である。前記TGG結晶は、組成Tb3 Mx Ga5-x O12で表され、MがSc、Inから選ばれる少なくとも1種の3価元素であって、基板がGGGの場合には0.1≦x≦0.5を満たし、基板がSGGGの場合は0.9≦x≦1.65を満たしており、且つ前記基板と育成したTGG結晶の垂直方向の格子定数差を±0.02Å以下とする。必要なガーネット原料と、PbO及びB2 O3 をフラックスとする融液の表面に、基板の片面を接触させ、850〜980℃でTGG結晶をLPE成長させる。融液中に、SiO2 、GeO2 、TiO2 から選ばれる1種以上の酸化物、あるいはCeO2 が含まれていてもよい。必要に応じて、育成したTGG結晶を還元処理する。

(もっと読む)

半導体素子の製造方法

【課題】SiC半導体基板の不純物元素を捕捉・固定するためのゲッタリング層の形成を含む半導体素子の製造方法を提供する。

【解決手段】SiC基板10上にSiCエピタキシャル層16を形成し、該エピタキシャル層16にイオン注入および熱処理を行なって半導体素子を製造する方法において、上記SiC基板10よりも欠陥密度の高いゲッタリング層13を形成する工程を含むことを特徴とする半導体素子の製造方法。

(もっと読む)

III族窒化物結晶の製造方法およびIII族窒化物結晶

【課題】加工性に優れていて品質が高いIII族窒化物結晶を提供すること。

【解決手段】III族窒化物単結晶を1000℃以上で熱処理することによりIII族元素を含む化合物からなる被膜を形成し、その被膜を除去することによりIII族窒化物結晶を製造する。

(もっと読む)

炭化珪素単結晶育成用原料の製造方法

【課題】純度の向上と、収率の低下とのトレードオフ関係を改善した炭化珪素単結晶育成用原料の製造方法を提供する。

【解決手段】炭素坩堝を用いた昇華再結晶法による結晶成長に際して形成され、炭素坩堝1に結合した再結晶析出物を、炭素坩堝1ごと粉砕し、再結晶析出物が結合した状態で破片となった炭素坩堝材に水を浸透させる、水が浸透した破片状の炭素坩堝材に対して、水が凍結、融解する温度での温度サイクルを複数回繰り返した後、温度サイクルをかけられた炭素坩堝材を粉砕して炭化珪素単結晶育成用原料とする。

(もっと読む)

III族窒化物半導体結晶の製造方法

【課題】結晶成長の終了後にGaN結晶を安全に取り出すことができること。

【解決手段】Naフラックス法によるGaN基板の育成終了後、温度500℃、圧力10PaでNaを蒸発させた。そして、排気管14を通して気体のNaを排出し、冷却器15によってNaを液化してNa回収タンク17によりNaを回収した。その後、圧力を大気圧に戻し、加熱を停止して温度を常温まで下げ、反応容器10を開封して中から坩堝11を取り出した。このとき、坩堝11内にはNaはほとんど残留していないため、GaN基板を短時間で安全に取り出すことができる。また、回収したNaは高純度であり、フラックスとして再利用することができる。

(もっと読む)

シリコンウェーハの熱処理方法

【課題】ボイド欠陥の消滅力が高い高温下でRTPを行っても、表面粗さの悪化を抑制することができ、更に、凹形状のピットの発生も抑制することができるシリコンウェーハの熱処理方法を提供する。

【解決手段】少なくとも半導体デバイスが形成される表面が鏡面研磨されたシリコンウェーハをフッ化水素系溶液により前記表面のシリコン原子を水素で終端させて、前記表面の水素終端密度を5×1014atoms/cm2以上1×1016atoms/cm2以下とする工程と、前記水素で終端させたシリコンウェーハを、不活性ガス雰囲気中、1300℃以上1400℃以下の温度範囲に急速昇温し保持した後、急速降温する急速昇降温熱処理を行う工程と、を備える。

(もっと読む)

III族金属窒化物の加工された非極性面を有する基板およびその製造方法

【課題】III族金属窒化物の非極性面を有する基板を研磨加工することで極めて平坦な表面を形成しつつ、かつその表面の加工歪みを取り除くことによって、III族金属窒化物の無歪研磨加工面を得ることである。

【解決手段】本方法は、III族金属窒化物の非極性面を有する基板を研磨加工し、前記非極性面の平均表面粗さ(Ra)を1nm以下とする研磨加工工程、次いで基板を不活性雰囲気下で熱処理する熱処理工程、および基板の非極性面を、ハロゲン含有ガスを用いて反応性ドライエッチングするか、または化学機械研磨加工する加工工程を有する。

(もっと読む)

シリコン基板の製造方法及びシリコン基板

【課題】表層にRIE欠陥がなく、かつライフタイムが十分長いシリコン基板の製造方法及びシリコン基板を提供することを目的とする。

【解決手段】チョクラルスキー法により育成したシリコン単結晶インゴットから切り出されたシリコン基板に、急速加熱・急速冷却装置を用いて、1300℃より高くかつシリコン融点以下の温度で1〜60秒保持して急速熱処理を施した後、600〜800℃の範囲の温度まで降温速度5〜150℃/secで一段目の降温工程を行い、その後、冷却時間X秒と降温速度Y℃/secが、X<100の場合はY≦0.15X−4.5を、X≧100の場合はY≦10を満たすように二段目の降温工程を行うシリコン基板の製造方法。

(もっと読む)

シリコン単結晶ウェーハの製造方法及びアニールウェーハ

【課題】大口径に対応可能なCZ法で製造したV領域のウェーハを用いて、バルク中の欠陥を無欠陥とし、さらに中性子照射を行わなくても、中性子照射を行った場合と同程度の面内抵抗率分布とすることにより、IGBT向けに適用可能な低コストのシリコン単結晶ウェーハを製造する方法を提供する。

【解決手段】チョクラルスキー法により育成されたV領域のシリコン単結晶インゴットから得られた酸素濃度7ppma未満、窒素濃度1×1013〜1×1014atoms/cm3のシリコン単結晶ウェーハに対して、非窒化性雰囲気下、1150〜1300℃で、1〜120分の熱処理を行うことにより、バルク中の15nm以上の結晶欠陥の密度が2×106/cm3以下となる。

(もっと読む)

シリコンエピタキシャルウェーハおよびその製造方法

【課題】エピタキシャル欠陥がテイル部付近の直胴部で発生することを防止できる窒素ドープエピウェーハの製造方法を提供する。

【解決手段】CZ法にて窒素ドープしたシリコン単結晶を引き上げる際に、引上速度V[mm/min]と、融点〜1350℃までの結晶成長軸方向の平均温度勾配G[℃/mm]との比をV/G[mm2/℃min]≧0.25に設定し、かつ、800〜750℃の温度領域の冷却速度Cv≧1.7℃/minとする。

(もっと読む)

1 - 20 / 266

[ Back to top ]