Fターム[4M104BB03]の内容

Fターム[4M104BB03]に分類される特許

41 - 60 / 270

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置を提案することを課題とする。

【解決手段】基板上に形成されたゲート電極と、ゲート電極上に形成された酸素過剰のSiOX膜と、SiOX膜上に形成された酸化物半導体膜と、を有する半導体装置。

(もっと読む)

発光表示装置及び発光表示装置の作製方法

【課題】薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製する方法を提供する。

【解決手段】剥離層を介して基板上に素子領域を形成する際に、半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行う。更に素子領域を基板から剥離して、じん性の高い第1の支持体に設け、第1の支持体及びじん性の高い第2の支持体で液晶素子を挟持することで、薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製できる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】非酸化雰囲気下でなくても、良好なオーミック電極を形成可能な技術を提供する。

【解決手段】オーミック電極を有する半導体装置の製造方法であって、半導体基板50上に金属層30eを形成する工程と、金属層30e上に透過膜30fを形成する工程と、透過膜30fを通して金属層30eに電磁波を照射して、金属層30eを加熱する工程と、透過膜30fを除去する工程を有する。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】信頼性を向上させることができる半導体装置を得る。

【解決手段】半導体素子10のエミッタ電極12の一部の領域上に多層メタル20が形成されている。多層メタル20に外部電極22が半田24を介して接続されている。半導体素子10はモールド樹脂36に覆われている。多層メタル20の終端部の直下に第1のセル38aが存在し、多層メタル20の終端部の直下以外に第2のセル38bが存在する。第2のセル38bにはIGBTが形成され、第1のセル38aにはIGBTが形成されていない。

(もっと読む)

半導体装置およびその製法

【課題】トレンチ構造のトランジスタセルがマトリクス状に多数個形成され、そのゲート電極に金属膜からなるゲート配線がコンタクトされる半導体装置でも、ゲート耐圧を充分に高くすることができる構造の半導体装置を提供する。

【解決手段】半導体層1に凹溝11が形成され、その凹溝11内にゲート酸化膜4が形成され、その凹溝11内にポリシリコンなどからなるゲート電極5が設けられるトレンチ構造のトランジスタセルがマトリクス状に配列されたセル領域10を有している。そして、金属膜からなるゲート配線9とコンタクトするため、ゲート電極5と連続してゲートパッド部5aが設けられるが、そのゲートパッド部5aが凹溝11と同時に設けられる凹部12内に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体チップの割れや欠けを防止し、デバイス特性を向上することができる半導体装置および半導体装置の製造方法を提供すること。

【解決手段】半導体チップ10の素子端部の側面には、分離層3が設けられている。また、半導体チップ10の素子端部には、凹部4によってひさし部5が形成されている。コレクタ層6は、半導体チップ10の裏面に設けられ、凹部4の側壁22および底面23に延在し、分離層3に接続されている。コレクタ層6の表面全体には、コレクタ電極7が設けられている。凹部4の側壁22上のコレクタ電極7は、最表面の電極膜の厚さが0.05μm以下となっている。半導体チップ10の裏面に設けられたコレクタ電極7は、はんだ層11を介して、絶縁基板12上に接合されている。はんだ層11は、半導体チップ10の裏面の平坦部21に設けられたコレクタ電極7を覆うように設けられている。

(もっと読む)

半導体装置、貼り合せ基板およびそれらの製造方法

【課題】低コストで高品質の半導体装置、および当該半導体装置の製造に用いる貼り合せ基板、およびこれらの製造方法を提供する。

【解決手段】半導体素子の製造方法は、単結晶半導体部材を準備する工程(S10)と、支持基材を準備する工程(S20)と、支持基材と単結晶半導体部材とを、炭素を含む接合層を介して接合する工程(S30)と、単結晶半導体部材の表面にエピタキシャル層を形成する工程(S40)と、エピタキシャル層を利用して半導体素子を形成する工程(S50)と、半導体素子を形成する工程(S50)の後、接合層を酸化することにより分解して支持基材から単結晶半導体部材を分離する工程(S60)と、支持基材から分離された単結晶半導体部材を分割する工程(S80)とを備える。

(もっと読む)

成膜方法及び半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供することを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でスパッタリングを行う。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

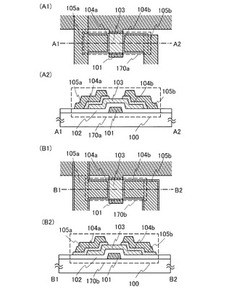

半導体素子

【課題】垂直に形成されたナノワイヤを構成要素として備える半導体素子の寄生容量増加を抑制し、動作速度時定数が改善される半導体素子を提供する。

【解決手段】導電性基板101の主平面と電極109間の層間絶縁膜を膜厚調整層102と保護絶縁層103の2層化することにより、膜密着性の乏しい低誘電率膜102と電極109を保護絶縁層103で隔てることによってはがれを抑制しながら、主平面101と電極109間を電気的に接続するナノワイヤ107と、導電性基板101と電極109の間の寄生容量を低減する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置がSBDとして良好なショットキー特性を得ることができるようにする。

【解決手段】主面2a側がn型領域12とされると共に当該主面2aにp型領域15を形成してなる炭化珪素基板の主面2aのうち、p型領域15の表面15aのみを荒らす粗面化工程と、前記炭化珪素基板2の主面2aを洗浄液により洗浄する洗浄工程と、一種類の金属材料からなる一体の電極用金属層を、前記n型領域12の表面12a及び前記p型領域15の表面15aの両方に接触させるように、前記主面2aに形成する接続工程とを備える半導体装置の製造方法を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】パターン外析出を抑制し、密着力を向上させることができる半導体装置を提供する。

【解決手段】半導体ウエハ1と、半導体ウエハ1上にパターンニングして形成され最表面に複数の凹部9が形成されたAl−Si金属層2と、Al−Si金属層2上と半導体ウエハ1が露出した箇所上に形成された酸化膜11と、Al−Si金属層2上に酸化膜11を介して各凹部9を埋め込むように形成されたNiめっき膜3およびAuめっき膜4とを備える。

(もっと読む)

熱処理方法および熱処理装置、ならびに半導体装置の製造方法

【課題】従来技術よりも小さい熱エネルギーで、SiC基板上に低抵抗のオーミック電極を形成することができ、熱処理における半導体装置の素子部の損傷および特性の劣化を防止することができる熱処理方法および熱処理装置、ならびに前記熱処理方法を用いた半導体装置の製造方法を提供する。

【解決手段】熱処理装置1の電源部21によって、複数のパルスを含むパルス列で構成される複数パルス電流を発生させ、導線22および電流端子部23を介して、SiC基板11上の電極金属膜12に供給する。これによって電極金属膜12にジュール熱を発生させ、発生したジュール熱によって電極金属膜12を加熱する。

(もっと読む)

半導体装置

【課題】IGBTにおいて、P型コレクタ層におけるキャリア濃度の変化を抑制し、オン電圧のばらつきを低減可能な技術を提供することを目的とする。

【解決手段】半導体装置は、表面側にMOSFET構造1が形成されたN型半導体基板2と、N型半導体基板2の裏面に形成されたP型コレクタ層4とを備える。そして、P型コレクタ層4上にストライプ状に互いに離間して形成された、AlとSiとのAl合金からなるAlSi電極7aを含む積層構造の裏面電極7を備える。

(もっと読む)

ショットキーバリアダイオード

【課題】順方向サージ耐圧と順方向降下電圧VFとのトレードオフ特性を改善することが可能で、かつ、逆方向漏れ電流IRが増加してしまうことのないショットキーバリアダイオードを提供する。

【解決手段】第1主面及び当該第1主面の反対面である第2主面を有し、炭化珪素からなるn型の半導体基体110と、半導体基体110における第1主面上に形成されたバリアメタル層118と、半導体基体110における第1主面側の表面に部分的に形成され、高濃度のp型不純物を含有する小数キャリア注入層128と、小数キャリア注入層128の直下にのみカーボンが導入されたカーボン導入層132とを備えるショットキーバリアダイオード100。

(もっと読む)

電力半導体装置およびその製造方法

【課題】本発明は、コレクタ電極に含まれるアルミニウムがコレクタ層へ拡散することを防止でき、かつ安定した電気特性を有する電力半導体装置およびその製造方法を提供することを目的とする。

【解決手段】基板の表面に形成されたエミッタおよびゲートと、該基板の裏面に形成されたコレクタ層と、該コレクタ層の該基板と接する面と反対の面に形成された酸化膜と、該酸化膜の該コレクタ層と接する面と反対の面に形成された、アルミニウムを含むコレクタ電極と、を備えたことを特徴とする。

(もっと読む)

41 - 60 / 270

[ Back to top ]