Fターム[4M104BB03]の内容

Fターム[4M104BB03]に分類される特許

21 - 40 / 270

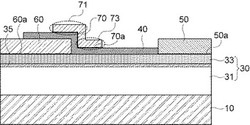

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】良好なオン特性を維持したまま、逆方向バイアスに対するリーク電流を低減した半導体デバイスを得る。

【解決手段】窒化物系化合物半導体からなるチャネル形成層と、チャネル形成層上に設けられ、第1の窒化物系化合物半導体からなる第1の半導体層、および、第2の窒化物系化合物半導体からなる第2の半導体層を有する疑似混晶からなる疑似混晶層と、疑似混晶層上に設けられ、窒化物系化合物半導体からなり、チャネル形成層の多数キャリアと反対の導電型を有する導電半導体層と、導電半導体層に接する第1の電極と、チャネル形成層に電気的に接続された第2の電極と、を備える半導体デバイスを提供する。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

半導体装置

【課題】金属酸化物中の酸素欠損を低減し、電気的特性の安定した半導体装置を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の金属酸化物膜と、第1の金属酸化物膜に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極上に設けられたパッシベーション膜と、を有し、パッシベーション膜は、第1の絶縁膜と、第2の金属酸化物膜と、第2の絶縁膜とが順に積層された半導体装置である。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間にバッファ層が設けられた逆スタガ型(ボト

ムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン

電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設

けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

半導体装置及び電子機器

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導

体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作

製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって

形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチ

ング工程において、第1のエッチング工程は、エッチングガスによるドライエッチングを

用い、第2のエッチング工程はエッチング液によるウエットエッチングを用いる。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧な半導体素子を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、第一と第二の主面を有する炭化珪素基板と、炭化珪素基板の第一の主面に設けられた第一導電型の第一の炭化珪素層と、第一の炭化珪素層の表面に形成された第二導電型の第一の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第一導電型の第二の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第二導電型の第三の炭化珪素領域と、第一の炭化珪素層、第一の炭化珪素領域および第三の炭化珪素領域の表面に連続的に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された炭化珪素からなる第一の電極と、第一の電極上に形成された第二の電極と、第一と第二の電極を被覆する層間絶縁膜と、第二の炭化珪素領域と第三の炭化珪素領域と電気的に接続される第三の電極と、炭化珪素基板の第二の主面に形成された第4の電極と、を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】複数の金属層が積層された電極構造を有する半導体装置を容易に製造することができる半導体装置の製造方法を提供する。

【解決手段】 半導体層と、その半導体層の表面に形成されている第1金属層と、第1金属層の少なくとも一部が露出するように第1金属層に隣接する位置に形成されている絶縁層とを有する半導体基板を用いて、半導体装置を製造する方法であって、露出部分の第1金属層の表面及び絶縁層の表面に、絶縁層に対するよりも第1金属層に対する接着性が高い第2金属層を形成する工程と、第1金属層の表面に形成された第2金属層を残存させながら、絶縁層の表面に形成された第2金属層を絶縁層から剥離する工程を有する。

(もっと読む)

アルミニウム膜被着方法

【課題】薄い基材上に厚いアルミニウムを被着させても基材が撓むことのない被着方法を提供する。

【解決手段】基材を静電チャック上に配置し、静電チャックにバイアスを印加しない状態でアルミニウムの第1層を被着させ、次に静電チャックにバイアスを印加して基材を支持体に密着し、そして第1層より厚いアルミニウムの第2層を22℃未満の基材温度で第1層に連続して被着させる。

(もっと読む)

Al基合金スパッタリングターゲット、及びCu基合金スパッタリングターゲット

【課題】Al基合金スパッタリングターゲットやCu基合金スパッタリングターゲットを用いたときのプレスパッタリング時、及び続いて行われる基板等へのスパッタリング時の成膜速度が高められ、且つスプラッシュなどのスパッタリング不良を抑制し得る技術を提供すること。

【解決手段】Al基合金またはCu基合金スパッタリングターゲットの最表面から1mm以内の深さのスパッタリング面法線方向の結晶方位<001>±15°と、<011>±15°と、<111>±15°と、<112>±15°と、<012>±15°との合計面積率をP値としたとき、下記(1)および/または(2)の要件を満足するスパッタリングターゲット。

(1)前記P値に対する、<011>±15°の面積率PA:40%以下、

(2)前記P値に対する、<001>±15°と<111>±15°との合計面積率PB:20%以上

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

超高速リカバリダイオード

【課題】ソフトリカバリ特性を維持する逆回復電荷を低減した高速リカバリダイオードを提供する。

【解決手段】整流装置100は、第1の極性の基板と、基板に結合された第1の極性の低濃度ドープ層180と、低濃度ドープ層と共に配置された金属層140とを備える。超高速リカバリダイオードは、互いに離間され、低濃度ドープ層内に形成され、第2の極性のドーピングを備える複数のウェル150を含む。複数のウェルは金属層130に接続する。超高速リカバリダイオードは、複数のウェルのウェル間に位置し、低濃度ドープ層より高濃度に第1の極性がドープされた複数の領域160をさらに含む。

(もっと読む)

半導体装置の製造方法、および、半導体装置

【課題】ニッケルめっき電極を備え、低VFを兼ね備えた半導体装置の製造方法、および、半導体装置を提供することを目的としている。

【解決手段】n型半導体基板の一方の表面近傍に、小電流領域の電圧降下を得るべく濃度設定されたp型の半導体層を形成してpn接合を形成する工程と、p型の半導体層表面に、鉛を含有するガラスパッシベーション膜を形成し、形成したガラスパッシベーション膜の一部を除去して開口部を形成する工程と、開口部を形成した後、p型の半導体層表面に、アルミニウムの膜を形成する工程と、アルミニウムとp型の半導体層のシリコンを、熱処理により反応させてアルミニウム・シリサイド膜を生成する工程と、アルミニウム・シリサイド膜上部に存在するシリコンと未反応のアルミニウムを、エッチングにより除去して表面を粗面化する工程と、粗面化されたアルミニウム・シリサイド膜の上にニッケル電極を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】特性測定用のステージにゴミがある場合でも、ウェハ状態でのチップ形成箇所のピエゾ効果による漏れ電流の誤判定が起こり難い半導体装置を提供すること。

【解決手段】n半導体基板1の裏面側に形成したnフィールドストップ層9と、このnフィールドストップ層9の表面層に形成したpコレクタ層10とからなる裏面拡散層16の厚さが5μm以下と薄い場合に、Ti膜11,13、やNi膜14などの積層膜で形成される裏面電極19のその積層膜に0.3μm〜4μmの厚さのAl−Si膜12を挟み応力緩衝することで、ピエゾ効果によるウェハ状態でのチップの漏れ電流の誤判定率を低下させる。

(もっと読む)

半導体装置

【課題】しきい値電圧の経時的な低下を抑制でき、またアルミ配線による絶縁膜の腐食やAlスパイクに起因するゲート・ソース間の短絡を防止できる半導体装置を提供する。

【解決手段】半導体装置のMOSFETセルは、ポリシリコンのゲート電極6およびn-ドリフト層2の上部に形成されたn+ソース領域4を備える。ゲート電極6上は層間絶縁膜7によって覆われており、Alのソース電極101は、層間絶縁膜7上に延在する。またゲート電極6にはAlのゲートパッド102が接続される。ソース電極101と層間絶縁膜7との間、並びにゲートパッド102とゲート電極6との間のそれぞれに、Alの拡散を抑制するバリアメタル層99が配設される。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで高い信頼性を有する、半導体装置およびその製造方法を提供すること。

【解決手段】n型半導体基板の一方の主面に、p型ベース領域とn型エミッタ領域と所要の位置にゲート絶縁膜を介して載置されるゲート電極とからなるMOSゲート構造と該MOSゲート構造を沿面方向に取り巻く耐圧構造部とを有し、他方の主面に1μm以下の浅い逆阻止接合を有するp型コレクタ層を備える半導体装置において、前記コレクタ層の他方の主面上に、バッファ絶縁層を介して被覆されるコレクタ電極が、前記バッファ絶縁層に設けられたコンタクトホールを通して前記コレクタ層と導電接触する半導体装置とする。

(もっと読む)

21 - 40 / 270

[ Back to top ]