Fターム[4M104BB03]の内容

Fターム[4M104BB03]に分類される特許

61 - 80 / 270

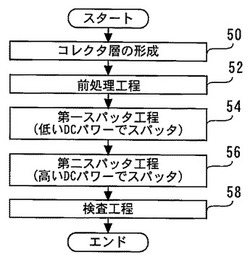

半導体装置の製造方法

【課題】本発明は、スパッタ装置の処理能力を損なうことなく、スパッタに異常がないときは金属薄膜の反射率を面内で均一にすることができる半導体装置を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、シリコン基板にスパッタ成長により金属膜を形成する第1スパッタ工程と、該第1スパッタ工程の後に該第1スパッタ工程よりも高いDCパワーでさらに金属膜をスパッタ成長させる第2スパッタ工程と、該第1スパッタ工程と該第2スパッタ工程の後に、該第1スパッタ工程および該第2スパッタ工程で形成された金属膜の反射率の均一性を測定する検査工程とを備えたことを特徴とする。

(もっと読む)

半導体装置及び電子機器

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、第1の導電層の端面よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上に、前記伸長した領域のチャネル長方向の長さより小さいチャネル長方向の長さの底面を有するサイドウォール絶縁層を有する半導体装置である。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含む半導体装置である。

(もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

半導体装置

【目的】活性部の端部に形成されたトレンチの電界強度を緩和しながら、少数キャリアを注入させることなく、耐圧の高い半導体装置を提供する。

【解決手段】TMBSダイオードの活性部21と耐圧構造部22において、活性部トレンチ12を取り囲むように端部トレンチ7が設けられ、アノード電極3の外周側の端部である活性端部19は、端部トレンチ7の内部に設けられた導電性のポリシリコン13と接している。端部トレンチ7と離間して端部トレンチ7を取り囲むようにガードトレンチ8が形成されている。またアノード電極3の外周部にアノード電極3とは離間してフィールドプレート9が設けられている。フィールドプレート9は、端部トレンチ7とガードトレンチ8の間のメサ領域18におけるn型ドリフト層2の表面の一部と、ガードトレンチ8の内部に形成されている導電性ポリシリコン13の両方と接している。

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体基板の製造方法およびレーザアニール装置

【課題】一面側に金属電極が形成された半導体基板のアロイ化を良好に行うことを可能にする製造方法および装置を提供する。

【解決手段】一面側に金属電極が形成され、所望により他面側に金属薄膜や化合物半導体層が形成された半導体基板に対し、パルス発振レーザを出射するパルス発振レーザ光源または連続発振レーザを出射する連続発振レーザ光源から出力された波長500〜550nmかつ半値幅300ns以上としたパルス発振レーザまたは波長500〜550nmで同一箇所に半値幅300ns以上で照射される連続発振レーザを金属電極側から半導体基板に照射しつつ相対的に走査して前記基板に対するアロイ処理を行う。

(もっと読む)

半導体装置およびその作製方法

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

非線形素子、該非線形素子を有する表示装置および該表示装置を有する電子機器

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有する薄膜トランジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms≦χ<φmdの関係になるように構成する。また、薄膜トランジスタのゲート電極とドレイン電極を電気的に接続することで、さらに整流特性の良い非線形素子を実現することができる。

(もっと読む)

ドープされたシリコン層の製造方法、該方法によって得られるシリコン層およびその使用

本発明は、基板上のドープされたシリコン層の製造方法であって、次の工程(a)液体シラン配合物および基板の準備、(b)該基板に該液体シラン配合物を塗布、(c)電磁エネルギーおよび/または熱エネルギーの導入、(d)少なくとも1種の、アルミニウムを含有する金属錯体化合物を有する液体調製物の準備、(e)前記工程(c)によって得られたシリコン層に該調製物を塗布、そして引き続き(f)電磁エネルギーおよび/または熱エネルギーの導入によって、前記工程(e)によって得られた被覆の加熱、そして引き続き(g)前記工程(f)によって得られた被覆の冷却、を含むドープされたシリコン層の製造方法、該法によって得られるドープされたシリコン層ならびに感光性素子および電子素子を製造するための該シリコン層の使用に関する。  (もっと読む)

(もっと読む)

半導体装置

【課題】IGBTとセットでFWダイオードとして使用される単体のショットキ・バリア・ダイオードにおいては、半田層を介して、表面のアノード電極をメタル・クリップに接続するケースが多い。この場合、アルミニウム系アノード電極上のポリイミド系ファイナル・パッシベーション膜の開口上にUBM層を設けるが、UBM層およびポリイミド系膜がともに、引っ張り応力を有するため、下地のアルミニウム系膜に両引っ張り応力によるクラックが発生する。

【解決手段】本願発明は、半導体基板の主面に設けられたSBDの活性領域および、その端部から外側の周辺部に設けられたPSG膜被覆領域を有するSBD素子において、アノード電極を構成するアルミニウム系メタル膜上に相補的に設けられた有機系ファイナル・パッシベーション膜とUBM層の境界部分をPSG膜被覆領域に設けたものである。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、歩留まりを向上できる半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体素子の製造方法は、半導体基板上に第1の絶縁膜を形成する工程と、前記第1の絶縁膜の一部をエッチングして複数段の段部を形成する工程と、前記第1の絶縁膜上に前記段部を覆うように導電層を形成する工程と、前記導電層の前記段部を覆う部分をエッチングする工程と、を備えることを特徴とするものである。

(もっと読む)

半導体装置

【課題】半導体基板に縦型パワートランジスタが形成され、該半導体基板の主面側と裏面側にそれぞれ電極が形成されてなる半導体装置であって、半導体基板の主面側と裏面側とで残留応力が低くバランスされており、半田接合に際して剥がれや亀裂等の不具合が生じ難い電極構造を有してなる半導体装置を提供する。

【解決手段】主面側の半導体基板1上に保護膜5が形成され、第1下地電極層14に接続する第1金属電極30aが保護膜5に設けられた開口部5kを介して外部に露出すると共に、裏面側の半導体基板1上の全面に第2下地電極層14bに接続する第2金属電極30bが形成され、第1金属電極30aと第2金属電極30bが、半導体基板1側から外部側に向かって、スパッタにより形成された同じ層数で対応する各層が同じ材料からなる積層構造を有してなる半導体装置100とする。

(もっと読む)

耐酸化性酸化ホウ素層を含む電極およびその製造方法

ここで開示されているのは、銅、ニッケル、鉄、コバルト、チタン、鉛、アルミニウム、スズおよびこれらの金属の1つを主成分として含む合金からなる群から選択される導電性構成成分を含む導電層と、酸化ホウ素を含む酸化保護層とを含む電極であって、前記酸化保護層が導電層の上面を被覆するかまたは導電層の上面および側面の両方を被覆するかまたは導電層が形成されている全ての場所を被覆する電極であって;導電層および酸化保護層を同時に空気焼成することによって形成される電極である。 (もっと読む)

半導体装置の製造方法

【課題】素子の特性の変動を抑えること。

【解決手段】面方位が(100)面のシリコン基板1の表面に、1nm以下の酸化膜10を形成する。そして、この酸化膜10の表面に、スパッタリングによってアルミニウムを積層することで、全面が(111)面のアルミニウム膜2を形成する。そして、アルミニウム膜2の表面に、無電解めっき処理によりニッケルめっき層を形成する。また、アルミニウム膜2を形成した後、シリコン基板1とアルミニウム膜2とをシンタリングする際に、酸素濃度に合わせて、熱処理温度を調整する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタは、基板1、チャネル層3及びバリア層4と、バリア層4上にこの順で離間して設けられたソース電極6、ゲート電極7およびドレイン電極8とを備え、ソース電極6の直下に第1のn型不純物拡散領域12が設けられ、ドレイン電極8の直下に第2のn型不純物拡散領域13が設けられ、第2のn型不純物拡散領域の下側の前記チャネル層3および第2のn型不純物拡散領域の前記ゲート電極側の前記チャネル層3および前記バリア層4に第3のn型不純物拡散領域15が設けられる。第3のn型不純物拡散領域15は第2のn型不純物拡散領域13よりも低いn型不純物濃度を有し、ゲート電極とドレイン電極との間に電圧が印加されたときバリア層4およびチャネル層3においてその絶縁破壊強度を超える電界集中が生じることを抑制する。

(もっと読む)

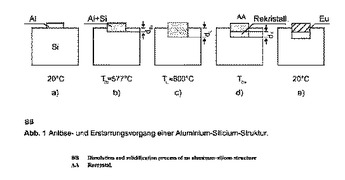

半導体装置およびその製造方法

【課題】リーク電流を抑え、微小電流が流れる領域で電圧降下を低くすることができる半導体装置およびその製造方法を提供することを目的としている。

【解決手段】半導体装置の製造方法は、n型半導体層の一方の表面近傍に、微小電流が流れる領域で電圧降下が生じるように濃度設定されたp型半導体層を形成してpn接合を形成し、p型半導体層の表面に、アルミニウムの膜を形成し、アルミニウムとp型半導体層のシリコンを、焼結処理により反応させてアルミニウム・シリサイド膜を生成し、アルミニウム・シリサイド膜の上部に存在するアルミニウムであって、シリコンとは未反応のアルミニウムを、エッチングにより除去して表面を粗面化し、粗面化されたアルミニウム・シリサイド膜の上に、ニッケル膜を形成する。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置の作製方法

【課題】特性の良い半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】基板上に、ゲート電極として機能する第1の導電層を形成する工程と、第1の導電層を覆うように第1の絶縁層を形成する工程と、第1の導電層と一部が重畳するように、第1の絶縁層上に半導体層を形成する工程と、半導体層と電気的に接続されるように第2の導電層を形成する工程と、半導体層および第2の導電層を覆う第2の絶縁層を形成する工程と、第2の導電層と電気的に接続される第3の導電層を形成する工程と、半導体層を形成する工程の後、第2の絶縁層を形成する工程の前の第1の熱処理工程と、第2の絶縁層を形成する工程の後の第2の熱処理工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の表面側で、Al電極膜表面にボイドが形成され難くすることのできる半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の一方の主面側に半導体機能領域と所要のコンタクトホール8を含む層間絶縁膜7パターンを形成した後、該半導体基板1の前記一方の主面側の全面に、厚膜のアルミニウム膜またはアルミニウム合金膜を成膜して前記コンタクトホール8の底面を含む半導体基板1表面に導電接触させて所要の電極膜9を形成する際に、前記アルミニウムの成膜工程を膜厚に関して複数回に分け、複数回の前記アルミニウム成膜工程の間に、直前のアルミニウム膜表面の凹凸を等方性エッチングにより平坦化する工程を設ける半導体装置の製造方法とする。

(もっと読む)

61 - 80 / 270

[ Back to top ]