Fターム[4M104DD07]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は絶縁膜の除去方法 (1,213)

Fターム[4M104DD07]の下位に属するFターム

ドライエッチ (710)

ウェットエッチ (218)

ドライ、ウェットの併用 (39)

Fターム[4M104DD07]に分類される特許

161 - 180 / 246

半導体装置及びその製造方法

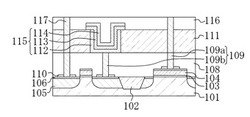

【課題】シリサイド層の凝集を抑えることができ、コンタクト抵抗が低抵抗化され、断線の発生が抑制された半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板101上に形成されたゲート電極104および不純物拡散領域105と、ゲート電極14および不純物拡散領域105の上に形成されたシリサイド層106と、シリサイド層106上に形成された第1のエッチングストップ膜110とを備えている。第1のエッチングストップ膜110は、シリサイド層106上に設けられた下層コンタクトプラグ109の側面を囲んで形成される。

(もっと読む)

半導体装置の製造方法

【課題】導電体プラグと金属シリサイド層との接触面積を容易に確保することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板11上にゲート電極12が形成される。ゲート電極12の側面には、サイドウォール絶縁膜14が形成される。ゲート電極12およびサイドウォール絶縁膜14をマスクとして、半導体基板11に不純物領域15が形成される。不純物領域15の表面に、金属シリサイド層16が形成される。金属シリサイド層16が形成されると、サイドウォール絶縁膜14底面のエッジをゲート電極12側に後退させるエッチングが行われる。当該エッチングが行われた半導体基板11上に、ライナー膜17、および層間絶縁膜18が形成された後、層間絶縁膜18およびライナー膜17にコンタクトホール19が形成される。コンタクトホール19に導電体を充填することで、導電体プラグ20が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極をより確実にフルシリサイド化できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10に、活性領域11よりも高い上面を有する素子分離領域12を形成した後、活性領域11および素子分離領域12の上にゲート配線形成用膜14および保護膜形成用膜15を形成する。その後、保護膜形成用膜15を研磨して平坦化する。次に、パターニングを行うことにより、ゲート電極部14a、ゲート配線部14bおよび保護膜15a、15bを形成した後、サイドウォール17を形成する。

(もっと読む)

半導体装置、およびその製造方法

【課題】高い信頼性と低い電気抵抗を有する配線構造を備えた半導体装置、およびその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成されたシリサイド層と、

前記シリサイド層上に形成された層間絶縁膜と、前記層間絶縁膜内に形成され、前記シリサイド層に前記コンタクト膜を介して電気的に接続された金属層と、前記金属層と前記層間絶縁膜との間に形成された拡散バリア膜と、を備え、前記コンタクト膜は、前記金属層に含まれる金属元素と、前記拡散バリア膜に含まれる金属元素と、前記シリサイド層に含まれる金属元素またはSiと、を少なくとも1つずつ含むことを特徴とする半導体装置を提供する。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】導電層上にマスクを設け、マスクを設けた導電層上に絶縁膜を成膜し、マスクを除去することで開口を有する絶縁層を形成する。露出した導電層と接するように開口に導電膜を形成することによって、導電層及び導電膜は絶縁層を介して電気的に接続することができる。開口の形状はマスク形状を反映し、柱状(角柱、円柱、三角柱など)、針状などを用いることができる。

(もっと読む)

コンタクトエリアに金属シリサイド領域が局所的に設けられたトランジスタ及び該トランジスタを形成するための方法

誘電材料層などのパターニングされた誘電層に基づいてシリサイデーションプロセスを実行することによって、各々の金属シリサイド部位を各々のコンタクト領域に非常に局所的なやり方で供給することができ、一方で、全体の金属シリサイド量を著しく減らすことができる。このようにして、金属シリサイドが電界効果トランジスタのチャネル領域に及ぼす悪影響を著しく減らすことができ、なおかつコンタクト抵抗を小さく維持することができる。  (もっと読む)

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】実施例に係る半導体素子は、所定の金属層が形成されている基板と、所定の最小線幅に対して1/2以下の最小線幅を有し、前記金属層に形成される第1空間と、前記第1空間と異なる高さに前記1/2以下の最小線幅を有し、前記金属層に形成される第2空間と、を含む。前記第2空間は、前記第1空間から前記1/2以下の最小線幅の距離を置いて形成されていると好適である。

(もっと読む)

薄膜トランジスタの製造方法

【課題】フォトリソ工程を簡便に削減できるパター形成方法を考案し、液晶表示装置の製造工程を大幅に削減できるTFTの新しい製造方法を提供する。

【解決手段】TFTを構成する材料膜を絶縁膜基板上に積層して成膜してから、膜厚が互いに異なる複数の領域を有するレジストマスクを上記材料膜の最上層にパターニングして形成する。そして、このレジストマスクを用いたリフトオフの方法で導電体膜のパターン形成を行う。あるいは、別に形成した膜厚が互いに異なる複数の領域を有するレジストマスクをエッチングマスクにして積層した材料膜のうち複数の材料膜を順次に加工する。このような新規なパターン形成方法および加工方法により、従来の技術で5回のフォトリソ工程で製造していた液晶表示装置を2回あるいは3回のフォトリソ工程で製造する。

(もっと読む)

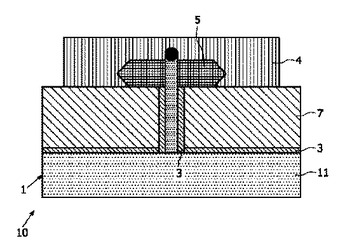

半導体デバイスを製造する方法及びそのような方法で得られる半導体デバイス

本発明は、少なくとも1つの半導体素子を備える半導体本体(1)を備える半導体デバイス(10)を製造する方法に関し、半導体本体(1)の上には、メサ形状半導体領域(2)が形成され、マスキング層(3)が、メサ形状半導体領域(2)の上に蒸着され、その頂部でメサ形状半導体領域(2)の側面と境界を接するマスキング層(3)の一部(3A)が取り除かれ、導電性接続領域(4)が、結果として得られる構造の上に形成され、メサ形状半導体領域(2)のための接点を形成する。本発明によれば、マスキング層(3)の部分(3A)の除去後、導電性接続領域(4)の形成前に、メサ形状半導体領域(2)が、マスキング層(3)の部分(3A)の除去によって自由にされるメサ形状半導体領域(2)の側面で追加的半導体領域(5)によって広げられる。このようにして、極めて低い接触抵抗を有するデバイス(10)が簡単な方法で得られる。好ましくは、メサ形状半導体領域(2)は、VLSのようなさらなるエピタキシアル成長プロセスによってナノワイヤによって形成される。追加的領域(5)は、例えば、MOVPEによって得られ得る。

(もっと読む)

(もっと読む)

配線形成方法

【課題】簡単なプロセスで平坦性に優れた配線を得ることができる配線形成方法を提供する。

【解決手段】基体110の表面の凹部113内に埋め込まれた配線114を形成する配線形成方法であって、(A)基体110の表面に、開口部112を備えたマスク材料層111を形成し、(B)マスク材料層111における開口部112の底部に位置する基体110をエッチングすることにより、基体110にマスク材料層111に対してアンダーカット形状の凹部113を形成し、その後、(C)マスク材料層111の開口部112内を含む全面に、配線材料層114をスパッタリング法により形成し、その後、(D)マスク材料層111及びマスク材料層111上の配線材料層114を基体110から除去し、凹部113内に配線材料層114を残し、以て、配線を得る工程を具備する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】トレンチ構造のトランジスタの形状及び電極構造に関して自由に設計を行なうことができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】シリコン基板10の表面には複数の凹部10a,10a,…が設けられ、各凹部10aには、表面からエミッタ領域REとベース領域RBとがこの順序で配置されている。その他の領域がコレクタ領域RCとなってトランジスタを構成する。基板全面に電極としての導電体を設ける場合、凹部10aによる段差のため、ベース領域RB上のベース電極12Bとエミッタ領域RE上のエミッタ電極12Eとは分離された状態で形成される。そして、エミッタ電極12E及びベース電極12Bを被覆する層間絶縁膜13を形成し、層間絶縁膜13を介してエミッタ電極12E及びベース電極12Bとそれぞれコンタクトを取るためのボンディングパッド14E及び14Bをデバイスの上層に形成する。

(もっと読む)

熱処理方法および熱処理装置

【課題】 低誘電率層間絶縁膜および/または金属膜の酸化を確実に抑止することが可能であり、しかも、プロセスの再現性に優れた熱処理方法を提供する。

【解決手段】 熱処理方法は、low−k膜および配線層が成膜されたウエハWを熱処理炉41内に収容する工程と、熱処理炉41内に、気相の無水酢酸をマスフローコントローラ44dによって流量調整しながら供給する工程と、気相の無水酢酸が供給された熱処理炉41内のウエハWを、熱処理炉41に設けられたヒーター41bによって加熱する工程とを含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】シェアードコンタクトホールの中に位置するサイドウォールがエッチングされてリーク電流が増加することを抑制できる半導体装置の製造方法を提供する。

【解決手段】第2のトランジスタのシリコン窒化膜からなるサイドウォール5b上に、シリコン酸化膜から構成される第1のエッチングストッパー膜8を形成する。第1及び第2のトランジスタ上並びに第1のエッチングストッパー膜8上に、シリコン窒化膜から構成される第2のエッチングストッパー膜9を形成する。第2のエッチングストッパー膜9上に、シリコン酸化膜から構成される層間絶縁膜10を形成し、層間絶縁膜10上に、レジストパターン50を形成する。レジストパターン50をマスクとして層間絶縁膜10、第2のエッチングストッパー膜9、及び第1のエッチングストッパー膜8をエッチングすることにより、ノーマルコンタクトホール10a及びシェアードコンタクトホール10bを形成する。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】コンタクトホールのサイズの安定した減少を実現でき、素子の信頼性を向上させるフラッシュメモリ素子の製造方法を提供する。

【解決手段】半導体基板101上に層間絶縁膜105とハードマスク膜パターン106aを形成し、それらの表面を覆うようにしてスペーサ膜109を形成する。第1のエッチング工程で層間絶縁膜105にコンタクトホール(図4中の符号200)を形成し、スペーサ膜109も第1のエッチング工程にて除去し、ハードマスク膜パターン106aを除去するための第2のエッチング工程を実施する。それにより、コンタクトホールのサイズを減少させる必要がある場合、あるいは隣り合うコンタクトホールどうしの間隔スペースを減少させる必要がある工程にあって、リソグラフィ工程の限界を克服しつつ、コンタクトホールのサイズを安定して減少させ、ブリッジの発生を抑えて素子の信頼性を高める。

(もっと読む)

半導体装置およびその製造方法

【課題】ホール内の導電層に空隙を生じさせないように構成することで導電層の高抵抗化を抑制できるようにする。

【解決手段】コンタクトホール7内において、第3の導電層16が第2の導電層15の内側に形成されている。したがって、第2の導電層15がコンタクトホール7の内面に沿って形成されその内側に空隙が存在するようなことがあってもこの空隙を埋込むことができ、第2および第3の導電層15および16の高抵抗化を抑制することができ、第2および第3の導電層15および16の抵抗値の低減化を図ることができる。

(もっと読む)

半導体装置の製造方法

【課題】従来の製造方法においては、オーバーエッチングによりコンタクト底部の表面荒れが引き起こされ、それにより半導体装置の特性ばらつきが増大してしまう。

【解決手段】P型シリコン基板1に形成されたトレンチの底部に設けられたコレクタ領域4を有するバイポーラトランジスタを形成する。P型シリコン基板1上に層間絶縁膜23を形成する。トレンチの上部の層間絶縁膜23を途中までエッチングすることにより、コレクタコンタクト用開口の一部30を形成する。トレンチの上部の層間絶縁膜23を上記底部に達するまでエッチングすることにより、コレクタコンタクト用開口の残りの部分32を形成する。コレクタコンタクト用開口の残りの部分32の形成は、エミッタコンタクト用開口25およびベースコンタクト用開口27の形成と同時に実行される。

(もっと読む)

コンタクトホール形成方法

【課題】すり鉢状のコンタクトホールを容易に形成する。

【解決手段】半導体基板11上に金属膜12を形成し、金属膜12上にSiO2膜13を形成し、SiO2膜13上に第1のレジスト膜14を形成し、レジスト膜14上に第2のレジスト膜15を形成し、レジスト膜15にコンタクトホール形成用の開口部16を形成し、レジスト膜14のみを感光させる露光用光源を用いてレジスト膜14に開口部16よりも大きい開口部17を形成し、レジスト膜14、15をマスクにして、CF4、C2F6などのエッチングガスを用いた反応性イオンエッチングによりSiO2膜13を選択的に除去して、コンタクトホール19を形成する。

(もっと読む)

互いに接続されたシールド電極及びゲート電極を有するシールドゲートトレンチFETの構造及びこれを形成する方法

電界効果トランジスタ(FET)は、半導体領域に延在する複数のトレンチを含んでいる。各トレンチはゲート電極及びシールド電極を含み、当該ゲート電極と当該シールド電極との間に電極間誘電体が設けられ、シールド電極及びゲート電極は互いに電気的に接続される。  (もっと読む)

(もっと読む)

低接触抵抗CMOS回路およびその製造方法

低接触抵抗CMOS集積回路(50)とその製造方法が提供される。CMOS集積回路(50)は、N型の回路領域(72、74)に電気的に結合された第1遷移金属(102)と、P型の回路領域(76、78)に電気的に結合され、第1遷移金属とは異なる第2遷移金属(98)と、を含む。導電性バリア層(104)は第1遷移金属の各々の上に重なり、第2遷移金属およびプラグ金属(110)は導電性バリア層の上に重なる。  (もっと読む)

(もっと読む)

半導体装置、電気光学装置、電子機器及び半導体装置の製造方法

【課題】使用するアクティブマトリクス方式の表示器に使用される有機半導体装置においてゲート駆動信号を伝搬するゲート線(ゲート信号線)の抵抗値を下げることを可能とした半導体装置、電気光学置及び電子機器を提供する。

【解決手段】基板上(101)に形成された有機半導体トランジスタと、有機半導体トランジスタのソース又はドレイン電極(105)と接続されるデータ線(107)と、データ線と交差するように配置されて有機半導体トランジスタのゲート電極(110)に接続されるゲート線と、を備え、ゲート線は、ゲート電極(110a)、ゲート電極に信号を伝搬する第1のゲート線(102)、及びデータ線と層間絶縁層(109)を介して交差する第2のゲート線(110b)を含み、上記ゲート電極、上記第1及び第2のゲート線は互いに直列に接続され、第1のゲート線(102)の導電率がゲート電極(110a)及び第2のゲート線(110b)の導電率よりも高い、ことを特徴とする。

(もっと読む)

161 - 180 / 246

[ Back to top ]