Fターム[4M104DD07]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は絶縁膜の除去方法 (1,213)

Fターム[4M104DD07]の下位に属するFターム

ドライエッチ (710)

ウェットエッチ (218)

ドライ、ウェットの併用 (39)

Fターム[4M104DD07]に分類される特許

81 - 100 / 246

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体層と、酸化物半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層との順で積層されたゲート電極を含むゲート配線と、酸化物半導体層と、前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、酸化物半導体層と電気的に接続され、第3の導電層と第4の導電層との順で積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】積層構造のゲート電極をもつ薄膜トランジスタにおいて、ゲート電極上の絶縁層のステップカバレージの低下を防止し、かつ、前記第1金属層のヒロック(hillock)の生成を防止する。

【解決手段】基板上に第1金属層43と第2金属層45を連続して蒸着し、さらに所定幅(W1)を持つ感光膜47を形成する(図5(a))。感光膜47をマスクとして第2金属層45を等方性のウェットエッチング方法で感光膜の幅(W1)よりも1μm乃至4μm程度小さな幅(W2)にパターニングする(図5(b))。次に、感光膜47をマスクとして第1金属層43を異方性エッチング方法で幅(W1)を持つようにパターニングして積層構造のゲート電極を形成する(図5(c))。1μm<W1−W2<4μmの関係にあればステップカバレージの低下とヒロックの両方を防止できる。

(もっと読む)

半導体装置

【課題】熱的安定性がある一方、密着性が悪くならない程度の仕事関数を有する金属膜または金属化合物よりなる膜をゲート電極として使用した場合に、しきい値電圧を低く抑制できる半導体装置を提供する。

【解決手段】n型MIS素子とp型MIS素子を備えるCMIS素子において、n型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上にケイ窒化タンタル膜よりなるゲート電極10を形成する。一方、p型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上に、酸化アルミニウム膜よりなるしきい値調整膜7を形成する。そして、このしきい値調整膜7上に、ケイ窒化タンタル膜よりなるゲート電極11を形成する。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備え、占有面積が小さい保護回路等が必要となる。

【解決手段】ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と端部が重畳する第1配線層及び第2配線層と、少なくともゲート電極と重畳しゲート絶縁膜及び該第1配線層及び該第2配線層における導電層の側面部及び上面部と接する酸化物半導体層とを有する非線形素子を用いて保護回路を構成する。非線形素子のゲート電極は走査線又は信号線と接続され、非線形素子の第1配線層又は第2配線層がゲート電極の電位が印加されるようにゲート電極層と直接接続されていることで、接続抵抗の低減による安定動作と接続部分の占有面積を縮小する。

(もっと読む)

表示装置及びその製造方法

【課題】CVD装置への出し入れ回数を減らした表示装置の製造方法および表示装置を提供すること。

【解決手段】本発明にかかる表示装置の製造方法は、絶縁基板上に第1の電極膜と第2の電極膜とを含む導電層、第1の絶縁層、半導体膜、第2の絶縁層および保護層を形成する工程と、半導体膜の上方の第1の領域に配置される所定の厚さの第1のレジスト膜と、第2の電極膜の上方の第2の領域に配置される開口部と、それら以外の領域に配置される厚い第2のレジスト膜と、を保護層上に形成する工程と、第2の領域下をエッチングする工程と、第1のレジスト膜をアッシングにより除去する工程と、第1の領域下に半導体膜に達する第1の孔を形成し、かつ第2の領域下に第2の電極膜に達する第2の孔を形成する工程と、第2のレジスト膜を除去する工程と、半導体膜および第2の電極膜と接続される配線を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域に高抵抗不純物領域(HRD

または低濃度不純物領域)を自己整合的に形成する方法を提供する。

【解決手段】ゲイト電極105上面にマスク106を残し、比較的低い電圧でポーラスな

第1の陽極酸化膜107をゲイト電極の側面に成長させる。この陽極酸化膜をマスクとし

てゲイト絶縁膜104’をエッチングする。必要に応じては比較的高い電圧でバリア型の

第2の陽極酸化膜108をゲイト電極の側面および上面に形成する。第1の陽極酸化膜を

選択的にエッチングする。不純物ドーピングをおこなうと、ゲイト電極の下部にはドーピ

ングされず、ゲイト電極に近い領域では、不純物濃度の低い高抵抗領域111,112と

なる。ゲイト電極から遠い領域では、不純物濃度の高い低抵抗領域110,113となる

。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の使用時において熱による反りを抑制し、半導体装置の信頼性を向上させる。

【解決手段】縦型MOSトランジスタを構成する半導体基板10の表面上に、ソース領域と接続したソースパッド電極18が形成されている。ソースパッド電極18には、メッキ法により形成された表面電極23が形成されている。表面電極23にはバンプ電極31が接続されており、表面電極23は、バンプ電極31を露出する保護膜26に覆われている。一方、半導体基板10の裏面上には、ドレイン領域と接続した裏面電極30が形成されている。表面電極23と裏面電極30は、同じ線膨張係数を有した金属、好ましくは銅からなる。また、表面電極23と裏面電極30は、好ましくは同じ厚さ、あるいは略同じ厚さを有している。

(もっと読む)

半導体装置の作製方法

【課題】ガラス基板を使用したSOI基板上に形成しても、ゲート電極を形成する導電膜を成膜する際に該導電膜の加える応力により、ガラス基板上の絶縁膜及び半導体膜がはがれないような半導体装置の作製方法の提供を課題の一つとする。

【解決手段】ボンド基板上に第1の絶縁膜を形成し、ボンド基板の表面からイオンを添加することによって脆化層を形成し、ボンド基板を、第1の絶縁膜を介してガラス基板と貼り合わせ、ボンド基板を脆化層において分離してガラス基板上に第1の絶縁膜を介して半導体膜を形成し、第1の絶縁膜及び半導体膜の周辺領域を除去してガラス基板の一部を露出させ、半導体膜、第1の絶縁膜及びガラス基板上に接してゲート絶縁膜を形成し、ゲート絶縁膜上に接して2層構造の積層導電膜を形成し、2層構造の積層導電膜として、上層に引っ張り応力を有する導電膜、下層に圧縮応力を有する導電膜を用いて半導体装置を作製する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチゲート形成において、ペアスペースパターンの位置ずれの生じないパターン形成方法を提供する。

【解決手段】被加工層1上に、第3〜第1マスク層13,12,11を順次積層する。第1マスク層上に第4マスク層を形成し、第4マスク層をマスクにして第1マスク層をラインパターン形状に成形する。第1マスク層のライン幅方向両側に、サイドウオール層21aを形成してから第1マスク層を除去する。一対のサイドウオール層をマスクにして第2マスク層を一対のラインパターン形状に成形する。第3マスク層上に第5マスク層を形成し、第5マスク層をマスクにして一対の開口部を第3マスク層に設ける。第3マスク層をマスクにして被加工層に一対の溝部を設ける。

(もっと読む)

基板処理方法

【課題】半導体デバイスの小型化要求を満たす寸法の開口部を形成する基板処理方法において、マスク層の厚さを増大させることができる基板処理方法を提供する。

【解決手段】SiN膜51、BARC膜52及びフォトレジスト膜53が順に積層され、フォトレジスト膜53はBARC膜52の一部を露出させる開口部54を有するウエハWを処理する基板処理方法であって、デポ性ガスであるCH3FガスとSF6ガスの混合ガスから生成されたプラズマによって開口部54を有するフォトレジスト膜53の上部表面にデポを堆積して厚さを増大させるマスク層厚さ増大ステップを有する。

(もっと読む)

半導体装置の製造方法

【課題】接合リーク電流の低減が図られる半導体装置の製造方法を提供する。

【解決手段】半導体基板1に所定の深さのトレンチが形成され、そのトレンチ5内に分離酸化膜6が形成される。不純物イオンを注入することにより、分離酸化膜6の表面に、分離酸化膜6のエッチング特性とは異なるエッチング特性を有する改質層7が形成される。半導体基板の領域に、トランジスタ等の所定の半導体素子が形成される。半導体基板1上に、エッチングストッパ膜10および層間絶縁膜16が形成される。その層間絶縁膜16およびエッチングストッパ膜に、金属シリサイド9の表面を露出するコンタクトホール16a,16bが形成される。コンタクトホール16a,16b内にプラグ18a,18bが形成される。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】

基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】セルフアラインコンタクトを形成する際に、エクステンション領域及びソースドレイン領域におけるシリサイド化されていない部分とコンタクトとが接触することがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、ゲート電極13の側壁の上から半導体基板11の上に亘って形成されたL字サイドウォール14と、層間絶縁膜22と、L字サイドウォール14に覆われたエクステンション領域16と、一部がL字サイドウォール14に覆われたソースドレイン領域15と、ソースドレイン領域15におけるL字サイドウォール14に覆われていない部分に形成されたシリサイド層17と、シリサイド層17と接続されたコンタクト17とを備えている。L字サイドウォール14は、層間絶縁膜22と比べてエッチングレートが小さい絶縁材料により形成されている。

(もっと読む)

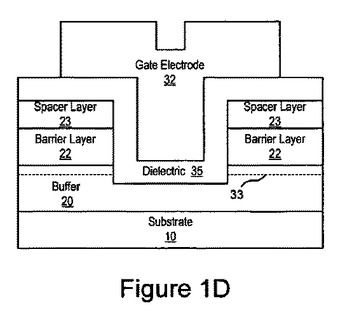

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

半導体装置、及びその製造方法

【課題】トランジスタ特性を劣化させずに形成される小型の半導体装置、及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成されるゲート絶縁膜と、前記半導体基板上に前記ゲート絶縁膜を介して形成されるゲート電極と、前記ゲート電極の上面に形成される第1窒化シリコン膜と、前記ゲート電極の側面に形成される保護絶縁膜と、前記保護絶縁膜の側面に形成される第2窒化シリコン膜と、前記保護絶縁膜の上面に形成され、その底面が前記第1窒化シリコン膜の底面よりも上部に形成される第3窒化シリコン膜とを備える。

(もっと読む)

液晶表示装置用アレイ基板製造用のエッチングテープ

【課題】本発明は液晶表示装置用アレイ基板製造用のエッチングテープを提供する。

【解決手段】本発明のエッチングテープは、ベースシート及びベースシート上にゲルタイプのエッチング物質が塗布されて形成されたエッチング物質層を含む。このエッチングテープは、透明絶縁基板上にゲート電極、ストレージキャパシターの第1電極、ゲート配線を形成する段階、ゲート絶縁膜、アクティブ層、オーミック接触層、ソース電極及びドレーン電極を形成し、誘電体層及びストレージキャパシターの第2電極を形成し、データ配線を形成する段階、画素電極を形成し、ゲートパッド電極を形成し、データパッド電極を形成する段階、保護層を形成する段階及びゲートパッド電極上に形成された保護層とデータパッド電極上に形成された保護層をエッチングすることでコンタクトホールを形成する段階を含む液晶表示装置用アレイ基板の製造方法に利用される。

(もっと読む)

半導体装置とその製造方法

【課題】SRAMを備えた半導体装置とその製造方法において、当該SRAMの占有面積を低減すること。

【解決手段】SRAMが形成された第1の領域Iとそれ以外の第2の領域IIとを有するシリコン基板10と、第1の領域Iに形成され、第1のゲート電極19aを備えたSRAMの第1のトランジスタTRn1と、第2の領域IIに形成され、第2のゲート電極19bを備えた第2のトランジスタTRn0とを有し、第1のゲート電極19aの高さが、第2のゲート電極19bの高さよりも低い半導体装置による。

(もっと読む)

薄膜トランジスタ及びその製造方法、ならびに薄膜トランジスタを備えた平板表示装置

【課題】酸化物半導体を活性層とする薄膜トランジスタ及びその製造方法、ならびに薄膜トランジスタを備えた平板表示装置を提供する。

【解決手段】基板上に形成され、チャネル領域、ソース領域及びドレイン領域を提供する酸化物半導体層と、ゲート絶縁層により酸化物半導体層から絶縁されたゲート電極と、酸化物半導体層のソース領域及びドレイン領域上に形成されたオーム接触層と、オーム接触層を介してソース領域及びドレイン領域に接続されたソース電極及びドレイン電極とを含み、オーム接触層は、ソース電極及びドレイン電極よりも仕事関数の低い金属で形成されている。

(もっと読む)

半導体装置の製造方法

【課題】リソグラフィの露光解像限界を超えた寸法を有するパターンの形成において、工程数の削減が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板上に形成された被加工膜上に第1のマスク材膜を形成し、前記第1のマスク材膜上にレジストパターンを形成し、前記レジストパターンを覆うように前記第1のマスク材膜上に所定の膜厚の第2のマスク材膜を形成し、前記第2のマスク材膜をエッチバックして前記レジストパターン及び前記第1のマスク材膜を露出させ、エッチバックされた前記第2のマスク材膜を残したまま、露出した前記レジストパターン及び前記第1のマスク材膜を同時に加工し、前記第1のマスク材膜下に露出する前記被加工膜部を加工する。

(もっと読む)

81 - 100 / 246

[ Back to top ]