Fターム[4M104DD07]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は絶縁膜の除去方法 (1,213)

Fターム[4M104DD07]の下位に属するFターム

ドライエッチ (710)

ウェットエッチ (218)

ドライ、ウェットの併用 (39)

Fターム[4M104DD07]に分類される特許

21 - 40 / 246

半導体装置およびその作製方法

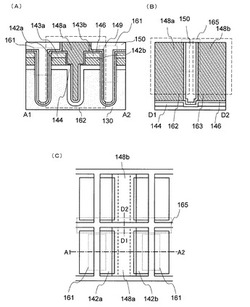

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

半導体装置の製造方法

【課題】耐圧が数ボルトから数十ボルト程度のショットキダイオード等のガラス封止型のダイオードにおいては、半田の融点よりもずっと高い封止処理温度が適用されるため、通常、バンプ電極材料としては、銀等の比較的融点の高い金属材料が使用される。しかし、バンプ電極の厚さは、パッシベーション膜や表面電極膜の厚さと比較して、著しく厚いので、バンプ電極とチップ上面の連結部外周部、すなわち、バンプ電極内側外壁には、応力が集中しやすく、この応力により、パッシベーション膜にクラックが発生することがある。

【解決手段】本願発明は、ダイオード等のガラス封止型半導体装置の製造方法において、表面メタル電極の外周とバンプ電極の内側外壁の位置を相互に相違した位置に設定するものである。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造工程の煩雑化および製造プロセスの長時間化を抑制できると共に、量産性に優れた半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法では、ゲート電極7上に、積層膜19を形成する。そして、層間絶縁膜8形成後、層間絶縁膜8等に対してエッチング処理を施す。これにより、ソース領域3およびp+ベースコンタクト領域5が底面から露出した第1のコンタクトホール12を形成すると同時に、積層膜19が底面から露出した第2のコンタクトホール13を形成する。ここで、当該エッチング処理は、積層膜19のエッチングレートが層間絶縁膜8のエッチングレートよりも遅くなるエッチング条件により、実施する。

(もっと読む)

半導体上からホットメルトエッチングレジストを剥離する改良された方法

【課題】シート抵抗率の増大およびアルミニウム電極の腐蝕を抑制する剥離剤配合物を提供する。

【解決手段】ホットメルトエッチングレジストが、半導体ウェハ上の反射防止コーティングもしくは選択的エミッタに選択的に適用される。無機酸含有エッチング剤を用いて、反射防止コーティングおよび選択的エミッタの露出部分がエッチング除去されて、半導体基体を露出させる。このホットメルトエッチングレジストは次いで、半導体の電気的一体性を悪化させないアルカリ剥離剤を用いて半導体から剥離される。次いで、露出した半導体は金属化されて、電流トラックを形成する。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域とコンタクトプラグの接続部分の電気抵抗が低減され、かつ短チャネル効果の発生が抑えられたトランジスタを有する、n型およびp型トランジスタを含む半導体装置、およびその半導体装置の製造方法を提供すること。

【解決手段】不純物高濃度領域を有する半導体装置を提供する。前記不純物高濃度領域は、第1のソース・ドレイン領域内の前記第1のソース・ドレイン領域と前記第1のコンタクトプラグとの界面近傍に形成される。前記不純物高濃度領域の前記第1のコンタクトプラグの底面の長手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅の少なくとも一方は、前記第1のコンタクトプラグの前記底面の短手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホールの形状制御が容易な半導体装置の製造方法を得る。

【解決手段】実施形態の半導体装置の製造方法は、基板1上にゲート絶縁膜2、ゲート電極3,4、第1ハードマスク5を形成し、第1ハードマスクをパターンニングして第1マスクを形成し、これをマスクにゲート電極及びゲート絶縁膜を基板が露出するまでエッチングしラインパターンを形成し、露出した基板及び第1マスクを覆うようにライナー膜7を形成する。更にライナー膜に覆われたラインパターンの間隙を有機系絶縁膜で埋め込み、少なくともライナー膜が露出するまで有機系絶縁膜を平坦化してその上に第2ハードマスク9を形成し、第2ハードマスクを第1マスクと交差するようにパターンニングして第2マスクを形成し、第1及び第2マスクをマスクに有機系絶縁膜をライナー膜が露出するまでエッチングしてコンタクトホールを形成する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電界効果移動度が大きい酸化物半導体層を用いた半導体装置の作製方法を提供することを課題の一つとする。また、高速動作可能な半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化物半導体層をハロゲン元素により終端化させて、酸化物半導体層と、酸化物半導体層と接する導電層のコンタクト抵抗の増大を抑制することで、酸化物半導体層と導電層のコンタクト抵抗が良好になり、電界効果移動度が高いトランジスタを作製することができる。

(もっと読む)

トップゲート型薄膜トランジスタ及びこれを備えた表示装置

【課題】酸化物半導体層のチャネル領域の、水素拡散による低抵抗化を抑制するトップゲート型酸化物半導体TFT及びこれを備えた表示装置を提供する。

【解決手段】基板の上に、ソース電極層と、ドレイン電極層と、酸化物半導体層と、ゲート絶縁層と、In、Ga、Zn、Snの少なくとも1種類の元素を含むアモルファス酸化物半導体からなるゲート電極層と、水素を含む保護層と、を有し、ゲート絶縁層は酸化物半導体層のチャネル領域の上に形成され、ゲート電極層はゲート絶縁層の上に形成され、保護層はゲート電極層の上に形成されていることを特徴とするトップゲート型薄膜トランジスタ。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート−ソース間の容量低減及びソース抵抗を低減させ、且つ耐圧向上、高出力化及び高周波化を、容易且つ確実に可能とする量産化に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極19を形成する際に、4層の電子線レジスト11〜14を用いてゲート開口17を形成し、ゲート開口17内に、キャップ層5の表面との接触面を含む幹状の下方部分19aと下方部分19aから傘状に拡がる上方部分19bとが一体形成されてなり、下方部分19aの接触面がドレイン電極7に比べてソース電極6に偏倚した位置に設けられており、上方部分19bの傘状の下端面のうちソース電極6側の部位がドレイン電極7側の部位よりもキャップ層5の表面からの高さが高いゲート電極19を形成する。

(もっと読む)

半導体装置

【課題】2DEGをチャンネルとして用いる半導体装置において、不純物イオンの侵入による悪影響を排除する。

【解決手段】第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層11側に、2次元電子ガス(2DEG)層13が形成される。ソース電極14からドレイン電極15の間の2DEG層13が形成された領域がこの半導体装置10におけるチャンネル領域となる。このチャンネル領域上の絶縁層17上において、第1のフィールドプレート18が形成されている。すなわち、第1のフィールドプレート18は、2つの主電極のうちの一方から他方に達するチャンネル領域上を覆うように形成されている。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、疎水化処理を要することなく、フォトリソグラフィー技術による酸化シリコン膜のパターニングが可能な半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明は、基板上に形成された酸化シリコン膜上に機能層を形成する機能層形成工程と、上記機能層上に第1フォトレジストを塗布し、フォトリソグラフィー法により上記機能層および上記酸化シリコン膜をパターニングし、上記第1フォトレジストを除去する第1パターニング工程と、パターニングされた上記機能層上に第2フォトレジストを塗布し、フォトリソグラフィー法により上記機能層をさらにパターニングし、上記第2フォトレジストを除去する第2パターニング工程とを有し、上記機能層と上記第1フォトレジストおよび上記第2フォトレジストとの接触角が20度以下であることを特徴とする半導体素子の製造方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】pチャネル型の電界効果トランジスタのしきい値電圧を確実に制御して所望の特性が得られる半導体装置と、その製造方法とを提供する。

【解決手段】温度約700〜900℃のもとで施す熱処理に伴い、素子形成領域RPでは、アルミニウム(Al)膜7a中のアルミニウム(Al)がハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)が添加される。また、チタンアルミニウムナイトライド(TiAlN)膜からなるハードマスク8a中のアルミニウム(Al)とチタン(Ti)とがハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)とチタン(Ti)とが添加される。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

整流器ブリッジ回路

【課題】本発明の課題は、ロードダンプの場合、すなわち負荷の遮断の急に行われる場合にも、ロードダンプエネルギが全てのダイオードに均等に分配される整流器ブリッジ回路を提供することである。

【解決手段】前記課題は、請求項1に従う整流器ブリッジ回路によって解決される。

(もっと読む)

整流器ブリッジ回路

【課題】本発明の課題は、ロードダンプ時の動作において、すなわち負荷の遮断が急に行われる場合であっても適切な整流器ブリッジ回路を提供することである。

【解決手段】前記課題は、請求項1に従う回路によって解決される。

(もっと読む)

21 - 40 / 246

[ Back to top ]