Fターム[4M104DD49]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | 選択成長 (331) | 成長速度の制御 (13)

Fターム[4M104DD49]に分類される特許

1 - 13 / 13

シリコン膜の形成方法及び半導体装置の製造方法

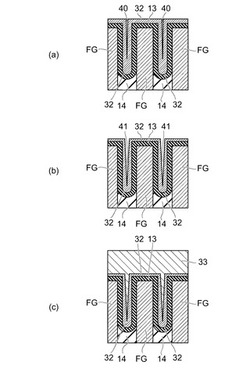

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

Ni膜の形成方法

【課題】 成膜温度、成膜圧力、還元ガスの使用量・使用割合等の成膜条件を設定することにより、所望の物性を有する利用範囲の広いNi膜の形成方法を提供すること。

【解決手段】 真空槽の中でSi基板を一定温度に保持してニッケルアルキルアミジナート(但し、アルキルは、メチル基、エチル基、ブチル基及びプロピル基から選ばれる。)とH2とNH3とをこの真空槽内に導入し、CVD法でNi膜を形成する方法であって、成膜温度が280℃より高く350℃以下であること。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備える。

(もっと読む)

電子デバイスの製造方法

【課題】カーボン膜の抵抗率を低減することができる電子デバイスの製造方法を提供する。

【解決手段】基板11が載置されたチャンバ4内に炭素を含有する原料ガスを供給する。基板11の周囲からチャンバ4内のアノード1に向けて電子を放出させてチャンバ4内にプラズマ14を発生させ、基板11上にグラファイト、グラフェン等のカーボン膜を形成する。

(もっと読む)

成膜装置、成膜方法及び記憶媒体

【課題】真空容器内にて反応ガスによりチタンナイトライド膜を形成するにあたり、当該チタンナイトライド膜を速やかに成膜すると共に、表面形状が平滑なチタンナイトライド膜を得ること。

【解決手段】チタンナイトライド膜の成膜処理を行う時に、回転テーブル2と各ガスノズル31、32、41、42とを100rpm以上で相対的に回転させることによって、反応ガスの供給サイクル(反応生成物の成膜サイクル)を高速で行うことができるので、薄膜を速やかに形成することができ、またサイクル間の時間が極めて短いので、基板の表面に生成した反応生成物の結晶化による粒子径の粗大化が進行する前に次の反応生成物の層を上層側に積層して平滑な表面を得ることができる。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

半導体装置の製造方法、基板処理装置及び半導体装置

【課題】 緻密で原料起因の不純物濃度が低く抵抗率が低い導電性膜を、速い成膜速度で形成する半導体装置の製造方法および基板処理装置を提供することである。

【解決手段】 2種類以上の原料を処理室内に同時に供給し、処理室内に載置された基板上に膜を形成する半導体装置の製造方法であって、少なくとも1種の原料を第1の供給量で処理室内に供給する第1の原料供給工程と、この少なくとも1種の原料を第1の供給量とは異なる第2の供給量で処理室内に供給する第2の原料供給工程と、を有する。

(もっと読む)

成膜方法

【課題】結晶粒径が均一な金属シリサイド膜、特にチタンシリサイド膜を形成することができる成膜方法を提供すること。

【解決手段】被処理体1のSi含有部分上の自然酸化膜を除去する工程と、被処理体1の自然酸化膜が除去されたSi含有部分上に金属シリサイド膜4を形成する工程とを具備し、金属シリサイド膜4を形成する工程は、最初にプラズマを生成せずに、成膜しようとする金属シリサイド中の金属を含有する金属含有原料ガスを所定時間供給して金属−シリコン結合を生じさせ(ii)、次いで金属含有原料ガスを供給しつつプラズマを生成して当該金属からなる金属膜を成膜し、その際の金属膜とSi含有部分との反応により金属シリサイド膜を形成する(iii)。

(もっと読む)

処理装置

【課題】 真空ポンプを備えた真空排気系内で故障の原因となる不要な膜が生成されることを防止することが可能な処理装置を提供する。

【解決手段】処理装置において、被処理体を収容する処理容器22と、処理容器内へ原料ガスを供給する原料ガス供給系50と、処理容器内へ反応性ガスを供給する反応性ガス供給系52と、真空ポンプ44、46を有する真空排気系36と、処理容器を迂回させるために原料ガス供給系と真空排気系とを連通す原料ガスバイパス系62と、処理容器を迂回させるために反応性ガス供給系と真空排気系とを連通する反応性ガスバイパス系66と、原料ガスバイパス系内に介設されて原料ガスの流出を防止する原料ガス流出防止開閉弁X1と、反応性ガスバイパス系内に介設されて反応性ガスの流出を防止する反応性ガス流出防止開閉弁Y1とを備え、真空排気系内に原料ガスと反応性ガスとが同時に流れ込まないようにする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造技術において、同一基板上に金属シリサイド膜厚の異なる領域を作り分ける。

【解決手段】シリコン基板1の主面f1の第1領域R1に第1トランジスタQ1を、同第2領域R2に第2トランジスタQ2を形成する。その後、主面f1に保護酸化膜PT1を形成し、第1ドライエッチングDE1を施すことで、第1領域R1および第2領域R2を覆う保護酸化膜PT1を除去する。その後、第1ドライエッチングDE1よりも低い高周波パワーで、かつ、炭素、水素およびフッ素の化合物を含まないガスを用いた第2ドライエッチングDE2を、第2領域R2に対して施す。その後、シリコン基板1の主面f1上に金属膜M1を堆積し、熱処理を施すことで、金属シリサイド膜scを形成する。

(もっと読む)

半導体素子及びその形成方法、半導体クラスタ装備

【課題】電気的な特性が向上される半導体素子の形成方法を提供する。

【解決手段】この方法は、導電パターン105を有する半導体基板100の上に絶縁膜110を形成する。絶縁膜をパターニングして導電パターンの一部を露出する開口部115を形成し、開口部の内壁及び絶縁膜の上部面に予備拡散防止膜120を形成する。予備拡散防止膜に酸素原子等を供給して第1拡散防止膜120aを形成する。第1拡散防止膜により囲まれている開口部を埋める金属膜152を形成する。この方法により製造された半導体素子及び半導体素子の製造に利用する半導体クラスタ装備を提供する。

(もっと読む)

深トレンチのドープシリコン充填のプロセスシーケンス

膜堆積がトレンチの底部から上に向かって生じるようなシラン比に対する温度、圧力およびドーパントで第1の充填が実施される、深トレンチ構造のイン・シトゥー・ドープアモルファスシリコンによるボイドフリー充填方法が提供される。この第1の充填によって、100%を超えるステップカバレージウェルが達成される。第2の充填ステップにおいて、堆積レートに対するドーパントの影響を低減するために変更された条件で堆積が実施されることによって、トレンチ充填が、第1の充填の堆積レートを超える堆積レートで完了される。深トレンチキャパシタ構造を形成するためのこの方法の用途において、中間ステップはさらに、アモルファスシリコン層によるボイドフリー充填トレンチのキャッピング、その後のウェーハの平坦化、およびドーパントを再分布させるための熱アニーリングを含む。 (もっと読む)

1 - 13 / 13

[ Back to top ]