Fターム[4M104DD95]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 2種類以上の電極の同時形成 (126) | 材料が異なる電極 (47)

Fターム[4M104DD95]の下位に属するFターム

オーミックとショットキー (33)

Fターム[4M104DD95]に分類される特許

1 - 14 / 14

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

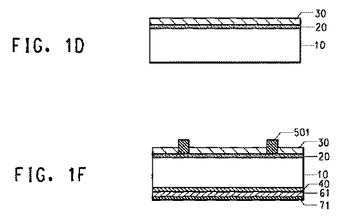

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

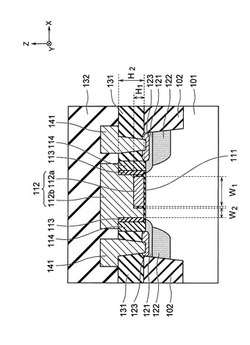

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

アルミニウムペーストおよびシリコン太陽電池の製造におけるその使用

粒子状アルミニウムと、亜鉛有機成分と、有機ビヒクルとを含むアルミニウムペースト、および、シリコン太陽電池のp型アルミニウム裏面電極の形成におけるその使用が開示される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル及びpチャネルのゲート構造が異なり且つメタルゲート電極を有する半導体装置において、ゲート電極パターン形成時のドライエッチングでゲート絶縁膜の突き抜けが発生しないようにする。

【解決手段】ゲート絶縁膜105と接する第2ゲート電極材料膜(TiN膜)111がゲート電極151の一部として形成されないnチャネル領域103上に、第2ゲート電極材料膜(TiN膜)111のエッチング時にオーバーエッチング吸収層として機能する第1ゲート電極材料膜(ポリシリコン膜)107を予め形成しておく。

(もっと読む)

半導体装置と半導体装置の製造方法

【課題】

オーバーエッチングを大きくしても、問題発生を抑制できる半導体装置及びその製造方法を提供する。

【解決手段】

半導体装置は、複数の活性領域にサイドウォール絶縁膜を備えたゲート電極を持つ電界効果トランジスタを有し、素子分離領域上にゲート電極と同一材料を用いて形成された配線を有し、素子分離領域上ではサイドウォール絶縁膜が選択的に除去され、ゲート電極のシリサイド層より厚いシリサイド層が形成される。nチャネル電界効果トランジスタを覆って引張応力絶縁膜を、pチャネル電界効果トランジスタを覆って圧縮応力絶縁膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETとpチャネル型MISFETで異なる金属膜を使用する場合であっても、両方のゲート電極を同時に加工できる技術を提供する。

【解決手段】pチャネル型MISFET形成領域に改質膜11を形成している。改質膜11は、ポリシリコン膜9にリンを導入することにより形成されている。この改質膜11は、ポリシリコン膜9よりもエッチング速度が速くなる性質がある。このことから、pチャネル型MISFET形成領域において、改質膜11とポリシリコン膜9をすべてエッチングする際、nチャネル型MISFET形成領域においては、ポリシリコン膜9がすべてエッチングされずに一部が残存する。これにより、pチャネル型MISFET形成領域に形成されている膜の総膜厚と、nチャネル型MISFET形成領域に形成されている膜の総膜厚の差が緩和される。

(もっと読む)

半導体装置及びその製造方法

【課題】コストを低減した半導体装置を提供する。

【解決手段】半導体基板100表面部にチャネル領域101を挟むように形成された拡散層102と、チャネル領域101上に形成されたゲート絶縁膜103を有し、N型MOSFETのゲート電極104は第1のニッケルシリサイド層104a及び第1のニッケルシリサイド層104a上に形成され第1のニッケルシリサイド層104aよりニッケル含有率が高い第2のニッケルシリサイド層104bからなり、P型MOSFETのゲート電極104は第2のニッケルシリサイド層104bよりニッケル含有率が高い第3のニッケルシリサイド層からなる。

(もっと読む)

デュアルメタルゲート構造の形成方法

半導体構造(10)の形成方法は、第1および第2ウェル領域(16、18)を含む半導体層上にチャネル領域層(40)を形成すること、チャネル領域層上に保護層(80)を形成すること、第1ウェル領域上に第1ゲート誘電体層(26)を形成すること、第1ゲート誘電体上に第1メタルゲート電極層(28)を形成すること、保護層を除去すること、チャネル領域層上に第2ゲート誘電体層(42)を形成すること、第2ゲート誘電体層上に第2メタルゲート電極層を形成すること、第1ウェル領域上に、第1ゲート誘電体層と第1メタルゲート電極層の各々の一部を含む第1ゲートスタック(58)を形成し、チャネル領域層上に、第2ゲート誘電体層と第2メタルゲート電極層の各々の一部を含む第2ゲートスタック(66)を形成することを含む。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置およびその製造方法は高誘電体をゲート絶縁膜として有し、かつ、適正な閾値電圧を有する。

【解決手段】半導体装置は、半導体基板101と、半導体基板上に設けられ、シリコン酸化膜よりも比誘電率の高い高誘電体から成るゲート絶縁膜108,109と、ゲート絶縁膜上に設けられたアルミニウム層を含むN型FET用の第1のゲート電極110aと、ゲート絶縁膜上に設けられ、NiXSiY(X>Y)から成るP型FET用の第2のゲート電極110bとを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易なNi−FUSI/SiONあるいはHigh−kゲート絶縁膜構造および低いしきい値電圧Vthを有するCMISを備えた半導体装置およびその製造方法を提供することを可能にする。

【解決手段】基板1中に互いに絶縁分離されたp型半導体領域2とn型半導体領域3を形成する工程と、p型およびn型半導体領域上に第1および第2ゲート絶縁膜5,15をそれぞれ形成する工程と、第1ゲート絶縁膜上にNi/Si<31/12となる組成の第1ニッケルシリサイド6bを形成するとともに第2ゲート絶縁膜上にNi/Si≧31/12となる組成の第2ニッケルシリサイド16を形成する工程と、第1ニッケルシリサイド中にアルミニウムを拡散させ、第1ニッケルシリサイドと第1ゲート絶縁膜との界面にアルミニウム6aを偏析させる工程と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】高性能かつ信頼性の高い金属ゲート電極部を有する半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に形成したゲート絶縁膜3上に金属ゲート電極層4が形成され、金属ゲート電極層4上にマスク層5が形成され、pMOS形成領域2bのマスク層5が除去され、nMOS形成領域2aのマスク層5aをマスクとしてpMOS形成領域2bの金属ゲート電極層4が除去され、マスク層5a上およびゲート絶縁膜3上に金属ゲート電極層6が形成され、pMOS形成領域2bをマスクするフォトレジストパターン7が形成され、フォトレジストパターン7をマスクとしてnMOS形成領域2aの金属ゲート電極層6が除去され、nMOS形成領域2aのマスク層5aが除去される。よって、nMOS形成領域2a上およびpMOS形成領域2b上の金属ゲート電極部形成のためのエッチング時にゲート絶縁膜3や半導体基板1表面への損傷を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの特性に適応した仕事関数をもつデュアルメタルゲートを備え、トランジスタ特性や信頼性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上に、ゲート絶縁膜3および金属層4を形成する。nMOS領域あるいはpMOS領域のいずれか、例えばpMOS領域にバリアメタル層5を形成した後に、全面に導電層6として例えばポリシリコンを成膜する。nMOS領域およびpMOS領域において、ゲート電極形状に加工した後に、熱処理を行う。これにより、nMOS領域では、金属層4と導電層6の合金層7からなる第2ゲート電極G2が形成される。pMOS領域では、バリアメタル層5により金属層4と導電層6との反応が抑制され、積層膜からなる第1ゲート電極G1となる。

(もっと読む)

1 - 14 / 14

[ Back to top ]