Fターム[4M104EE05]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極上 (625)

Fターム[4M104EE05]の下位に属するFターム

パシベーション膜 (200)

Fターム[4M104EE05]に分類される特許

201 - 220 / 425

半導体装置及びその製造方法

【課題】半導体装置のゲート加工用のマスク層に関する新たな提案を行う。

【解決手段】基板上方に第1乃至第3のマスク層を堆積し、第3のマスク層を加工し、第2のマスク層を加工し、L/S部内及びL/S部外の第2のマスク層をスリミングし、L/S部内及びL/S部外の第3のマスク層を剥離し、L/S部内及びL/S部外の第2のマスク層の側壁にスペーサを形成し、L/S部外の第2のマスク層がレジストで覆われた状態でL/S部内の第2のマスク層をエッチングすることで、L/S部外の第2のマスク層を残存させつつL/S部内の第2のマスク層を除去し、L/S部内及びL/S部外のスペーサとL/S部外の第2のマスク層とをマスクとして、第1のマスク層をエッチングにより加工し、当該エッチングにより、L/S部内及びL/S部外のスペーサとL/S部外の第2のマスク層とが薄膜化されることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】 III-V族窒化物半導体からなりバイアホール構造を有する半導体装置において、基板と半導体層との間に生じる漏れ電流を防止すると共にバイアホールの形成を容易にして高周波特性、高出力特性及び大電力特性を得られるようにする。

【解決手段】 半導体装置は、導電性基板11の上に形成された高抵抗のAlxGa1−xNからなるバッファ層12と、該バッファ層12の上に形成され、チャネル層を有するアンドープのGaN及びN型のAlyGa1−yNからなる素子形成層14と、素子形成層14の上に選択的に形成されたソース電極16、ドレイン電極17及びゲート電極15とを備えている。ソース電極16は、バッファ層12及び素子形成層14に設けられた貫通孔12aに充填されることにより導電性基板11と電気的に接続されている。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】

CMOS装置の製造工程におけるコンタクト不良発生を抑制する。

【解決手段】

半導体装置の製造方法は、(a)Si基板に、n型の第1の活性領域、p型の第2の活性領域を形成する工程と、(b)活性領域に、第1、第2のゲート電極構造、第1、第2のソース・ドレイン領域をそれぞれ形成する工程と、(c)第1のソース/ドレイン領域に、凹部を形成する工程と、(d)凹部にSi−Geを含むp型の圧縮応力を有する半導体エピタキシャル層を形成する工程と、(e)半導体基板上に引張応力を有する窒化シリコンのエッチストッパ膜、層間絶縁膜を形成する工程と、(f)層間絶縁膜、エッチストッパ膜を貫通して、コンタクト孔をエッチングする工程と、(g)半導体基板上方に酸素を含むプラズマを発生する工程と、(h)コンタクト孔に導電性プラグを埋め込む工程と、を有する。

(もっと読む)

半導体素子およびその製造方法

【課題】MOSトランジスタに十分な応力(ストレス)が加える半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100と、半導体基板100上に備えられたゲート電極114およびゲート電極114の側壁面に備えられたスペーサ116を含むゲート構造物110と、ゲート構造物110の両側の半導体基板100内に形成されたソース/ドレーン領域102と、ゲート構造物110上エッチング停止膜130と、を含み、エッチング停止膜130は、スペーサ116上の第1領域130_1およびゲート電極の上面上の第2領域130_2を含み、第1領域130_1の厚さは、第2領域130_2の厚さの85%以下である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】SACプロセスによるコンタクト形成において、ゲート電極とコンタクトとのショートを生じにくくし、歩留まりの向上を図ること。

【解決手段】シリコン基板1に直交する面内において、ゲート電極3,4,5のうちゲートマスク6,7に近い第2電極部(窒化タングステン)4及び第3電極部(タングステン)5をゲートマスク6,7よりも幅小となるようにし、ゲート電極3,4,5とセルコンタクトプラグ15との間のショートマージンを増加させた。

(もっと読む)

半導体装置及びその製造方法

半導体装置は、半導体基板上に形成された絶縁膜と、絶縁膜中に形成され、銅又は銅合金からなる埋め込み配線とを備え、絶縁膜と埋め込み配線との間に、白金族元素、又は白金族元素の合金からなるバリアメタル層を有しており、バリアメタル層は、相対的にバリア性が高くなる非晶質度を有する非晶質構造を一部に含んでいる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】圧縮応力を有する絶縁膜と引っ張り応力を有する絶縁膜とが互いに応力を相殺することがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタと、第1の応力絶縁膜20Aと、第1の絶縁膜21Aと、第2の絶縁膜21Bとを備えている。第1のトランジスタは、半導体基板10の第1の活性領域11Aに形成され、第1のゲート電極14Aを有する。第1の応力絶縁膜20Aは、第1のゲート電極14Aを覆うように形成され、第1のトランジスタのチャネル領域に応力を加える。第1の絶縁膜21Aは、第1の応力絶縁膜20Aの上に接して形成され、上面が平坦化されている。第2の絶縁膜21Bは、第1の絶縁膜21Aの上に接して形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の配置間隔を小さくしても所望のゲート電極のパターンを安定して形成することができ、特性・信頼性の劣化を防ぐことができる半導体装置の製造方法を得る。

【解決手段】半導体基板11上に複数の凹部14を形成する。複数の凹部14の内壁を覆うように半導体基板11上に絶縁膜15を形成する。絶縁膜15上にレジスト16を形成し、露光及び現像によりレジスト16に、複数の凹部14上において、対応する凹部14よりも幅が狭い複数の開口13をそれぞれ形成する。レジスト16をマスクとして絶縁膜15を異方性エッチングして凹部14の底面の一部を露出させる。露出した凹部14の底面及び絶縁膜15上にWSiN膜21及びAu膜22(導体膜)を形成する。複数の凹部14以外の領域においてWSiN膜21及びAu膜22を除去して、それぞれの凹部14内に残されたWSiN膜21及びAu膜22によりゲート電極23を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

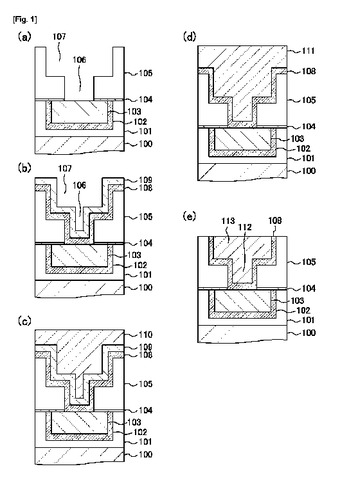

酸化物半導体を用いた薄膜トランジスタの製造方法

【課題】酸化物半導体を用いたボトムゲート型薄膜トランジスタにおいて、ソース電極、ドレイン電極と酸化物半導体層のオーミックコンタクトが良好な薄膜トランジスタを製造する方法を提供する。

【解決手段】基板1上に、ゲート電極2、ゲート絶縁膜3、酸化物半導体層4、第1の絶縁膜5、ソース電極7、ドレイン電極8、第2の絶縁膜9を少なくとも有する薄膜トランジスタの製造方法において、酸化物半導体層4の上に第1の絶縁膜5を酸化性ガスが含まれない雰囲気で形成することで、酸化物半導体層4が低抵抗化されたコンタクト領域6とする工程と、酸化物半導体層4のチャネル領域を含む面の上に第2の絶縁膜9を酸化性ガスが含まれる雰囲気で形成することで、チャネル領域を高抵抗化する工程とを実施する。

(もっと読む)

化合物半導体装置とその製造方法

【課題】ゲート電極の近傍での耐圧が高められた化合物半導体装置とその製造方法を提供すること。

【解決手段】SiC基板20と、SiC基板20の上に形成された電子走行層21と、電子走行層21の上に形成された電子供給層23と、電子供給層23の上に互いに間隔をおいて形成されたソース電極27a及びドレイン電極27bと、ソース電極27aとドレイン電極27bの間の電子供給層23上に形成され、SiC基板20に向かって狭径となる開口29bを備えた保護絶縁膜30と、開口29b内の電子供給層23上に形成されたゲート電極32とを有する化合物半導体装置による。

(もっと読む)

半導体装置の製造方法

【課題】トリミングを用いず、プロセスの大幅な変更や工程数を大きく増加させずに、高精度に微細化してゲート電極または配線を形成できる半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10のチャネル形成領域上にゲート絶縁膜12を形成し、その上層に第1導電層20を形成し、第1導電層にゲート電極のパターンに対応し第1の幅20wを有する第1凹部20tを形成し、その内壁を被覆して、第1の幅より狭い第2の幅31wの第2凹部31tを有する第2導電層31を形成し、第2凹部を埋め込んでマスク層32を形成し、第1凹部の外部における第2導電層及びマスク層を除去し、第1凹部に残されたマスク層をマスクとして第2導電層及び第1導電層をパターン加工してゲート電極Gを形成し、ゲート電極Gの両側部における半導体基板中にソース・ドレイン領域13を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】低屈折率の窒化シリコン膜を用いた場合であっても、電流コラプスを効果的に低減すること。

【解決手段】本発明は、GaN系半導体層16の上に屈折率が2.1以上2.2未満の窒化シリコン膜18を形成する工程と、窒化シリコン膜18の開口にオーミック電極20、22を形成する工程と、オーミック電極20、22を熱処理する工程と、を有する半導体装置の製造方法である。本発明によれば、屈折率が2.1以上の窒化シリコン膜18を形成した状態で、オーミック電極の熱処理を行うことにより、電流コラプスを抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜の開口に形成する電極の被覆性を向上させること。

【解決手段】本発明は、化合物半導体層16の上に第1絶縁膜20を形成する工程と、第1絶縁膜20を熱処理する工程と、第1絶縁膜20上に第2絶縁膜22を形成する工程と、第2絶縁膜22及び第1絶縁膜20を同一マスク40を用い選択的にエッチングし化合物半導体層16が露出する開口部44、46を形成する工程と、開口部44、46の内壁に接する電極を形成する工程と、を有することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】 n型FET及びp型FETのドレイン電流の増加(電流駆動能力の向上)を図る。

【解決手段】 半導体基板に形成されたn型及びp型FETを有する半導体装置の製造であって、前記p型FETのゲート電極と前記半導体基板の素子分離領域との間の半導体領域を絶縁膜で覆った状態で、前記n型及びp型FET上にこれらのゲート電極を覆うようにして、前記n型FETのチャネル形成領域に引っ張り応力を発生させる第1の絶縁膜を形成する(a)工程と、エッチング処理を施して、前記p型FET上の前記第1の絶縁膜を選択的に除去する(b)工程と、前記n型及びp型FET上にこれらのゲート電極を覆うようにして、前記p型FETのチャネル形成領域に圧縮応力を発生させる第2の絶縁膜を形成する(c)工程と、前記n型FET上の前記第2の絶縁膜を選択的に除去する(d)工程とを有する。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタシート及び有機薄膜トランジスタの製造方法

【課題】シロキサン化合物を含有する保護層を設けることで、トランジスタ性能が安定している有機薄膜トランジスタを提供し、且つ、前記保護層の形成時に、有機半導体層にダメージを与えない有機薄膜トランジスタの製造方法を提供する。

【解決手段】支持体、ゲート電極、ゲート絶縁層、有機半導体層、ソース電極、ドレイン電極および少なくとも1つの別種の電極を有する有機薄膜トランジスタにおいて、

構成層として保護層を有し、該保護層がシロキサン化合物を含有することを特徴とする有機薄膜トランジスタ。

(もっと読む)

トランジスタ、集積回路および集積回路形成方法

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

有機薄膜トランジスタ

【課題】 有機物を利用して薄膜トランジスタを製造しようとする場合、有機半導体薄膜のキャリア移動度が小さく、実用的な動作速度を有する有機薄膜トランジスタは得られなかった。この課題を解決するために縦型有機薄膜トランジスタが検討され、高速動作が期待されているが、十分な電流オンオフ比が得られないという課題がある。

【解決手段】 本発明の有機薄膜トランジスタは、基板上に第1の電極(ソース又はドレイン)、第1の有機半導体層、第3の電極(ゲート)、第2の有機半導体層、第2の電極(ドレイン又はソース)の順に積層した構造を有する。第3の電極の膜厚を80nm以上の厚膜とする。第3の電極の膜厚を厚くすることで、大きなオンオフ比を有する有機薄膜トランジスタが得られる。

(もっと読む)

ストレッサを有する半導体素子及びその製法

半導体素子(10)を半導体層(16)に形成する。ゲート誘電体(20)を前記半導体層(16)の上側表面に形成する。ゲート積層構造(18)を前記ゲート誘電体(20)の上に形成する。側壁スペーサ(24)を前記ゲート積層構造(18)の周りに形成する。前記側壁スペーサ(24)をマスクとして使用して、イオン注入を行なってディープソース/ドレイン領域(28,30)を前記半導体層に形成する。シリコンカーボン領域(32,36,34)を前記ディープソース/ドレイン領域(28,30)の上に、そして前記ゲート積層構造の上側表面に形成する。前記シリコンカーボン領域(32,36,34)をニッケルでシリサイド化する。  (もっと読む)

(もっと読む)

201 - 220 / 425

[ Back to top ]